Flash memory chip and testing method thereof

A technology of flash memory chips and testing methods, applied in information storage, static memory, read-only memory, etc., can solve the problems of increasing the time of parallel testing, etc., and achieve the effect of reducing testing time and reducing testing waiting time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

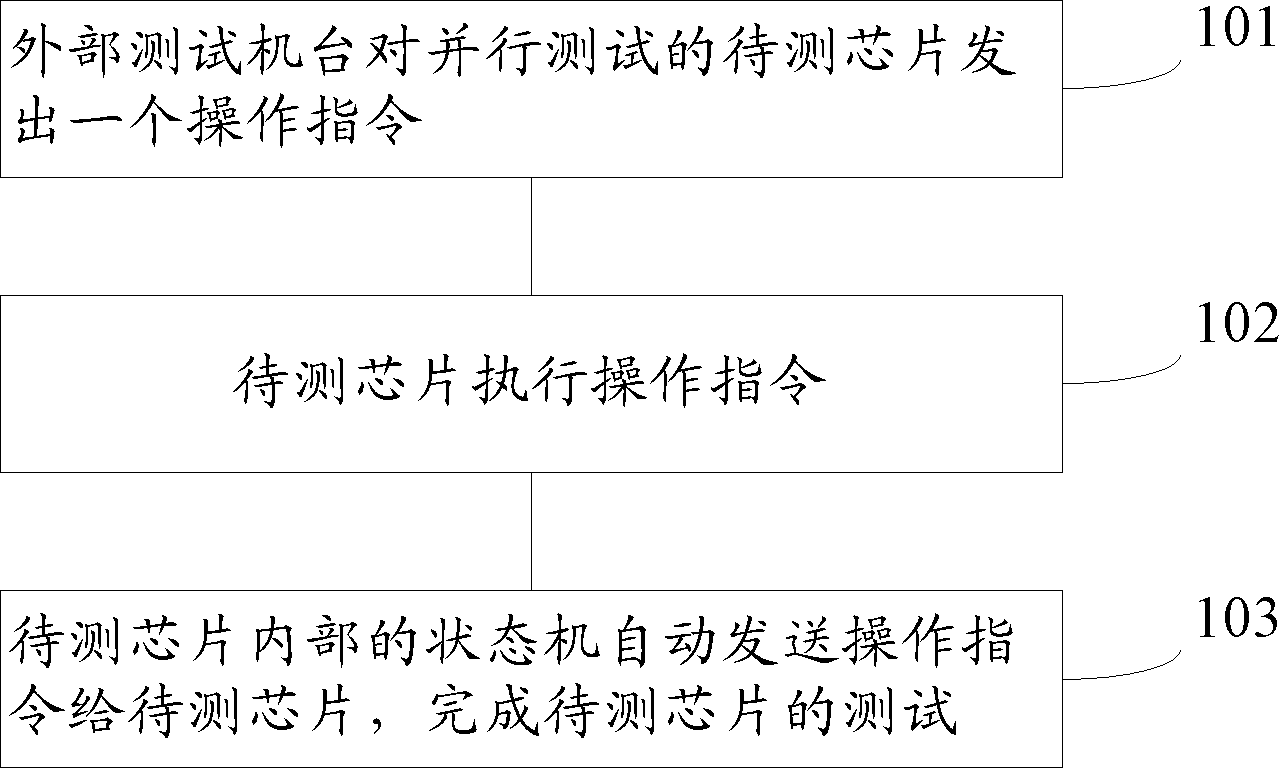

[0024] Please refer to figure 1 , showing a first embodiment of a method for testing a flash memory chip of the present invention, comprising the following steps:

[0025] Step 101, the external testing machine sends an operation instruction to the chips under test for parallel testing.

[0026] The external test machine sends an operation command to all the chips to be tested that need to be tested in parallel. The operation command here can be an operation command for logical function testing. For example, the external test machine operates the CKB of the chip to be tested: to the storage unit (cell ) erase operation instructions, program and verify operation instructions on memory cells that have been erased, and the like.

[0027] Step 102, the chip under test executes an operation instruction.

[0028] All the chips under test perform operations according to the operation instructions of the external test machine.

[0029] Step 103 , the state machine inside the chip t...

Embodiment 2

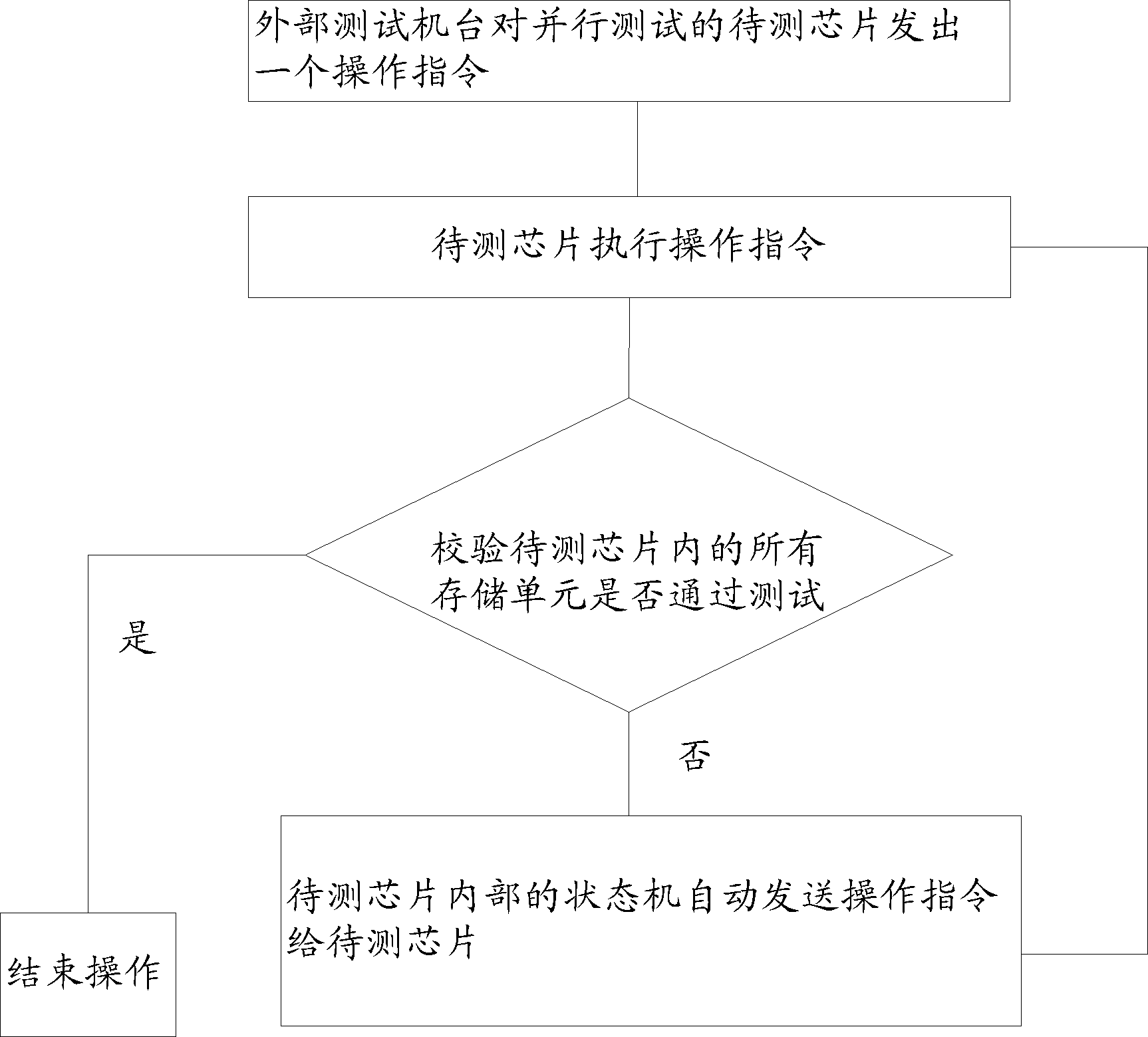

[0031] refer to figure 2 , showing a second embodiment of a method for testing a flash memory chip of the present invention, comprising the following steps:

[0032] In step 201, the external testing machine sends an operation command to the chips under test for parallel testing.

[0033] In step 202, the chip under test executes an operation instruction.

[0034] Step 203, check whether all storage units in the chip under test pass the test, if so, proceed to step 204; otherwise, the state machine inside the chip under test automatically sends an operation command to the chip under test, and returns to step 202.

[0035] Step 204, the state machine returns the test pass information to the external test machine.

[0036] By judging the execution results of the chip to be tested, whether all the storage units in the chip have completed the operation command, if yes, no operation is required, if not, it is necessary to issue an operation command to the chip to be tested, and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More