Method for predicting voltage value of full-open defect of interconnecting wire of deep sub-micron integrated circuit

A deep submicron, integrated circuit technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as broken metal lines or through holes, missing contact holes or through holes, and waste of test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054] The present invention is described in further detail below in conjunction with accompanying drawing:

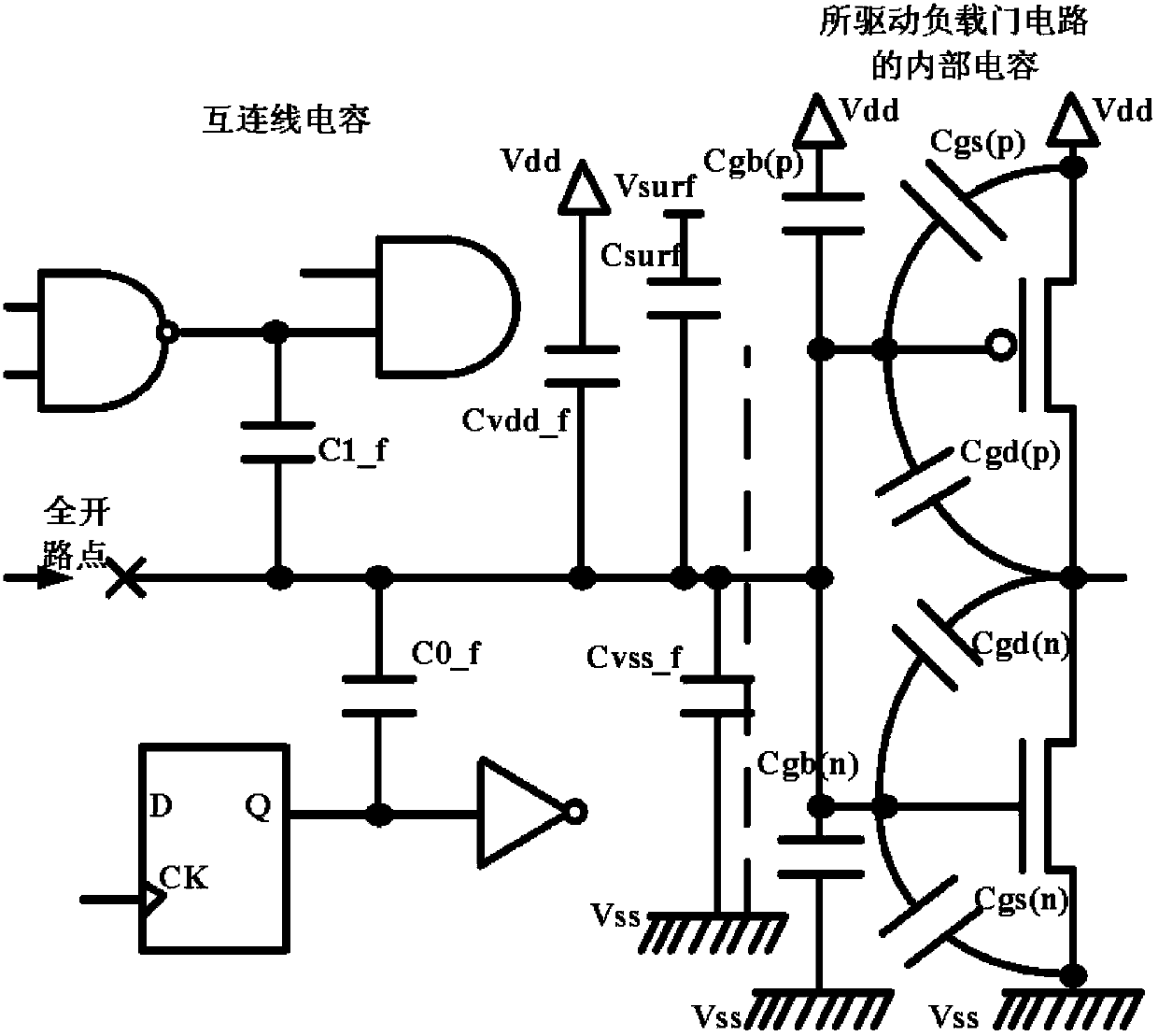

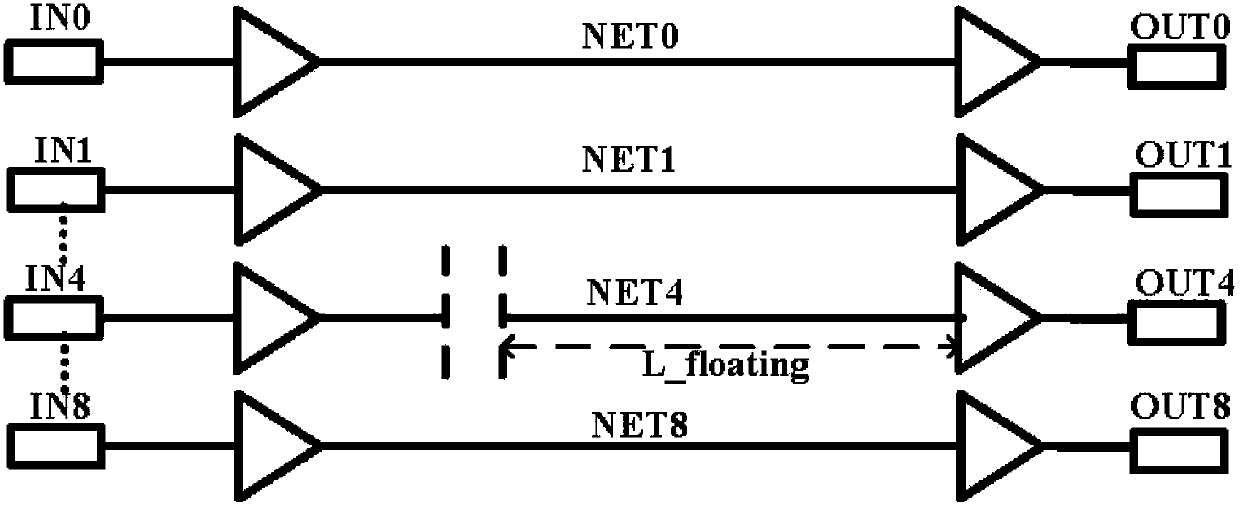

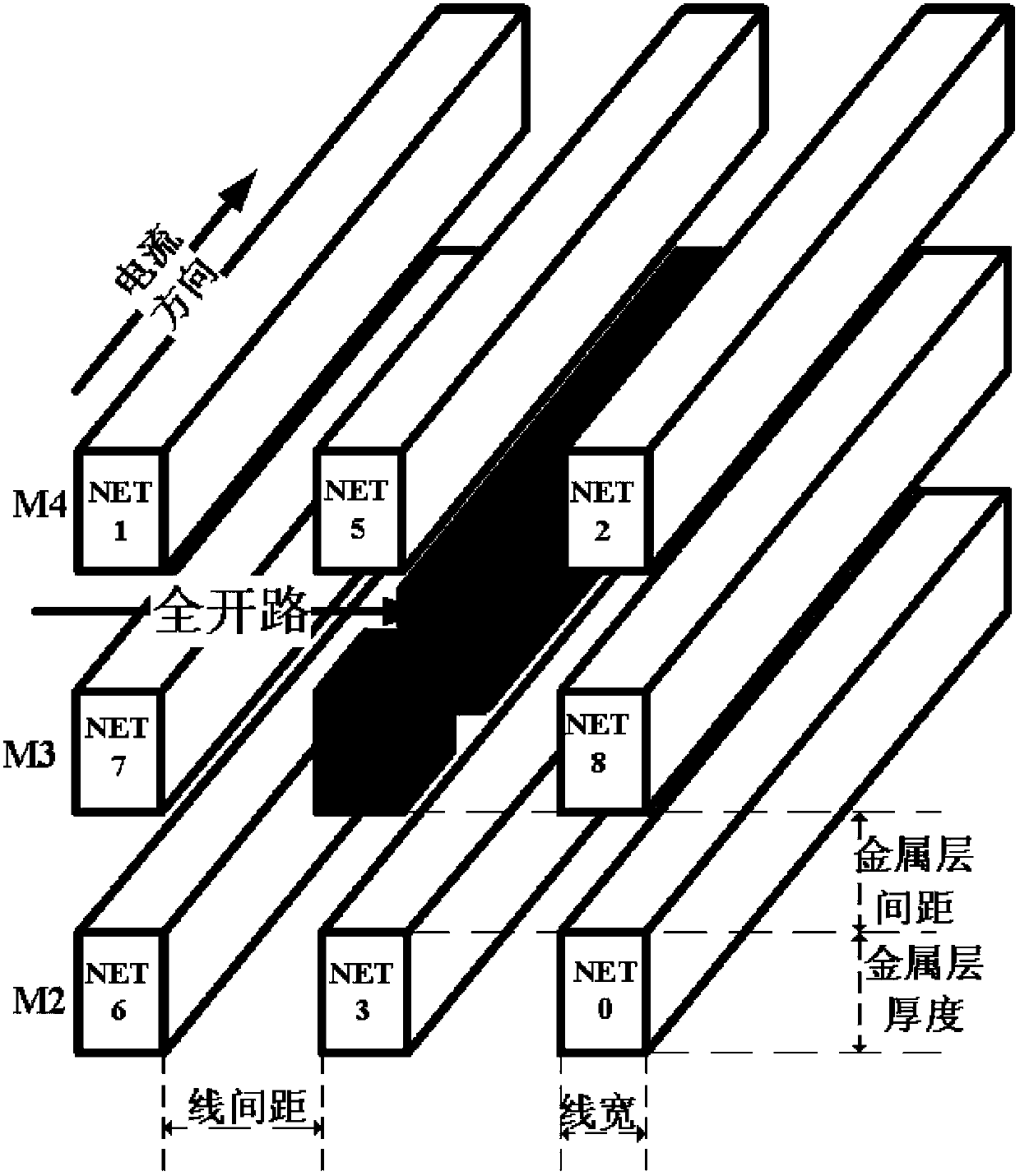

[0055] see Figure 1-11 , due to the deep submicron and ultra-deep submicron process conditions, there is a large coupling capacitance between other signal lines and open metal lines adjacent to the physical position of the open defect point in the integrated circuit layout (Layout). Under the influence of the coupling capacitance, when the logic states of other adjacent signal lines change, the voltage at the open-circuit defect also changes correspondingly. The voltage prediction method proposed in the present invention is to establish the relationship between the voltage of the open circuit point and the coupling capacitance, and use the coupling capacitance of the adjacent signal line to represent the voltage value and voltage logic of the circuit defect point.

[0056] The invention is based on the TSMC (TSMC) 40nm digital CMOS technology to simulate and analyze ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More