A key detection circuit and detection method

A detection circuit and detection method technology, which is applied in the key field, can solve the problems of complex circuit design, poor practicability, and high production cost, and achieve the effects of reducing production cost, strong applicability, and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

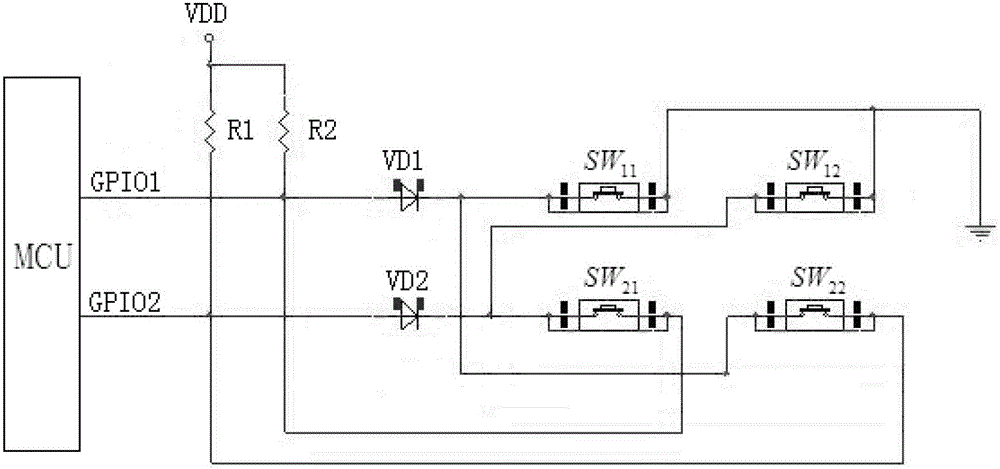

[0046] figure 1 It shows a circuit diagram in which the CPU sets two GPIO interfaces to detect 4 keys. Such as figure 1 as shown,

[0047] The button detection circuit includes the central processing unit MCU, 4 buttons SW 11 、SW 12 、SW 21 、SW 22 and power supply, the central processing unit MCU is set with GPIO 1 , GPIO 2 Two GPIO interfaces, GPIO 1 , GPIO 2 respectively through pull-up resistors R 1 , R 2 Connect to power supply. Among them GPIO 1 , GPIO 2 Constitute 4 detection circuits.

[0048] When GPIO 1 , GPIO 2 When both are input interfaces: GPIO 1 , GPIO 2 Respectively via the button SW 11 、SW 12 Grounded to form 2 detection lines;

[0049] When GPIO 1 For the output interface, GPIO 2 When it is an input interface: GPIO 2 by SW 21 with GPIO 1 Composition detection SW 21 detection line;

[0050] When GPIO 2 For the output interface, GPIO 1 When it is an input interface: GPIO 1 by SW 22 with GPIO 2 Composition detection SW 22 detectio...

Embodiment 2

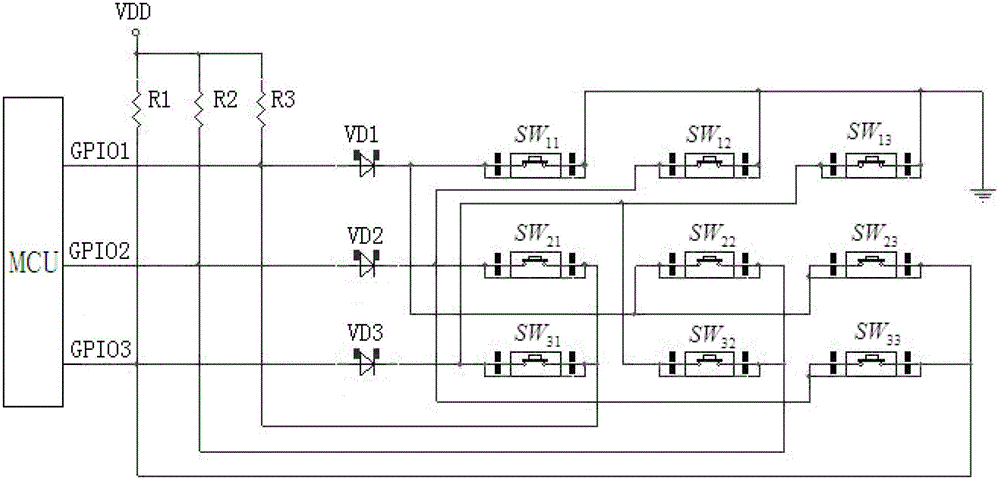

[0059] figure 2 It shows a circuit diagram in which the central processing unit sets three GPIO interfaces to realize detection of 9 keys. Such as figure 2 As shown, the button detection circuit includes a central processing unit MCU, 9 buttons and a power supply, and the central processing unit MCU is provided with GPIO 1 , GPIO 2 , GPIO 3 Three GPIO interfaces, GPIO 1 , GPIO 2 , GPIO 3 respectively through pull-up resistors R 1 , R 2 , R 3 Connect to power supply. Among them GPIO 1 , GPIO 2 , GPIO 3 Three GPIO interfaces form nine detection circuits.

[0060] When all three GPIOs are input interfaces: GPIO 1 , GPIO 2 , GPIO 3 Respectively via the button SW 11 、SW 12 、SW 13 Grounded to form 3 detection lines;

[0061] When GPIO 1 For the output interface, GPIO 2 , GPIO 3 When it is an input interface: GPIO 2 by SW 21 with GPIO 1 Composition detection SW 21 detection line; GPIO 3 by SW 31 with GPIO 1 Composition detection SW 31 detection line; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More