Multiprocessor inter-core transmission method for avoiding data back writing during read-miss

A multi-processor core and transmission method technology, which is applied in the direction of electrical digital data processing, instruments, memory systems, etc., can solve the problem of invalid cache copy content, achieve the effect of reducing the number of times and improving system performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described below in conjunction with the accompanying drawings.

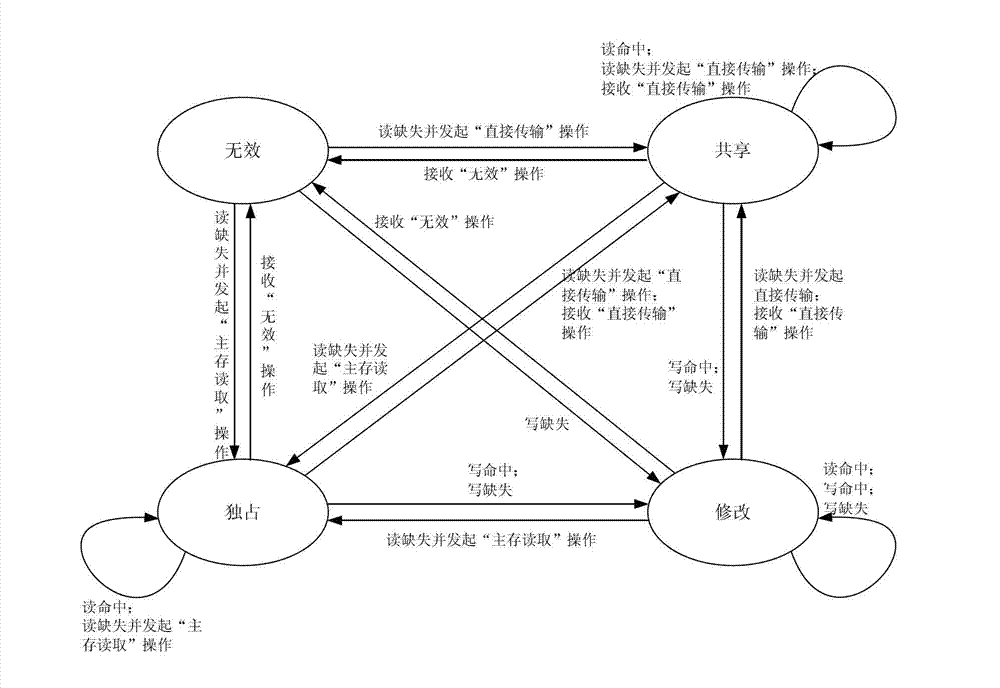

[0027] refer to figure 1 , a multi-processor inter-core transfer method that avoids data write-back when read misses occur. When read misses occur, data that supports cache valid dirty copies (cache valid copies different from main memory data) is directly transferred between processors , without first writing the data of the valid dirty copy of the cache back to the main memory; it supports a main memory block to have multiple valid dirty copies, and multiple valid dirty copies are written back to the main memory at most once; a kind of MESI protocol is adopted as a cache coherency protocol.

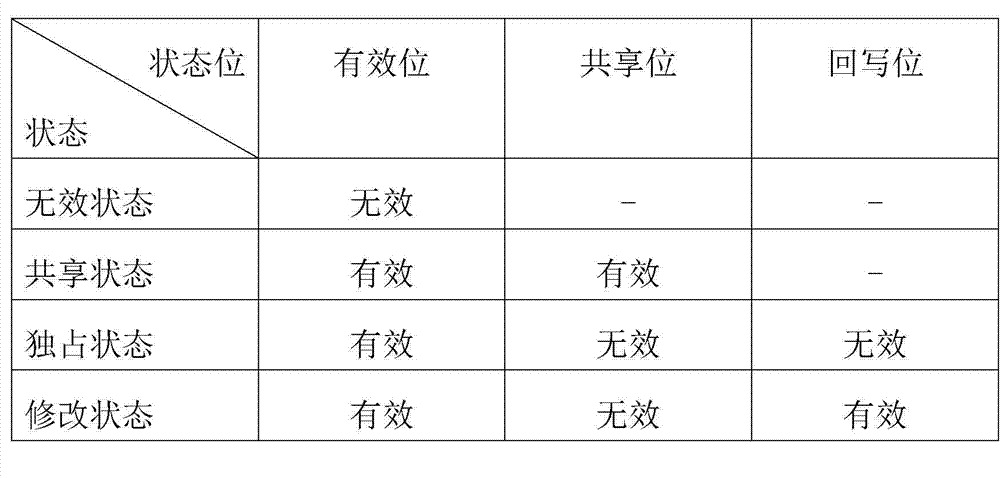

[0028] A MESI-like protocol is adopted as the cache coherency protocol. This protocol is suitable for caches with a write-return strategy. In this protocol, each cache copy has four states: invalid state, shared state, exclusive state, and modified state. The states are define...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More