Manufacturing method for super junction metal oxide semiconductor field effect transistor (MOSFET)

A manufacturing method and technology of source region, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., to achieve the effect of reducing production cost, increasing difficulty, and reducing quantity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The manufacturing steps of device of the present invention are:

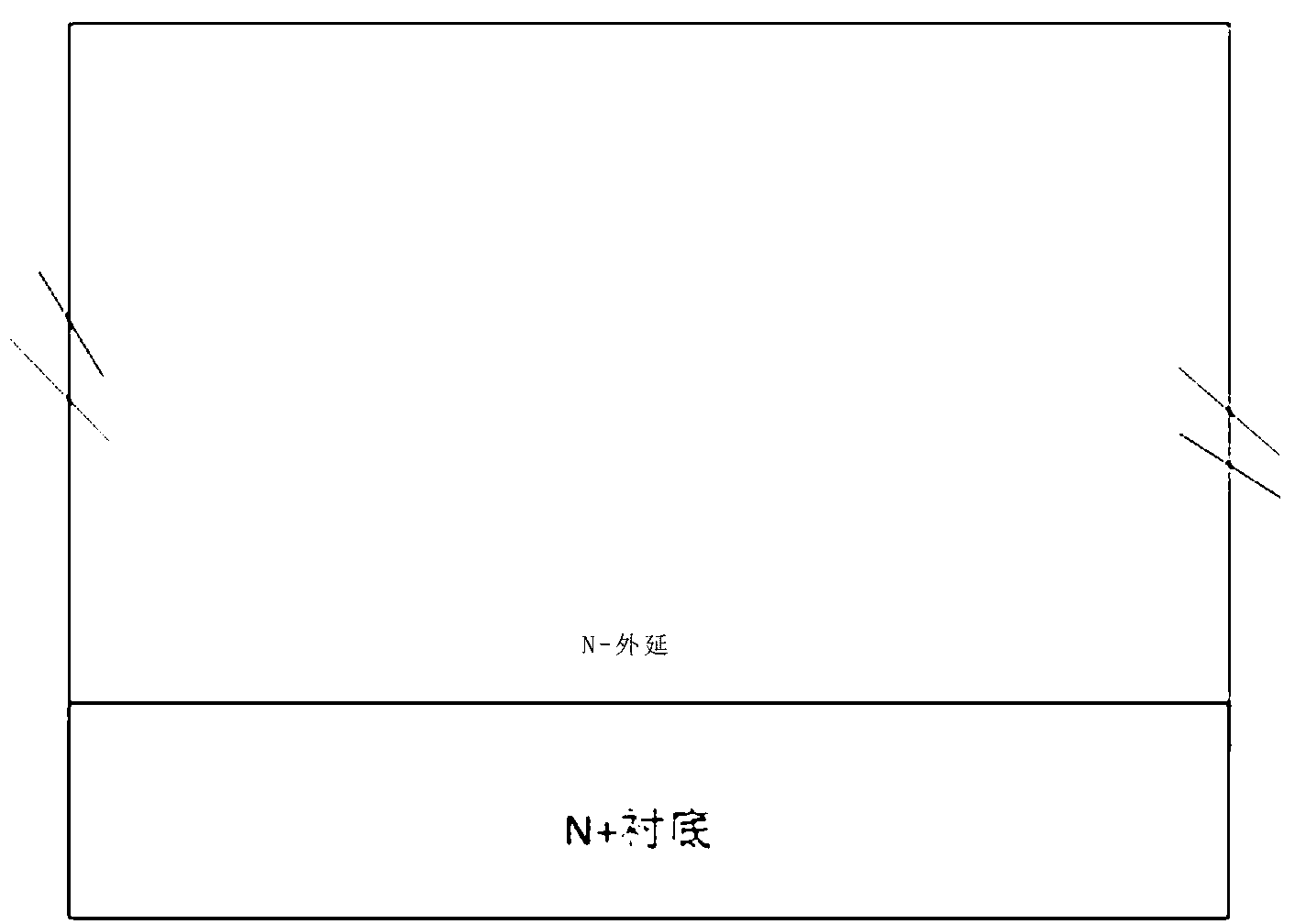

[0033] Step 1: provide n-type heavily doped n+ substrate, and form n-type epitaxial layer on n+ substrate, as figure 1 Show.

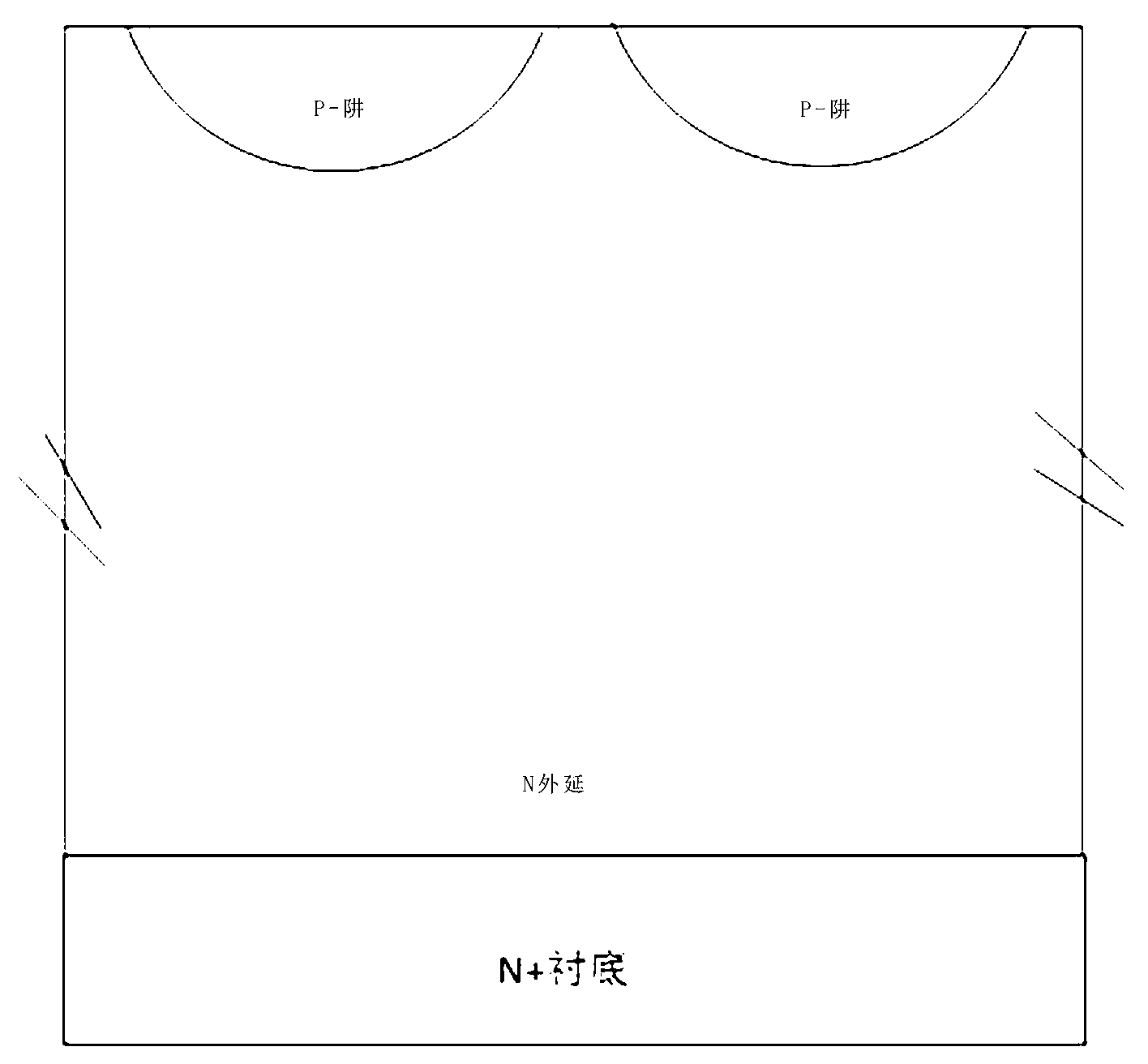

[0034] Step 2: Define the implantation region of the p-body by photolithography, perform p-type impurity implantation, and form a p-well region by thermal process push well, such as figure 2 Show.

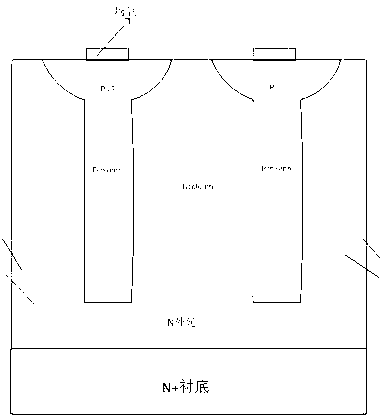

[0035] Step 3: Define the area for forming p-columm by photolithography, and form p-column by etching and epitaxial filling to form a composite buffer layer, such as image 3 Show.

[0036] Step 4: growing a field oxide layer on the silicon wafer, Figure 4 Show.

[0037] Step 5: Define the device cell area through the photolithographic field oxide layer, and reserve part of the field oxygen as a barrier layer for n+ implantation in the source region, such as Figure 5 Show.

[0038] Step 6: growing a gate oxide layer, depositing polysilicon, and defining the region of the pol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More