Three-dimensional chip-to-wafer integration

A technology of grain and connection, which is applied in the direction of semiconductor/solid-state device components, semiconductor devices, printed circuits, etc., and can solve problems such as limitations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

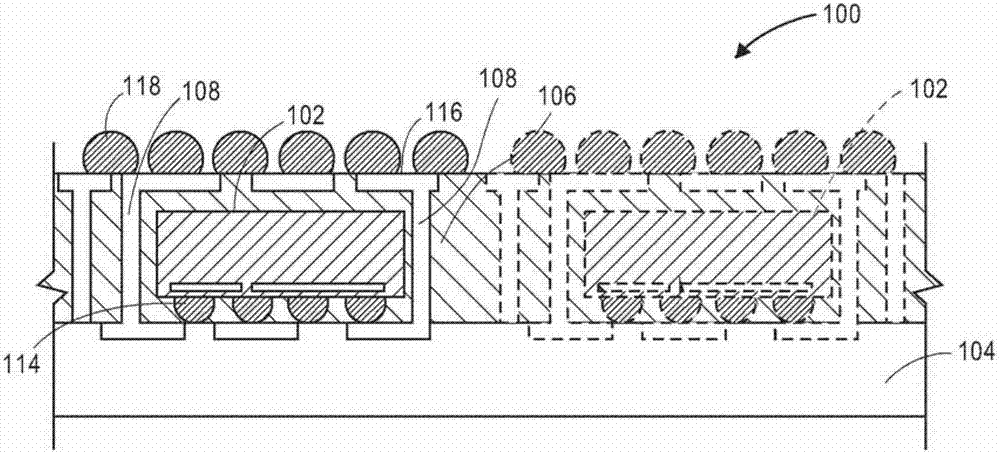

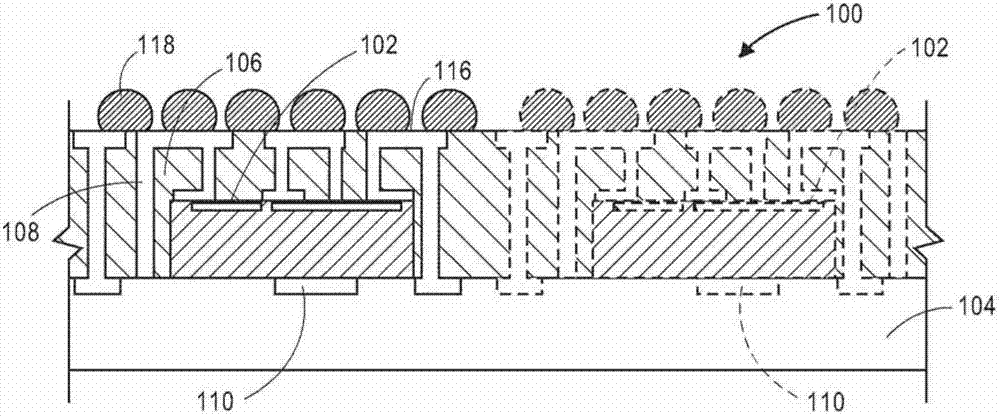

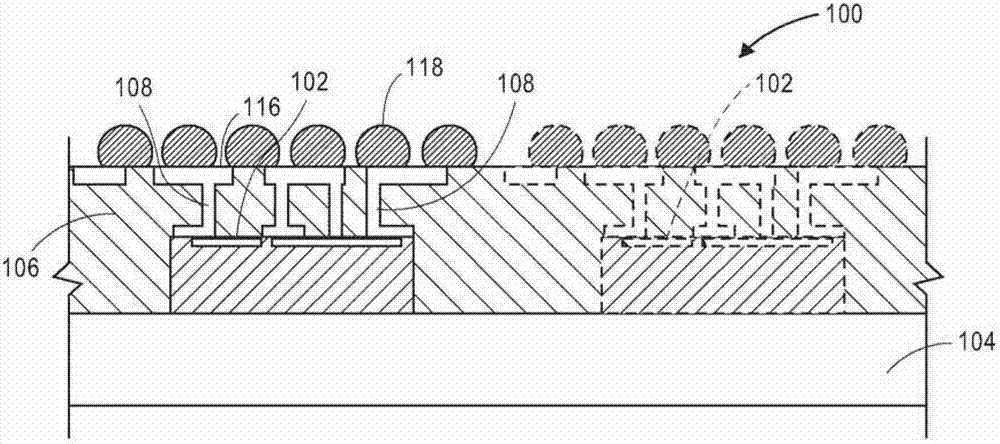

[0014] overview

[0015] 3D ICs can be constructed using two or more layers of electronic components integrated into a single IC chip. Electronic components can be stacked to form a single circuit. In some cases, vertical TSVs are used to connect to electronic components of 3D ICs. However, when two or more die are stacked on top of each other, this may require redesigning each die stacked below the other to connect to the underlying die via TSVs. In other cases, through-mold solder connections, such as TMVs, use solder balls to interconnect between the PCB and the top side of the molding compound. However, this type of configuration limits the minimum possible spacing between connections to the PCB as determined by the size of the solder balls and spacing requirements.

[0016] Other types of 3D ICs can be constructed using a molded epoxy wafer on which two or more die are arranged. However, because semiconductor die, such as silicon wafers, have a different coefficient o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More