Patents

Literature

46 results about "Wafer-scale integration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Wafer-scale integration, WSI for short, is a rarely used system of building very-large integrated circuit networks that use an entire silicon wafer to produce a single "super-chip". Combining large size and reduced packaging, WSI was expected to lead to dramatically reduced costs for some systems, notably massively parallel supercomputers. The name is taken from the term very-large-scale integration, the current state of the art when WSI was being developed.

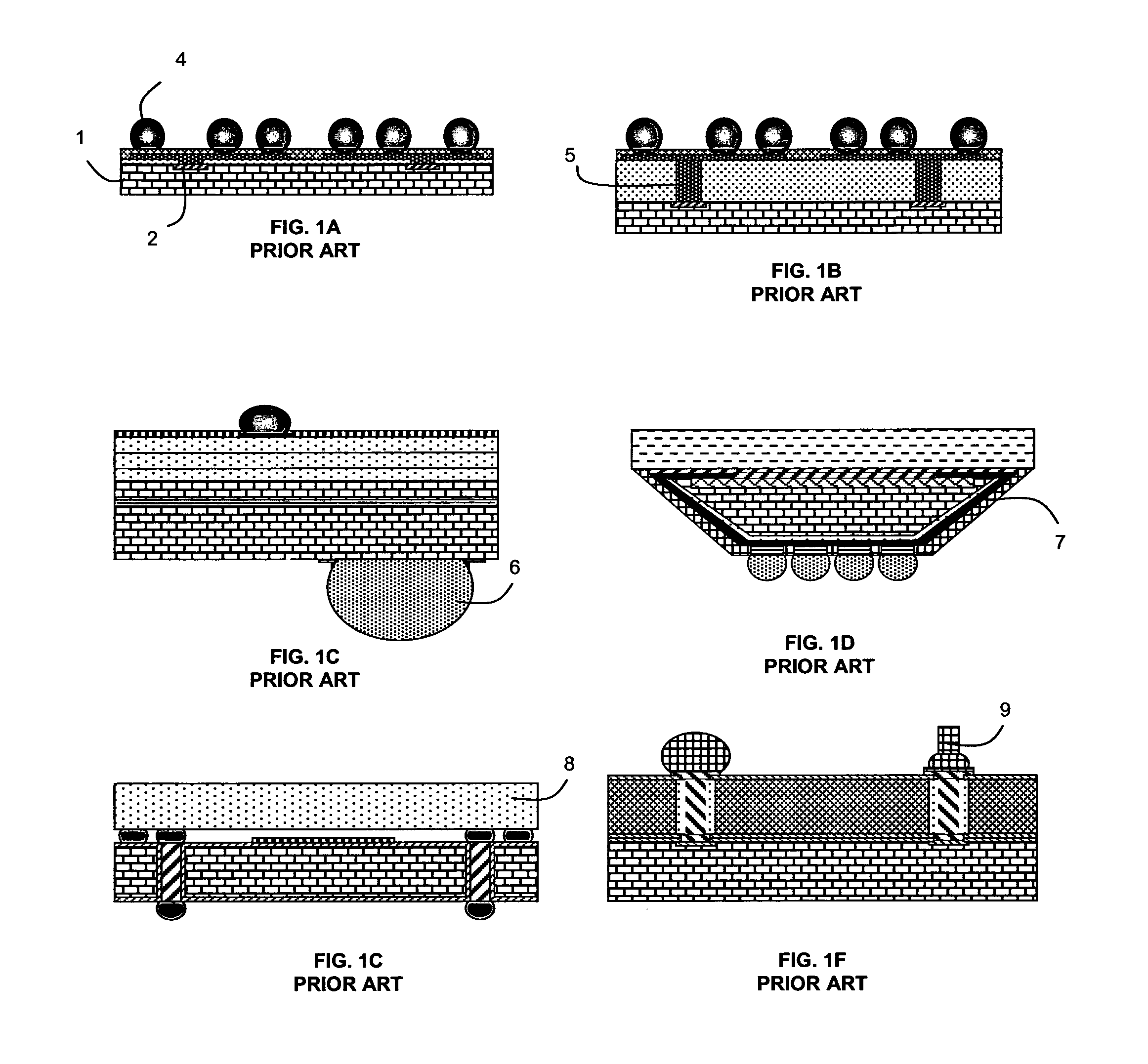

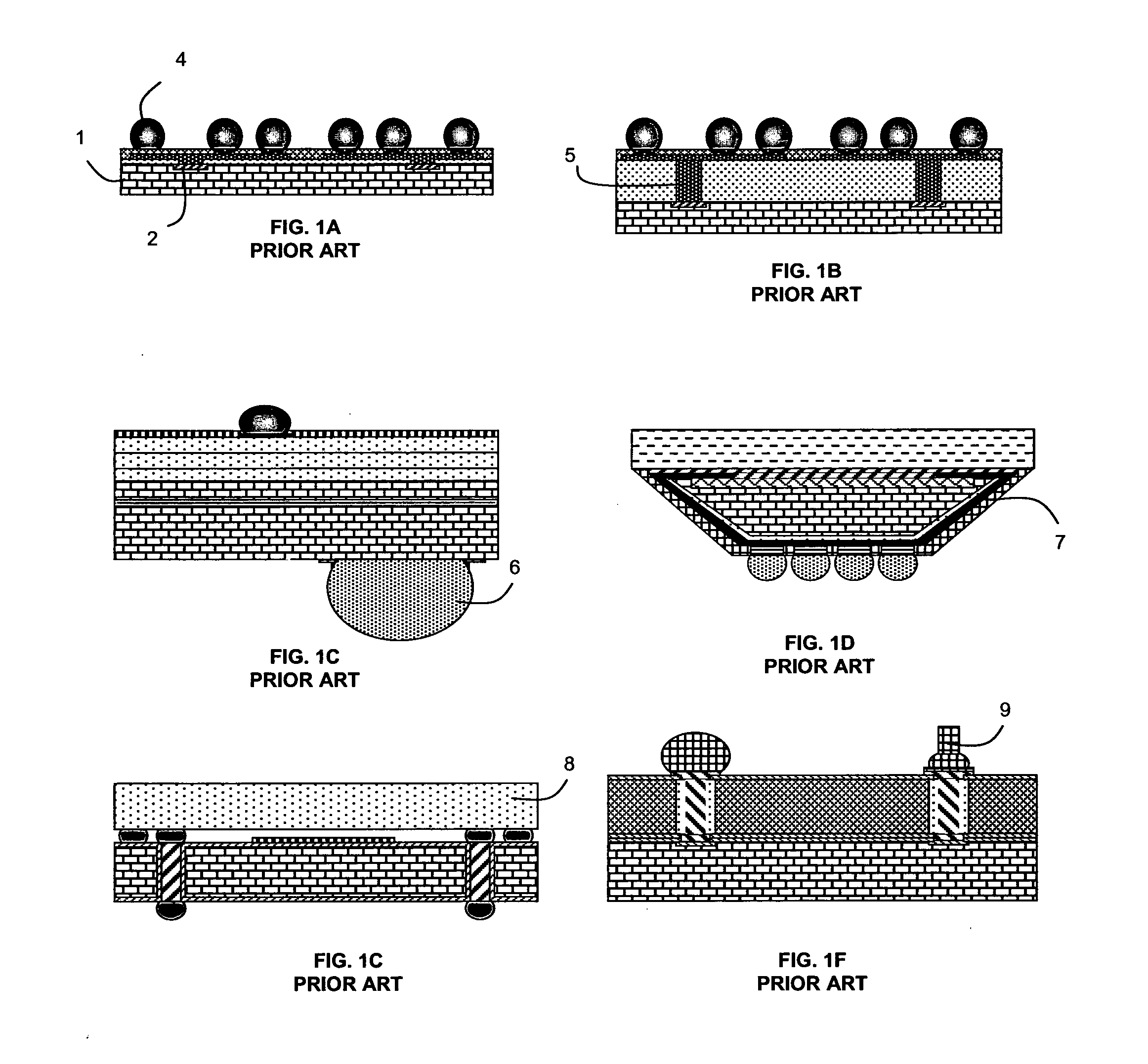

Hermetic wafer scale integrated circuit structure

InactiveUS6982475B1Prevent surfaceDamaged and destroyedSemiconductor/solid-state device detailsSolid-state devicesScale structureHermetic seal

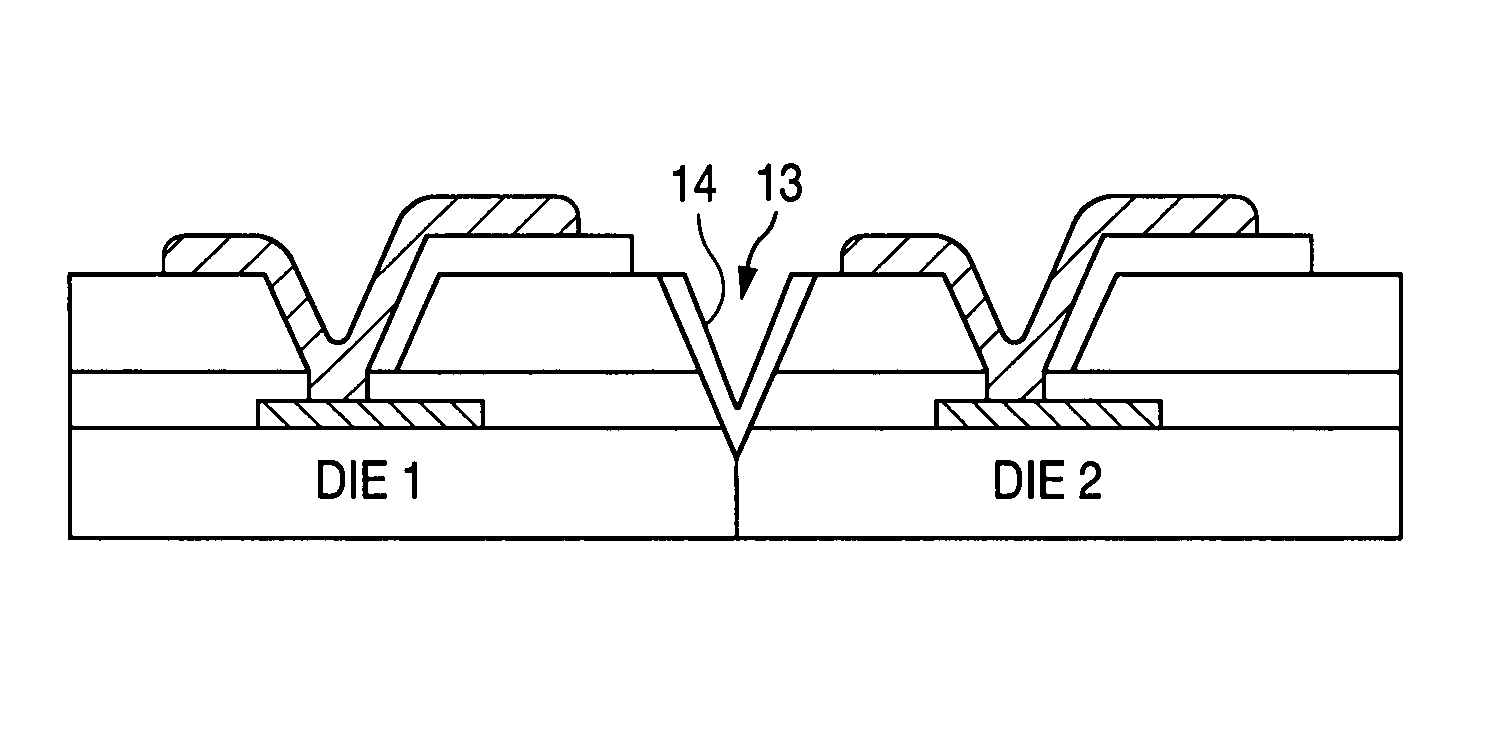

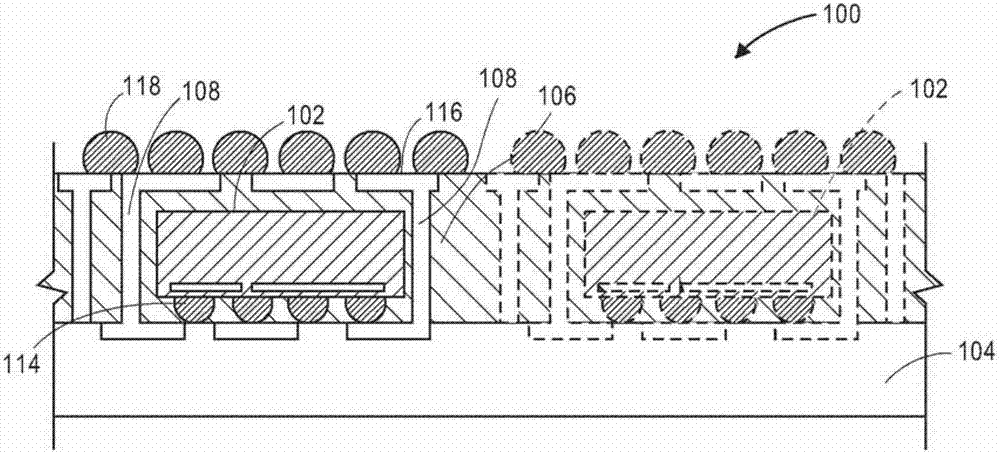

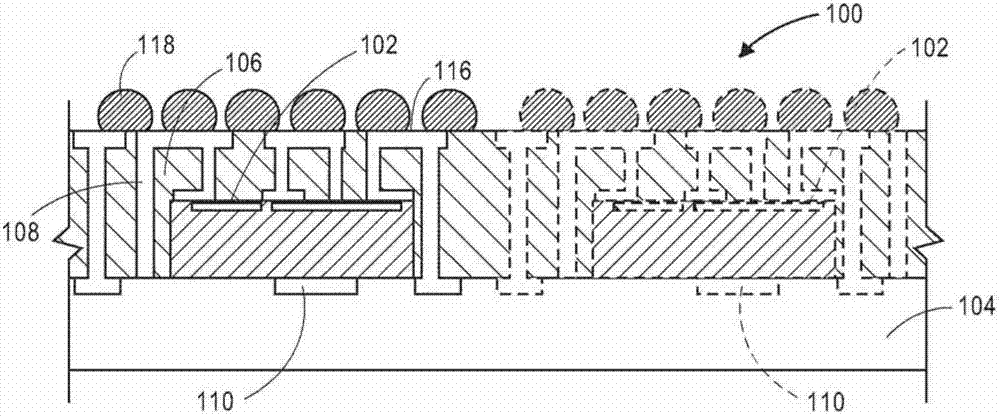

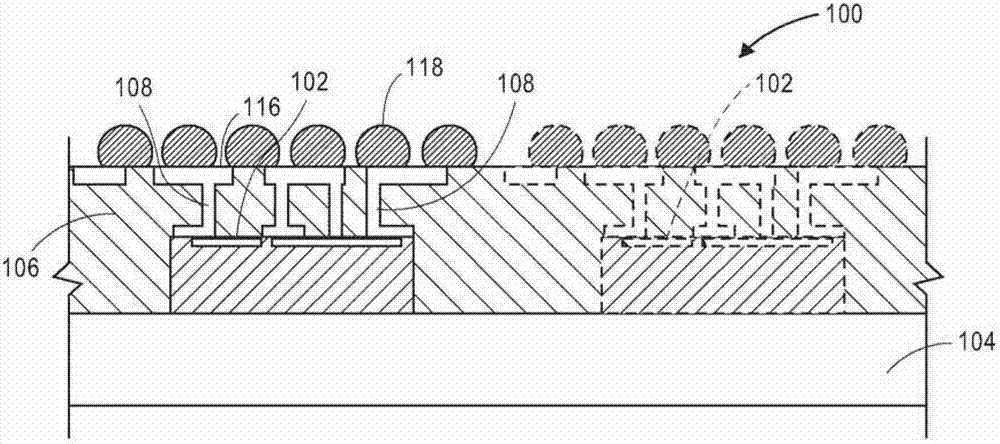

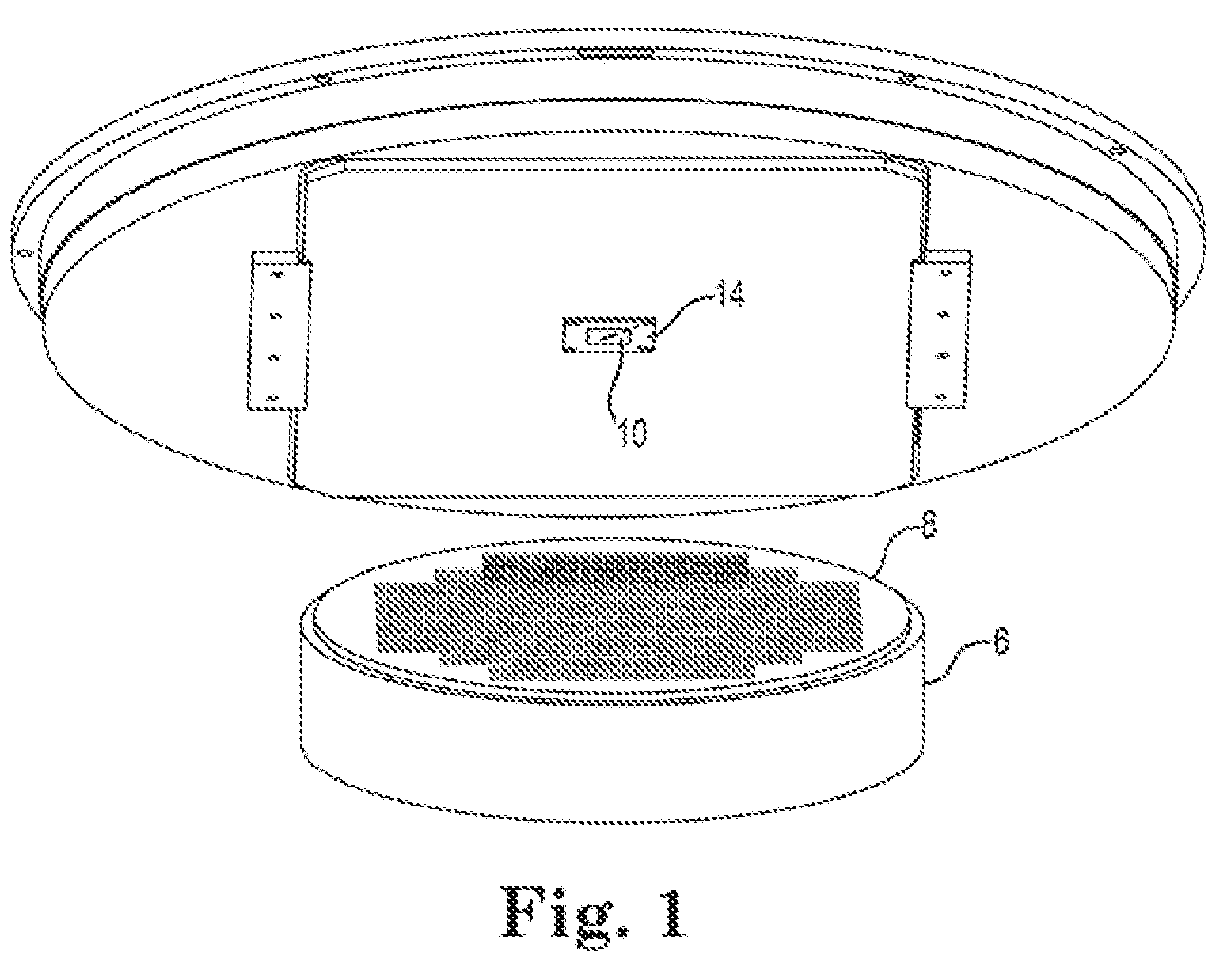

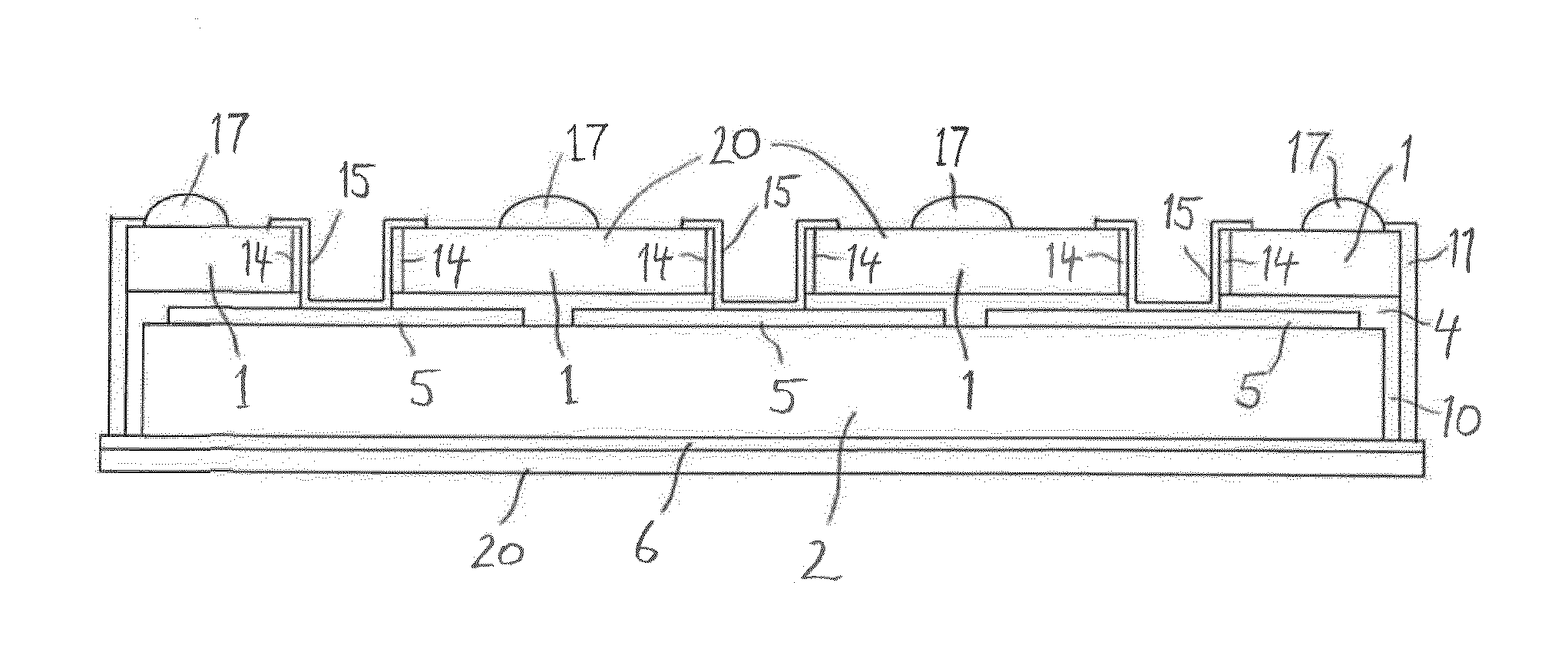

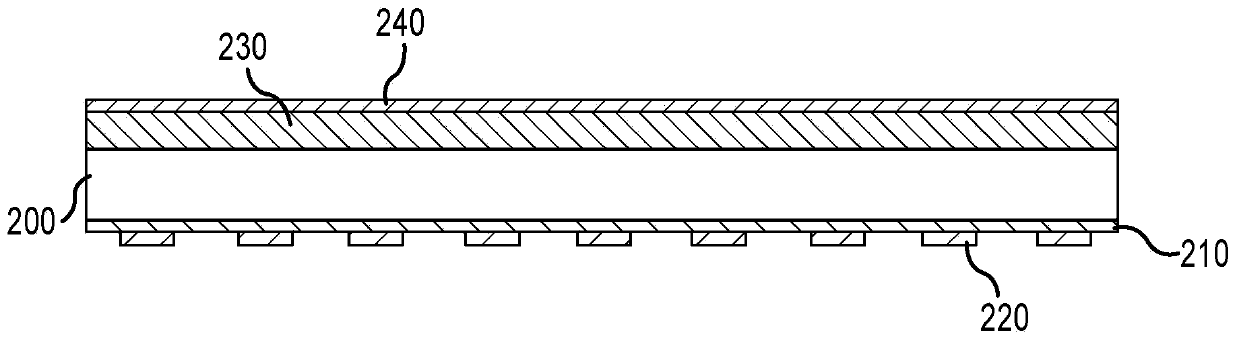

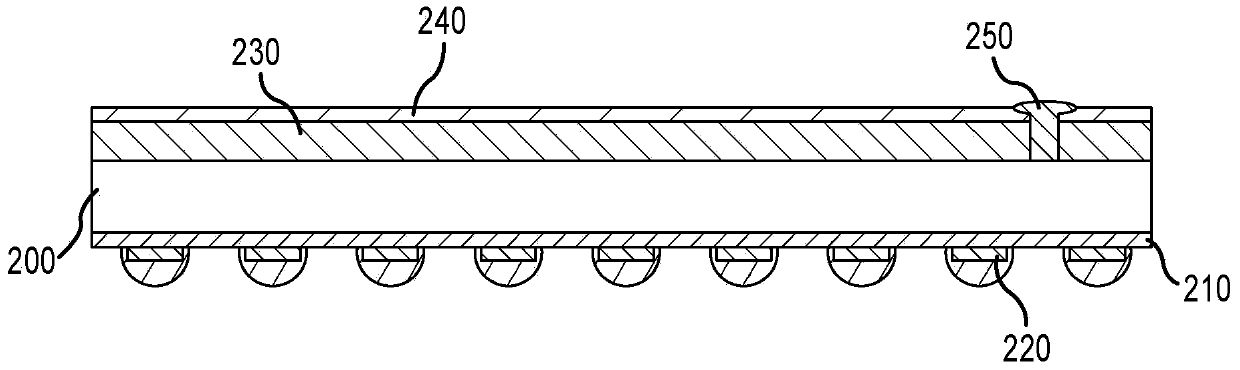

A wafer scale semiconductor integrated circuit packaging technique provides a hermetic seal for the individual integrated circuit die formed as part of the wafer scale structure. A semiconductor wafer is manufactured to include a number of individual semiconductor die. Each individual die formed on the wafer includes a number of bond pads that are exposed on the die surface in various locations to provide electrical connections to the circuitry created on the die. The wafer further includes a planar glass sheet that is substantially the same size as the wafer, the glass sheet being adhered to the wafer using a suitable adhesive. The glass sheet has a number of pre-formed holes in it, the arrangement of the pre-formed holes corresponding to the location of the bond pads at each of the individual semiconductor die formed as part of the wafer structure. Following adherence of the glass sheet to the semiconductor wafer utilizing the intermediate adhesive material, metal connections are made between pads formed on the glass sheet and the bond pads formed on the integrated circuit die. Solder balls are then attached to the pads on the glass sheet to provide a conductive flow between the solder balls and the bond pads. After the solder balls are attached, trenches are cut around each of the individual die on the wafer. The trenches are cut at an angle and extend through the glass sheet and the intermediate adhesive material and into the semiconductor substrate in which the integrated circuits are formed. After the trenches are cut around each individual semiconductor die, a noble metal is deposited on the sidewalls of the trench to extend over the interface between the glass sheet, the adhesive material and the semiconductor die. The wafer is then cut along the noble metal lined trenches to provide individual, hermetically sealed packaged integrated circuit die.

Owner:MICRO CHIP SCALE PACKAGING

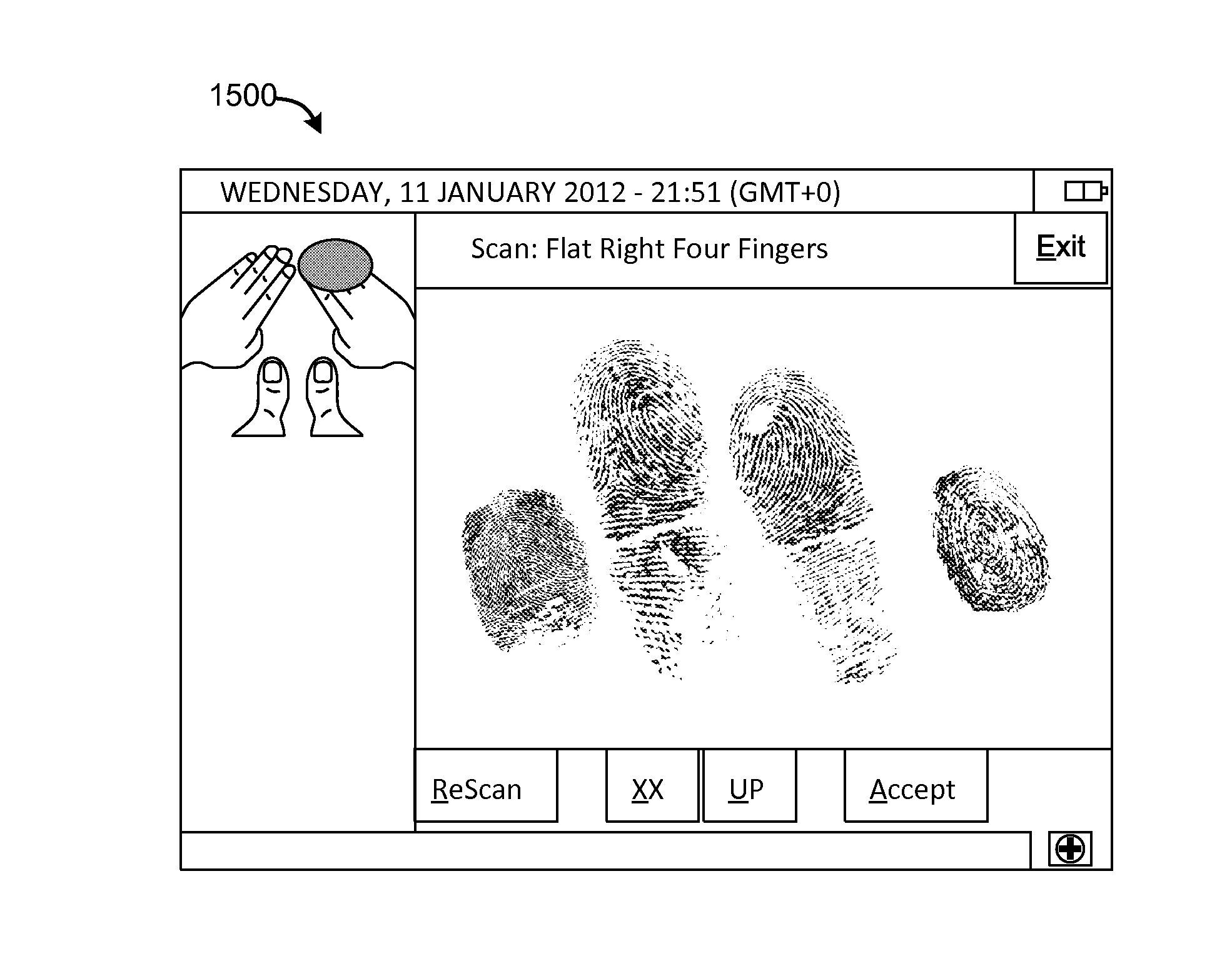

Finger asperity resistive discharge wafer-scale integration for forensic palm print collection

ActiveUS20130287271A1Made preciselySensing record carriersPrint image acquisitionPattern recognitionElectrical resistance and conductance

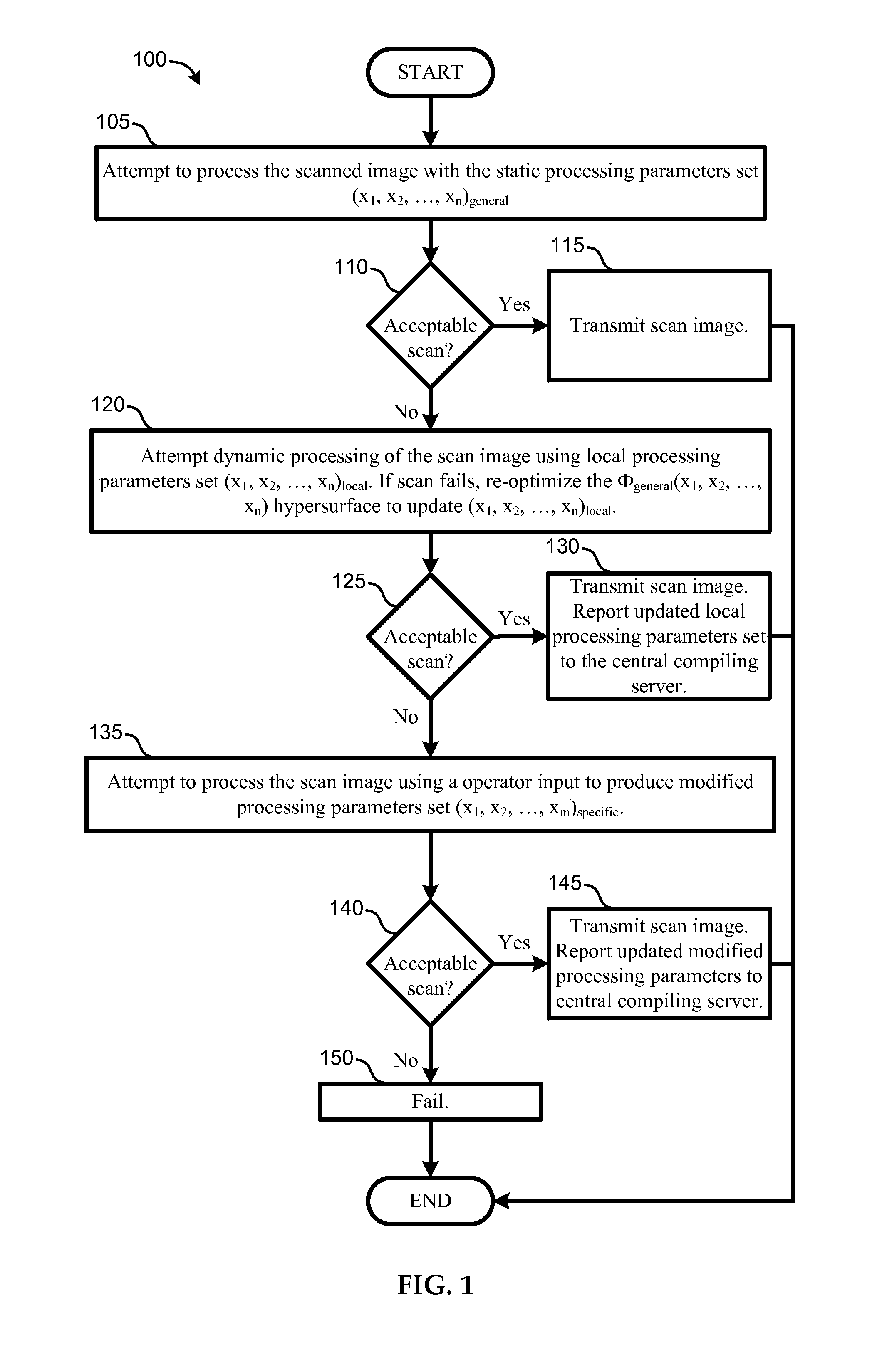

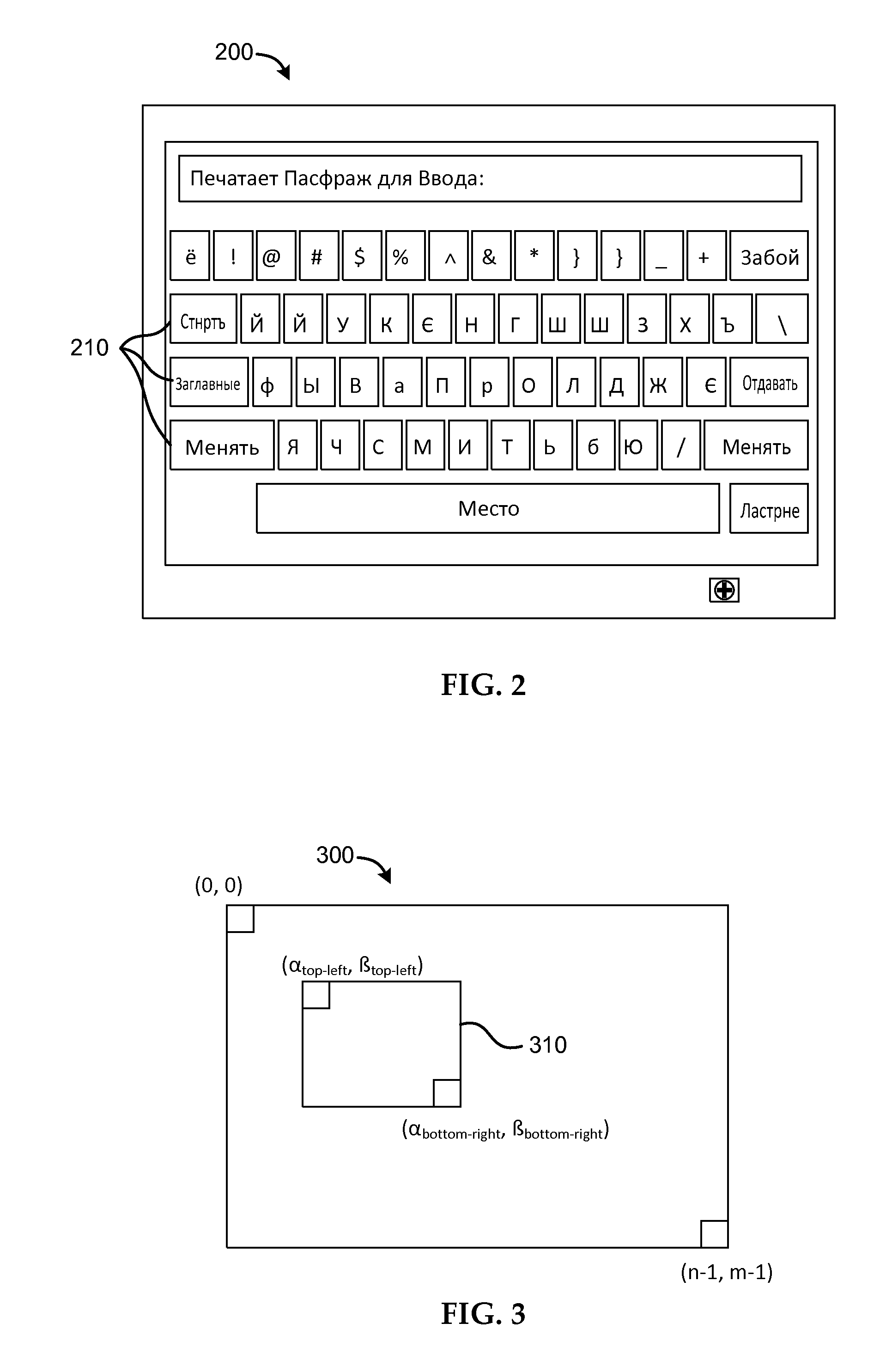

Techniques are disclosed herein for artificial intelligence machine learning to increase collection of digital livescan fingerprints. According to certain embodiments of the invention, processing parameters can be automatically machine-optimized for processing scan images of fingerprints (and other areas) to increase the amount of detected minutia. The processing parameters can alter and change over time to reflect historical successes and failures of particular optimizations. This allows a fingerprint collection device to learn over time and become more accurate (i.e., more successful at detecting minutia). Additionally, the techniques further include receiving input from a user regarding physical traits of a scanned subject, to further customize the processing parameter optimization. Various other features are provided herein.

Owner:HARPER JACK

Three-dimensional chip-to-wafer integration

ActiveCN103077933ASemiconductor/solid-state device detailsSolid-state devicesEngineeringDie (integrated circuit)

Disclosed is three-dimensional chip-to-wafer integration. An integrated circuit device is disclosed that includes a semiconductor substrate and a die attached to the semiconductor substrate. A conductive pillar is connected to at least one of the semiconductor substrate or the die. An overmold is molded onto the semiconductor substrate over the die, and the conductive pillar extends through the overmold.

Owner:MAXIM INTEGRATED PROD INC

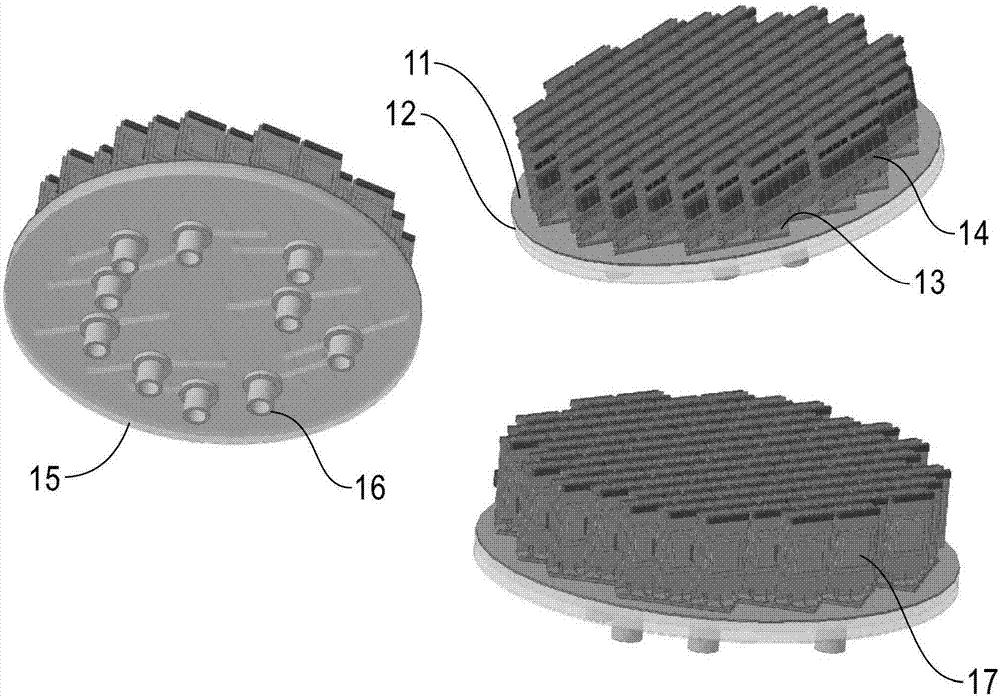

Supercomputer using wafer scale integration

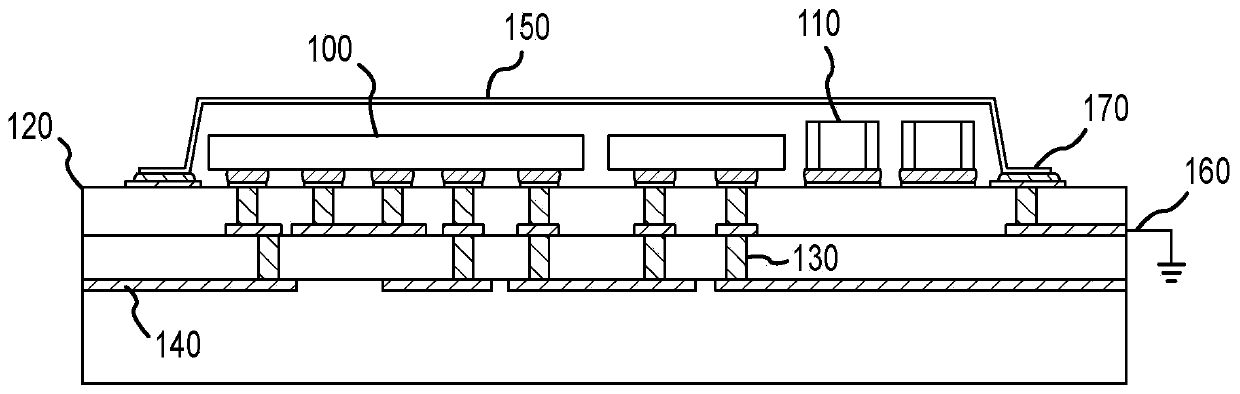

ActiveUS20160246337A1Unacceptable stressSemiconductor/solid-state device detailsSolid-state devicesElectricitySupercomputer

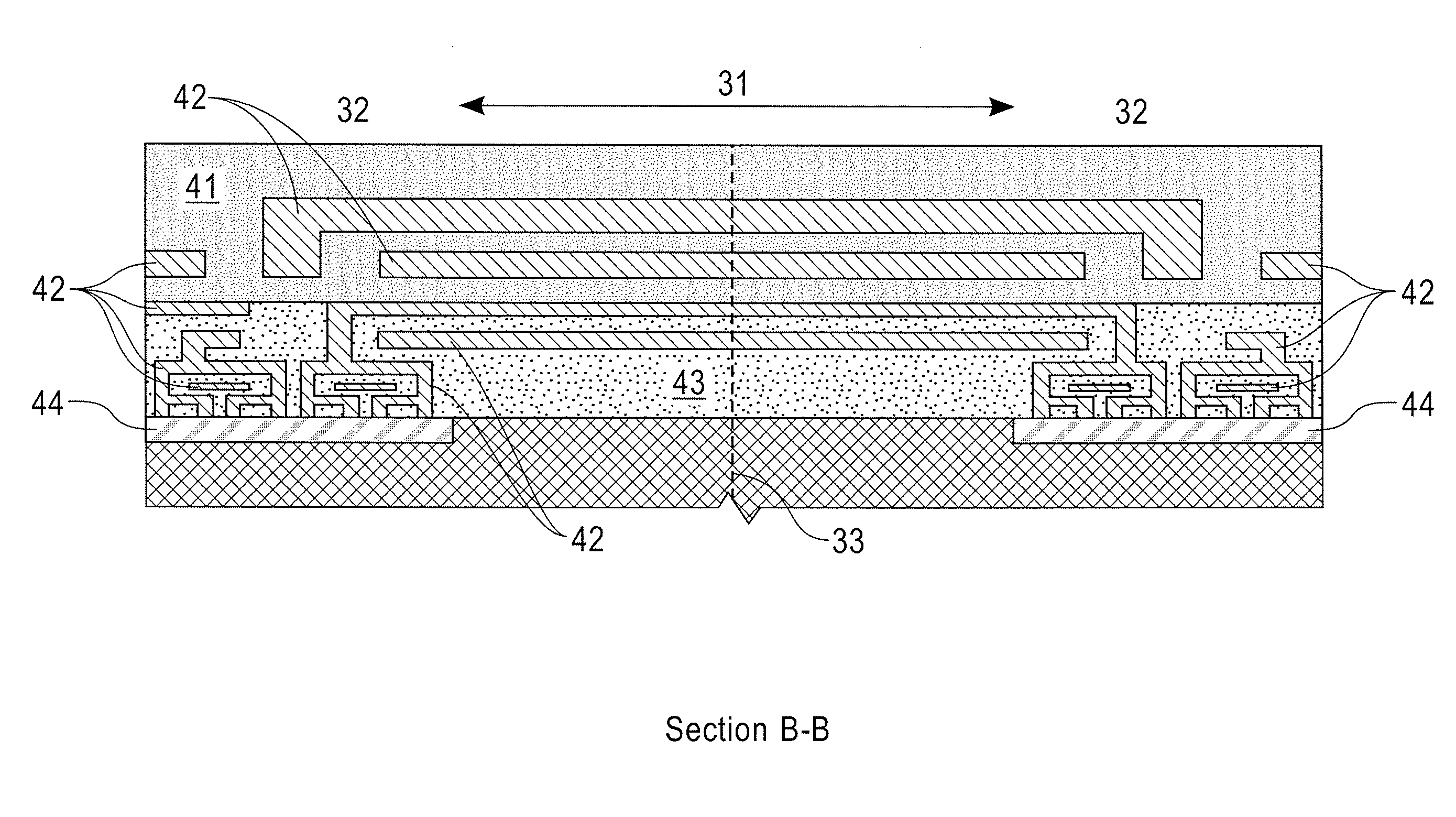

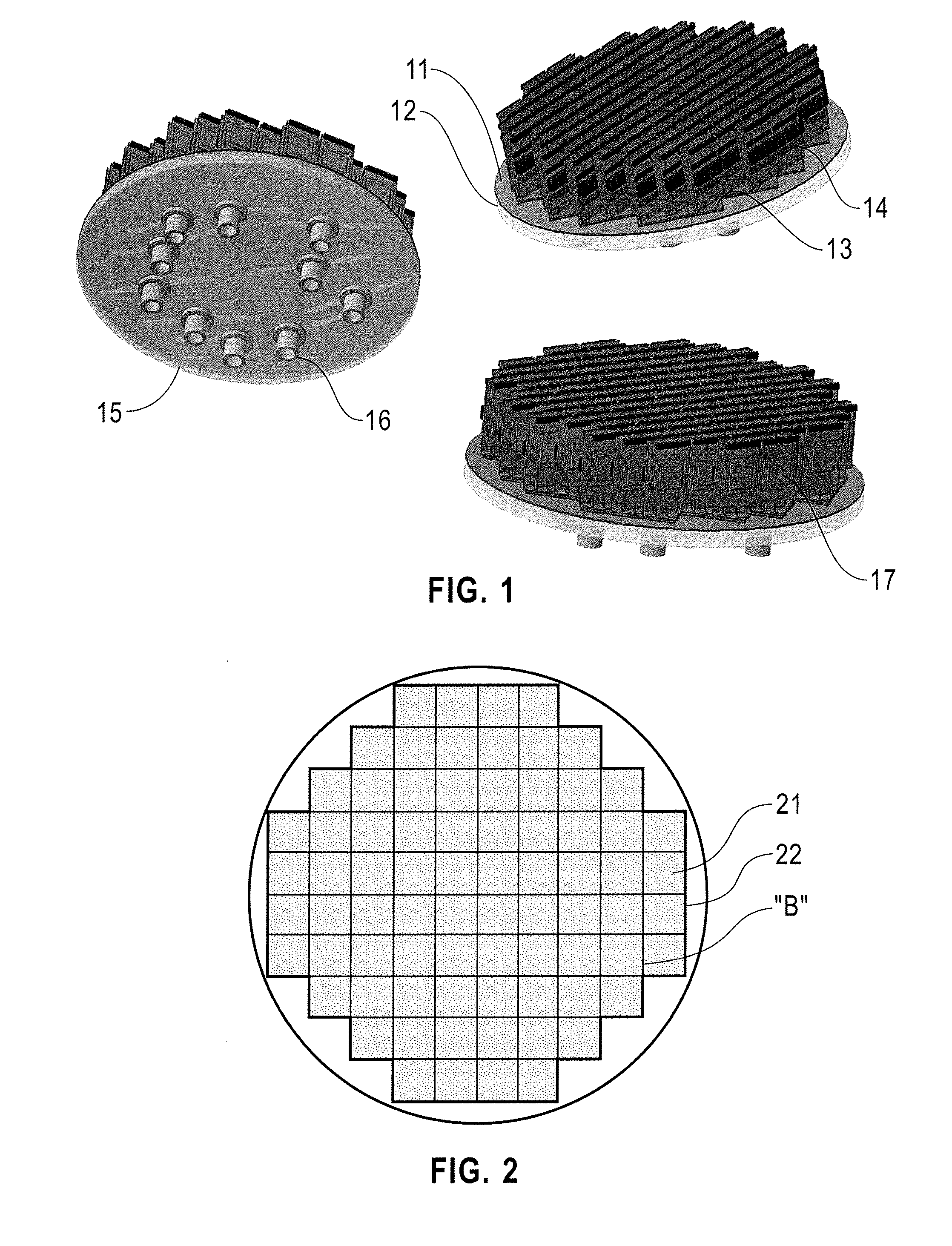

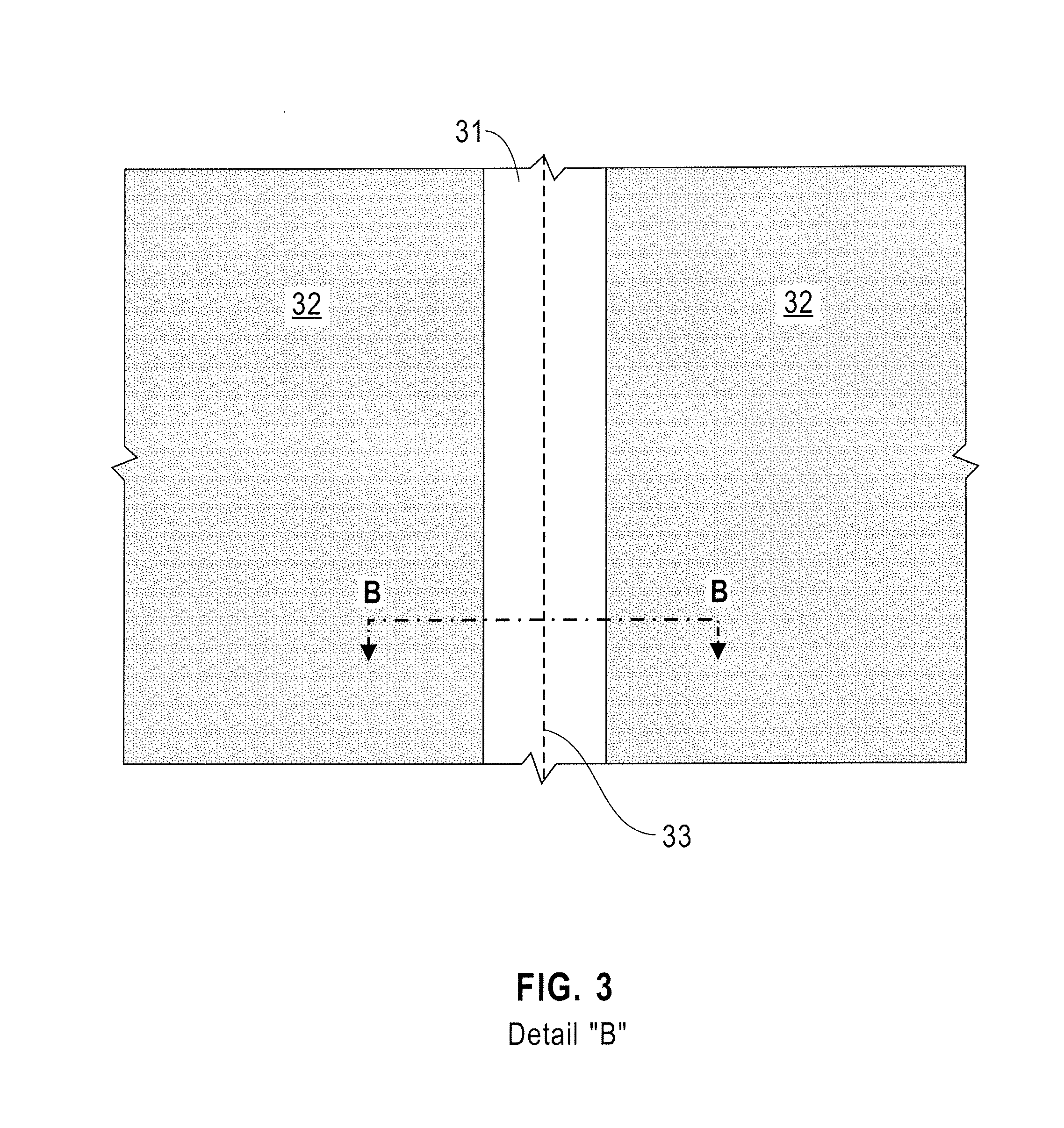

A semiconductor structure includes a substrate with cooling layers, cooling channels, coolant inlets and outlets in fluid communication with the cooling channels, and a device layer on the cooling layers with one or more connection points and a device layer area. The device layer thermal coefficient of expansion is substantially equal to that of the cooling layers. A plurality of laminate substrates are disposed on, and electrically attached to, the device layer. The laminate substrate thermal coefficient of expansion differs from that of the device layer, each laminate substrate is smaller than the device layer portion to which it is attached, and each laminate substrate includes gaps between sides of adjacent laminate substrates. The laminate substrates are not electrically or mechanically connected to each other across the gaps therebetween and the laminate substrates are small enough to prevent warping of the device, interconnection and cooling layers due to thermal expansion.

Owner:IBM CORP

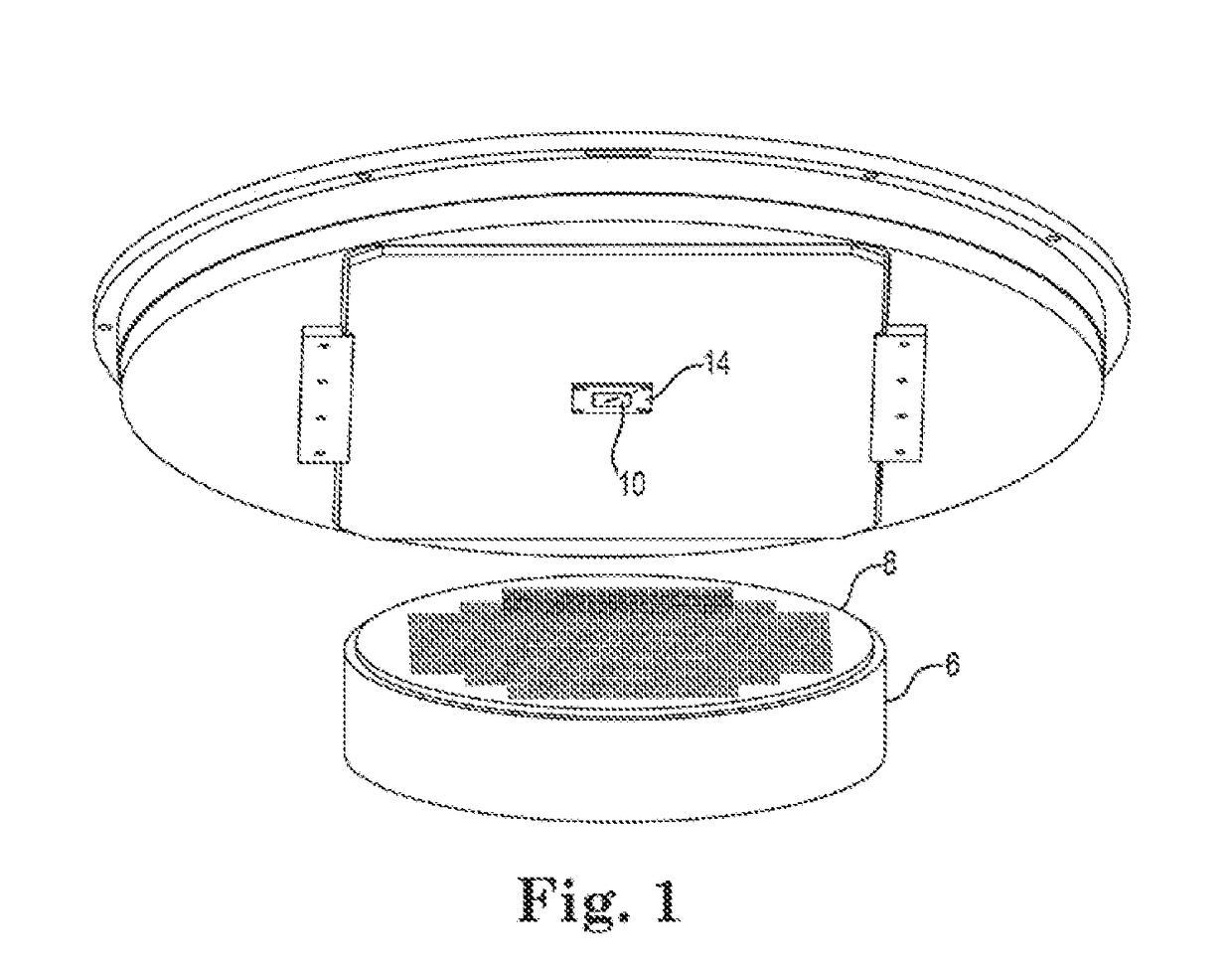

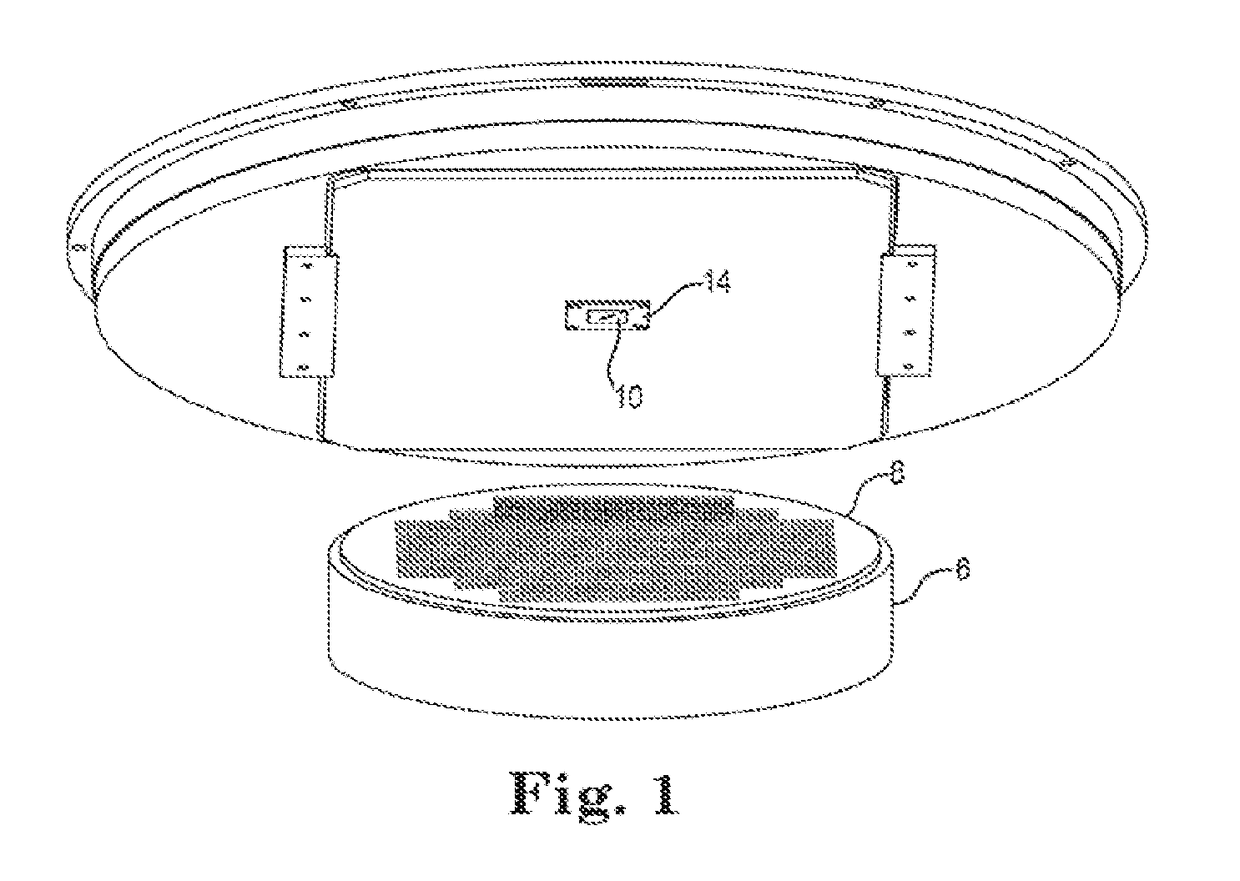

Wafer level integration of multiple optical elements

InactiveUS20070110361A1Efficient productionPrecise cuttingLamination ancillary operationsSynthetic resin layered productsEngineeringWafer-scale integration

Integrated multiple optical elements may be formed by bonding substrates containing such optical elements together or by providing optical elements on either side of the wafer substrate. The wafer is subsequently diced to obtain the individual units themselves. The optical elements may be formed lithographically, directly, or using a lithographically generated master to emboss the elements. Alignment features facilitate the efficient production of such integrated multiple optical elements, as well as post creation processing thereof on the wafer level.

Owner:FLIR SYSTEMS TRADING BELGIUM BVBA +1

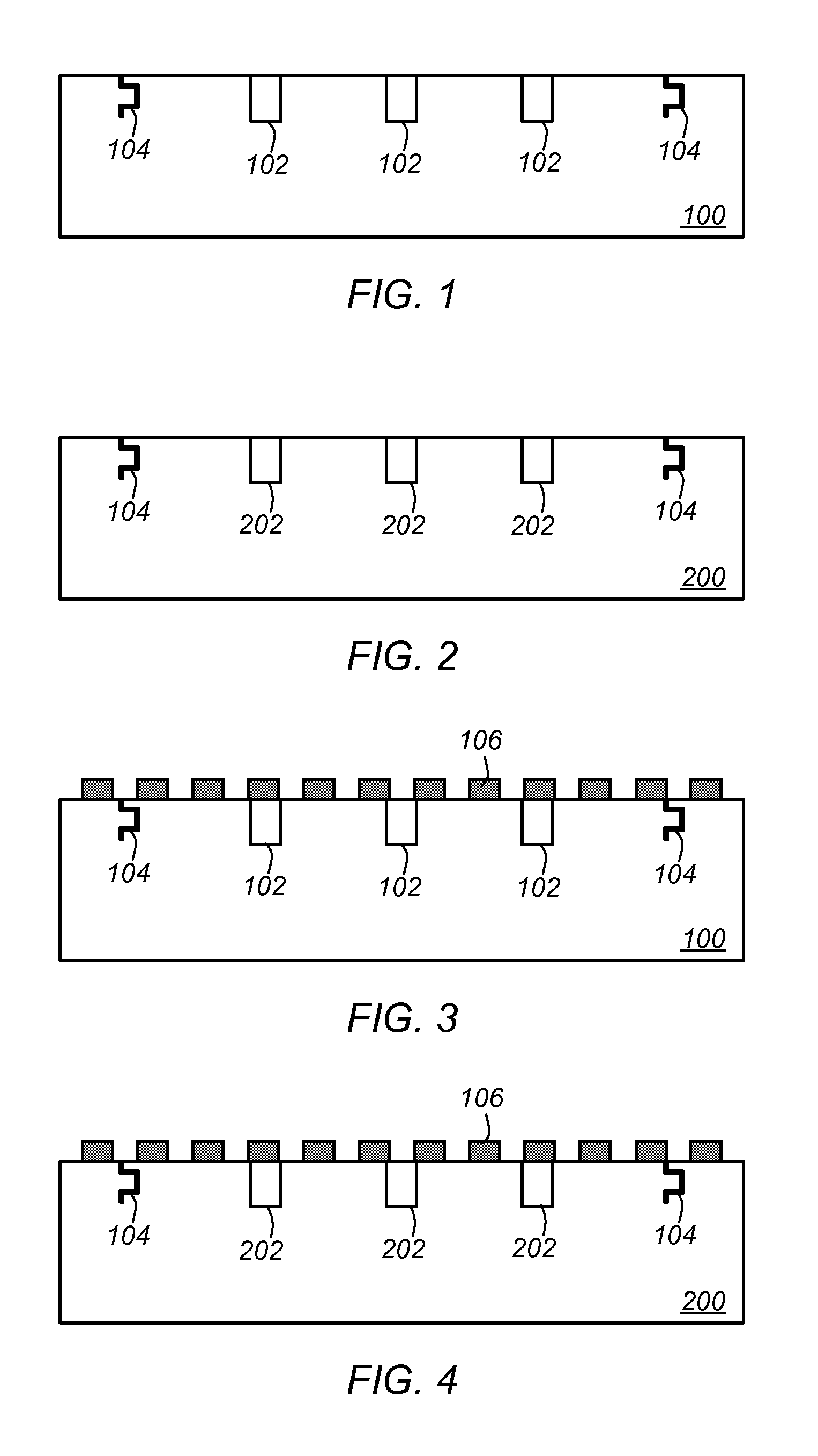

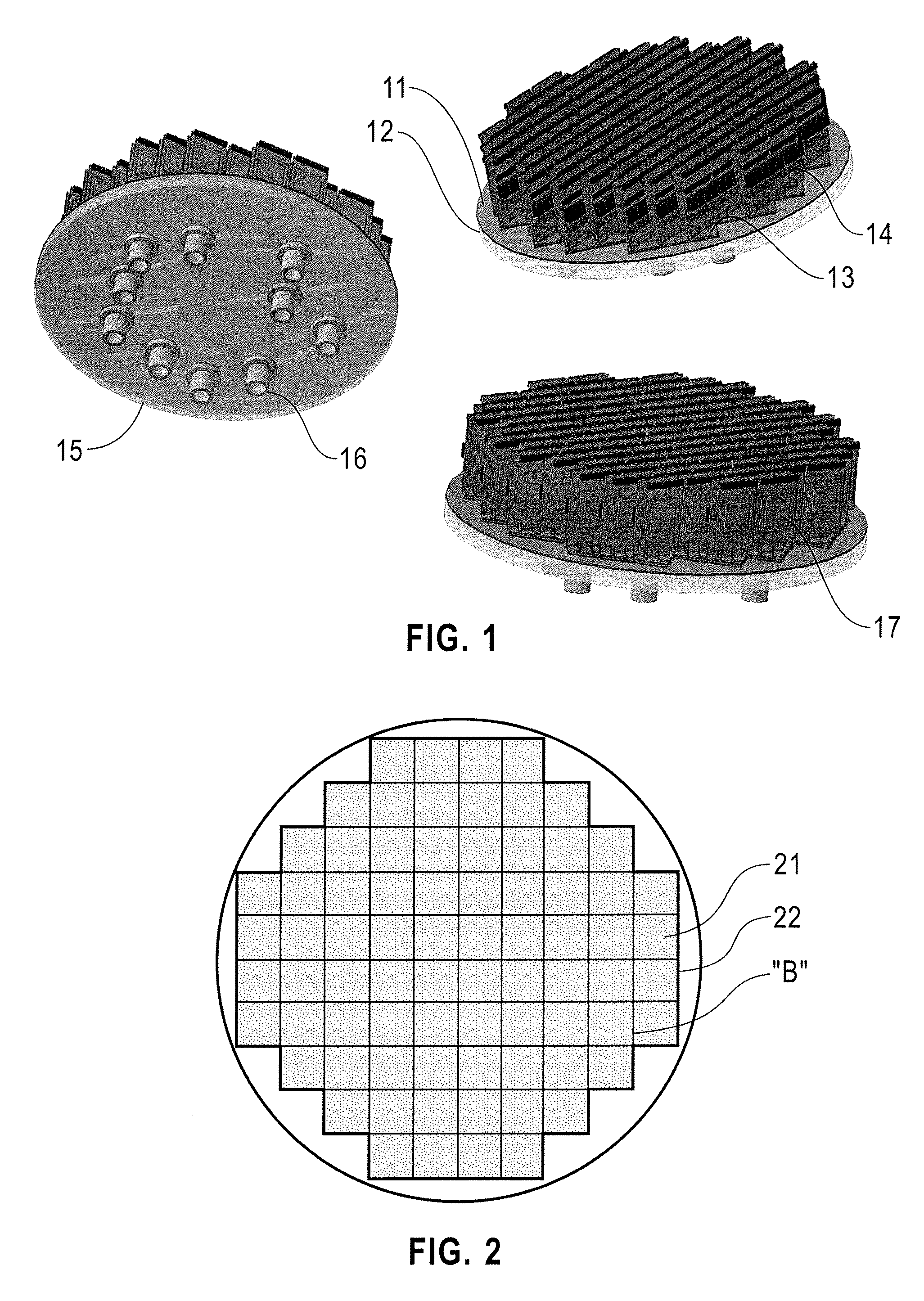

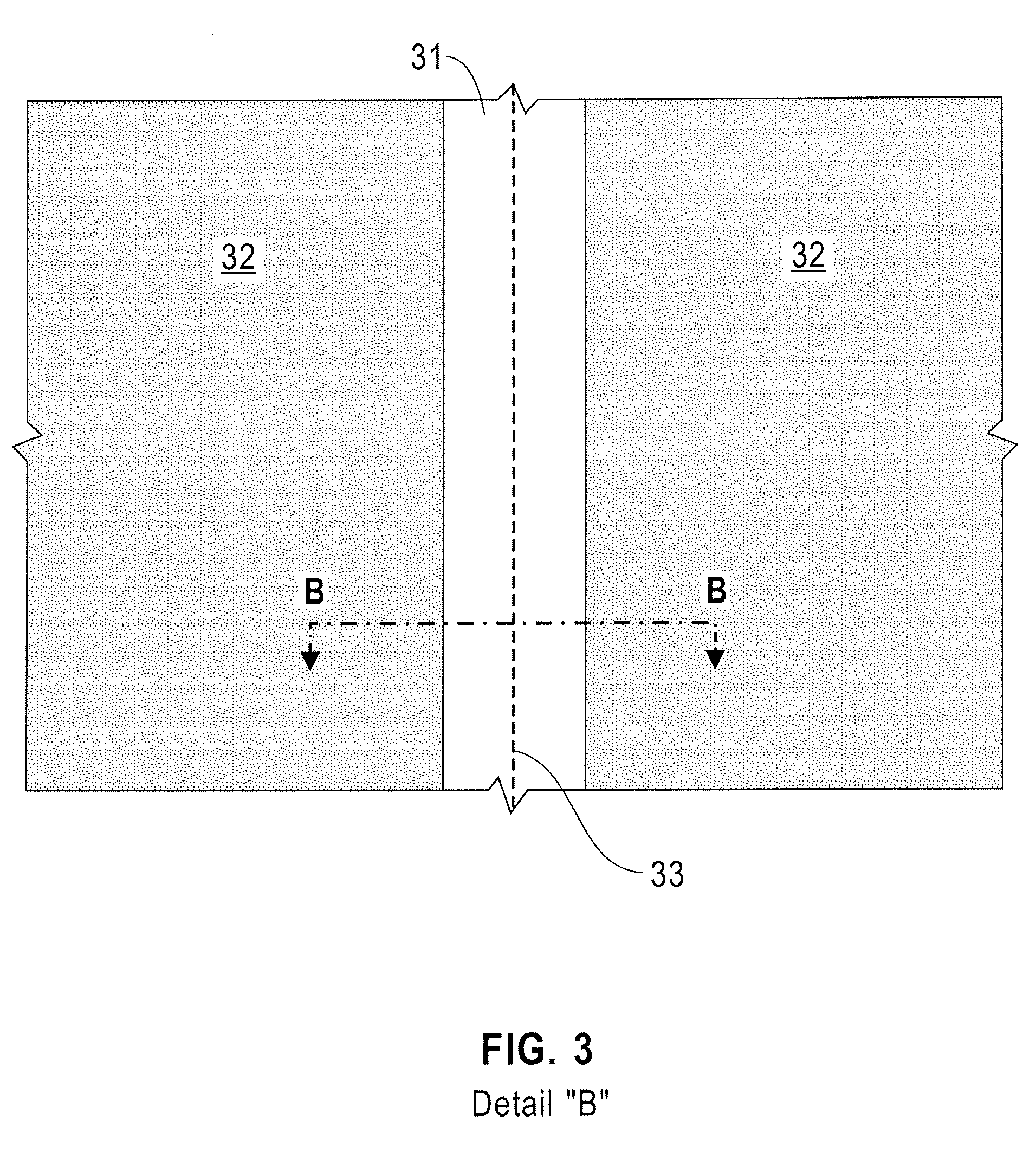

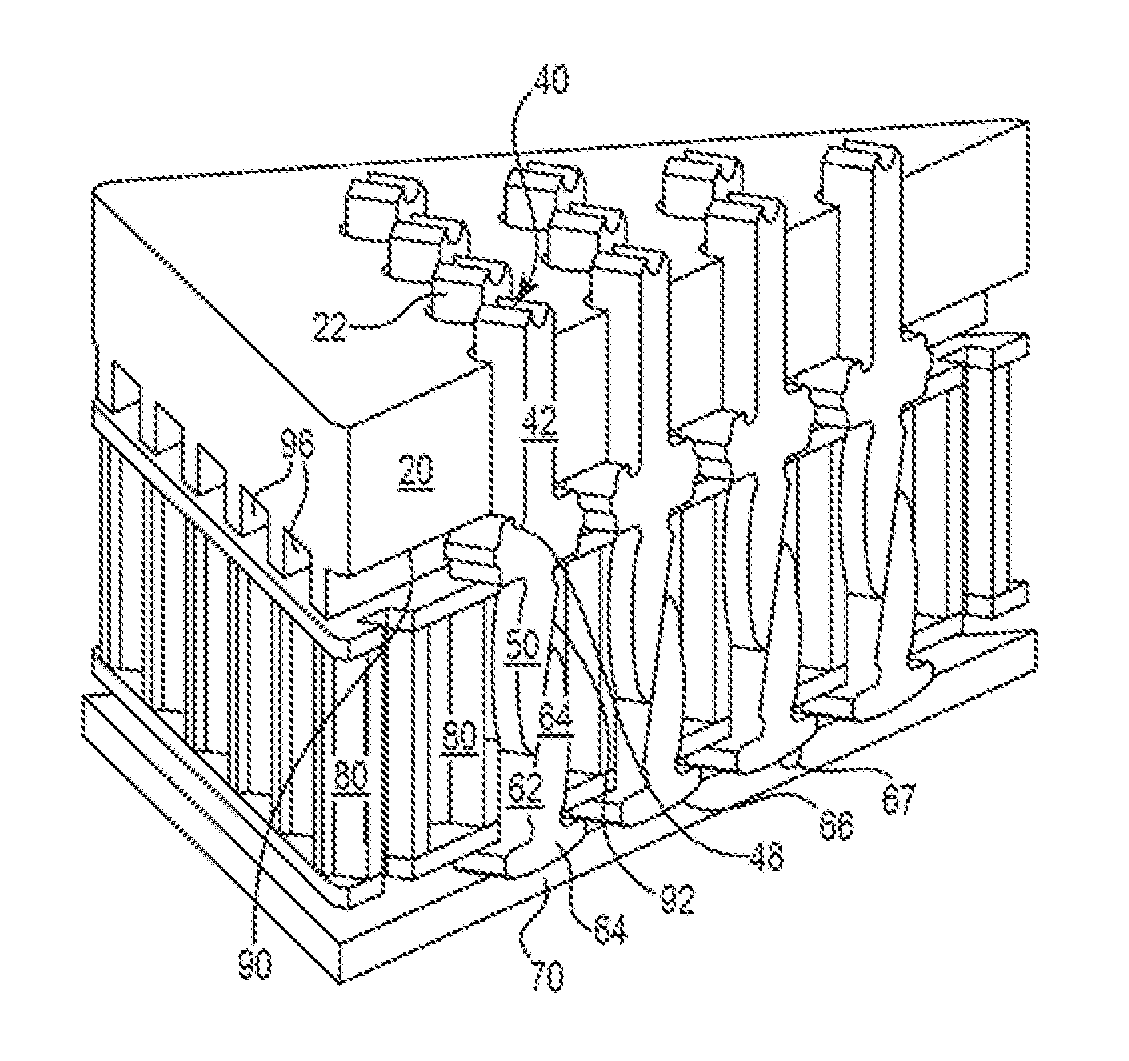

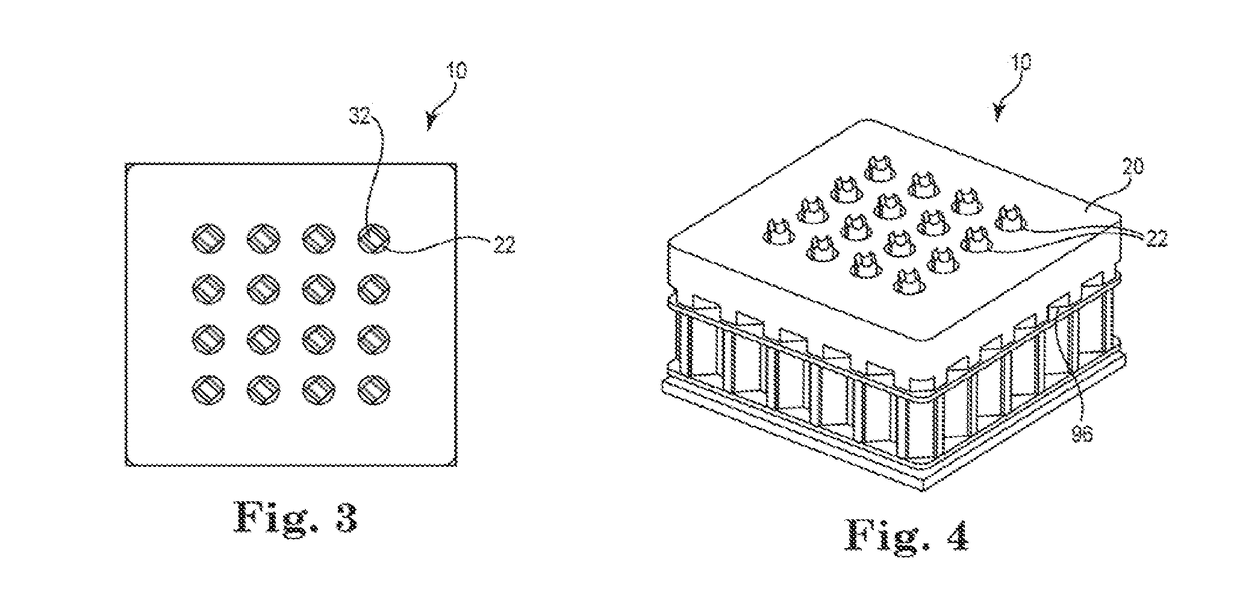

Wafer level integrated circuit contactor and method of construction

ActiveUS9261537B2Accurate locationEasy to processContact member manufacturingElectrical measurement instrument detailsElastomerPre compression

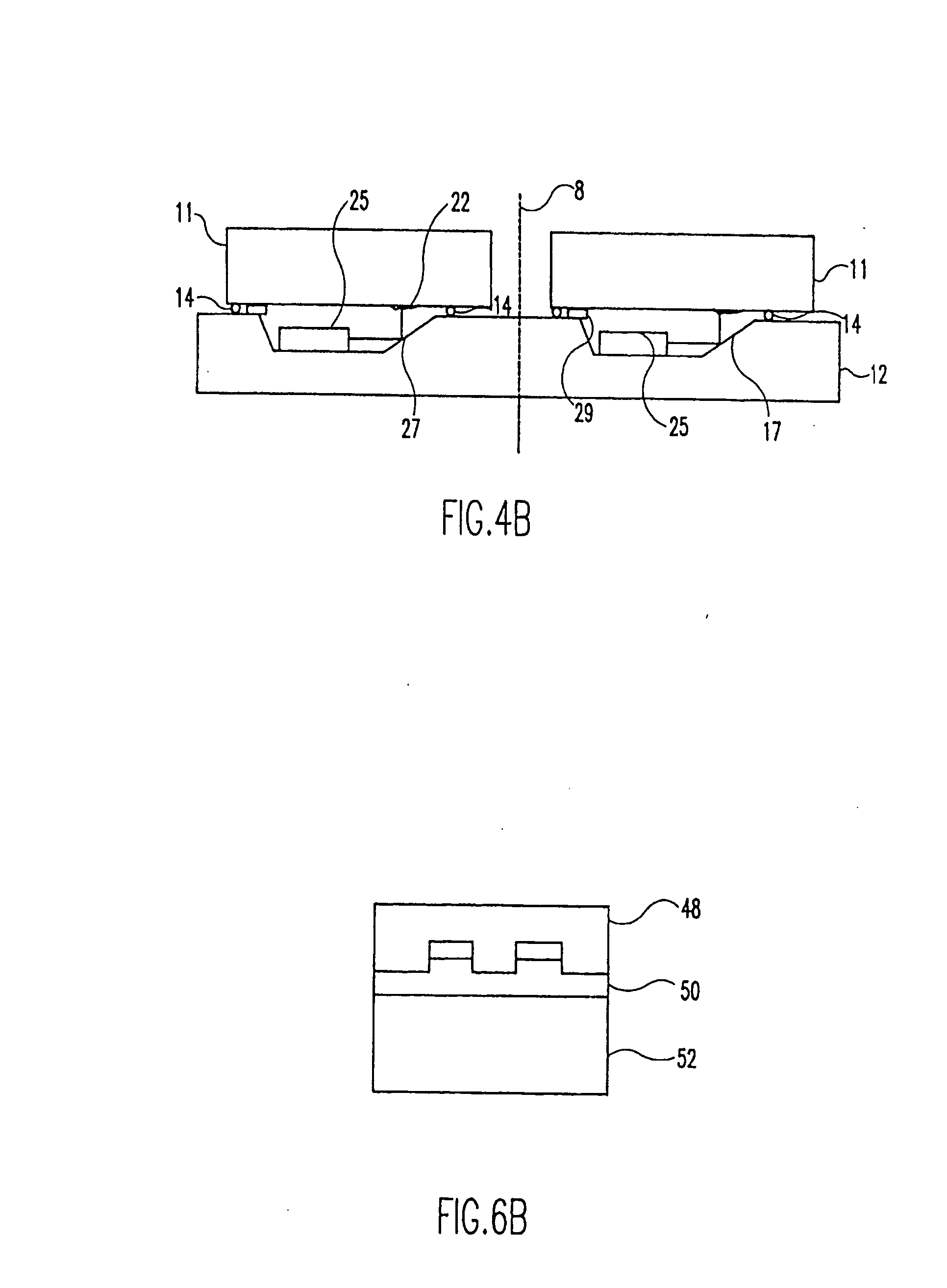

A testing device for wafer level testing of IC circuits is disclosed. An upper and lower pin (22, 62) are configured to slide relatively to each other and are held in electrically biased contact by an elastomer (80). The elastomer is precompressed from its natural rest state between a top (22) plate and a bottom (70). Pre compression improves the resilient response of the pins. The pin crows (40) are maintained relatively coplanar by the engagement of at least one flang (44a-b) against an up-stop surface 90 of plate 20, thereby insuring coplanarity of the crowns. The pin guide (12) is maintained in alignment with the retainer 14 by establishing a registration corner (506) and driving the guide into the corner by elastomers in at least one diagonally opposite corner.

Owner:JOHNSTECH INT

Hermetic wafer scale integrated circuit structure

InactiveUS7205635B1Prevent surfaceDamaged and destroyedSemiconductor/solid-state device detailsSolid-state devicesScale structureHermetic seal

A wafer scale semiconductor integrated circuit packaging technique provides a hermetic seal for the individual integrated circuit die formed as part of the wafer scale structure. A semiconductor wafer is manufactured to include a number of individual semiconductor die. Each individual die formed on the wafer includes a number of bond pads that are exposed on the die surface in various locations to provide electrical connections to the circuitry created on the die. The wafer further includes a planar glass sheet that is substantially the same size as the wafer, the glass sheet being adhered to the wafer using a suitable adhesive. The glass sheet has a number of pre-formed holes in it, the arrangement of the pre-formed holes corresponding to the location of the bond pads at each of the individual semiconductor die formed as part of the wafer structure. Following adherence of the glass sheet to the semiconductor wafer utilizing the intermediate adhesive material, metal connections are made between pads formed on the glass sheet and the bond pads formed on the integrated circuit die. Solder balls are then attached to the pads on the glass sheet to provide a conductive flow between the solder balls and the bond pads. After the solder balls are attached, trenches are cut around each of the individual die on the wafer. The trenches are cut at an angle and extend through the glass sheet and the intermediate adhesive material and into the semiconductor substrate in which the integrated circuits are formed. After the trenches are cut around each individual semiconductor die, a noble metal is deposited on the sidewalls of the trench to extend over the interface between the glass sheet, the adhesive material and the semiconductor die. The wafer is then cut along the noble metal lined trenches to provide individual, hermetically sealed packaged integrated circuit die.

Owner:MICRO CHIP SCALE PACKAGING

Wafer Level Integrated Circuit Probe Array and Method of Construction

ActiveUS20170074926A1Easy to processGuarantees proper engagementElectronic circuit testingElectrical measurement instrument detailsElastomerDiagonal

A testing device for wafer level testing of IC circuits is disclosed. An upper and lower pin (22, 62) are configured to slide relatively to each other and are held in electrically biased contact by an elastomer (80). To prevent rotation of the pins in the pin guide, a walled recess in the bottom of the pin guide engages flanges on the pins. In another embodiment, the pin guide maintains rotational alignment by being fitted around the pin profile or having projections abutting the pin. The pin guide (12) is maintained in alignment with the retainer 14 by establishing a registration corner (506) and driving the guide into the corner by elastomers in at least one diagonally opposite corner.

Owner:JOHNSTECH INT

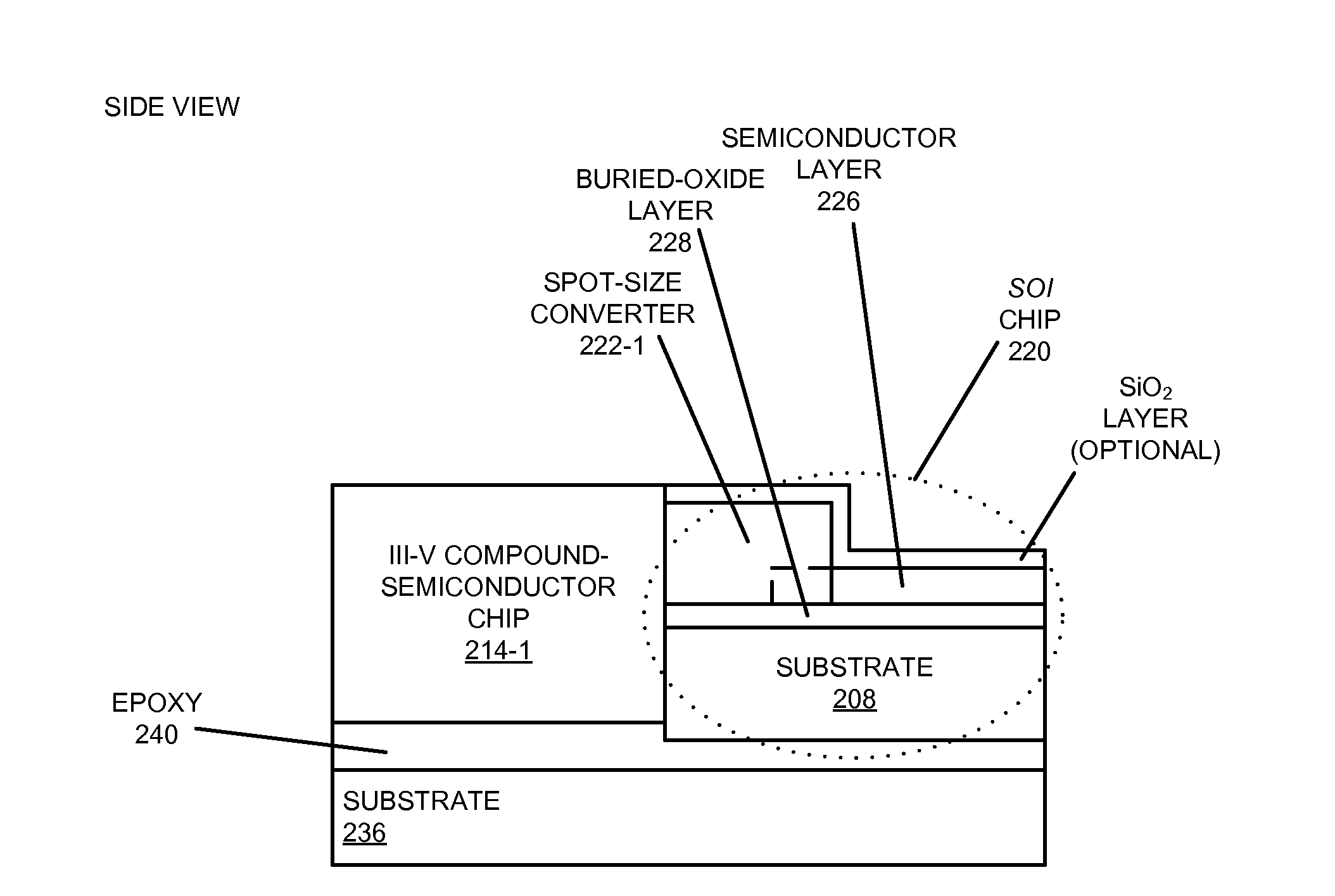

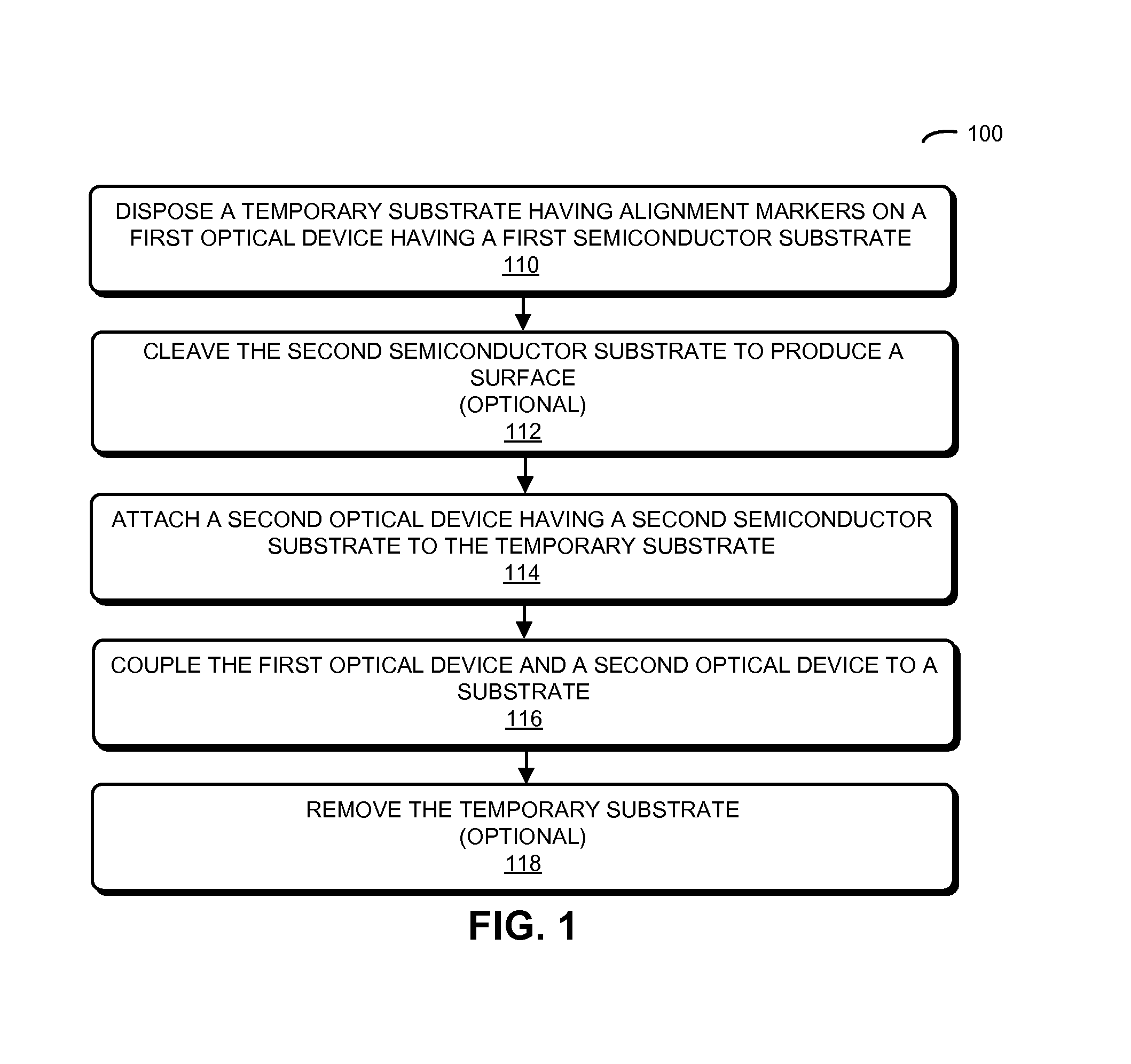

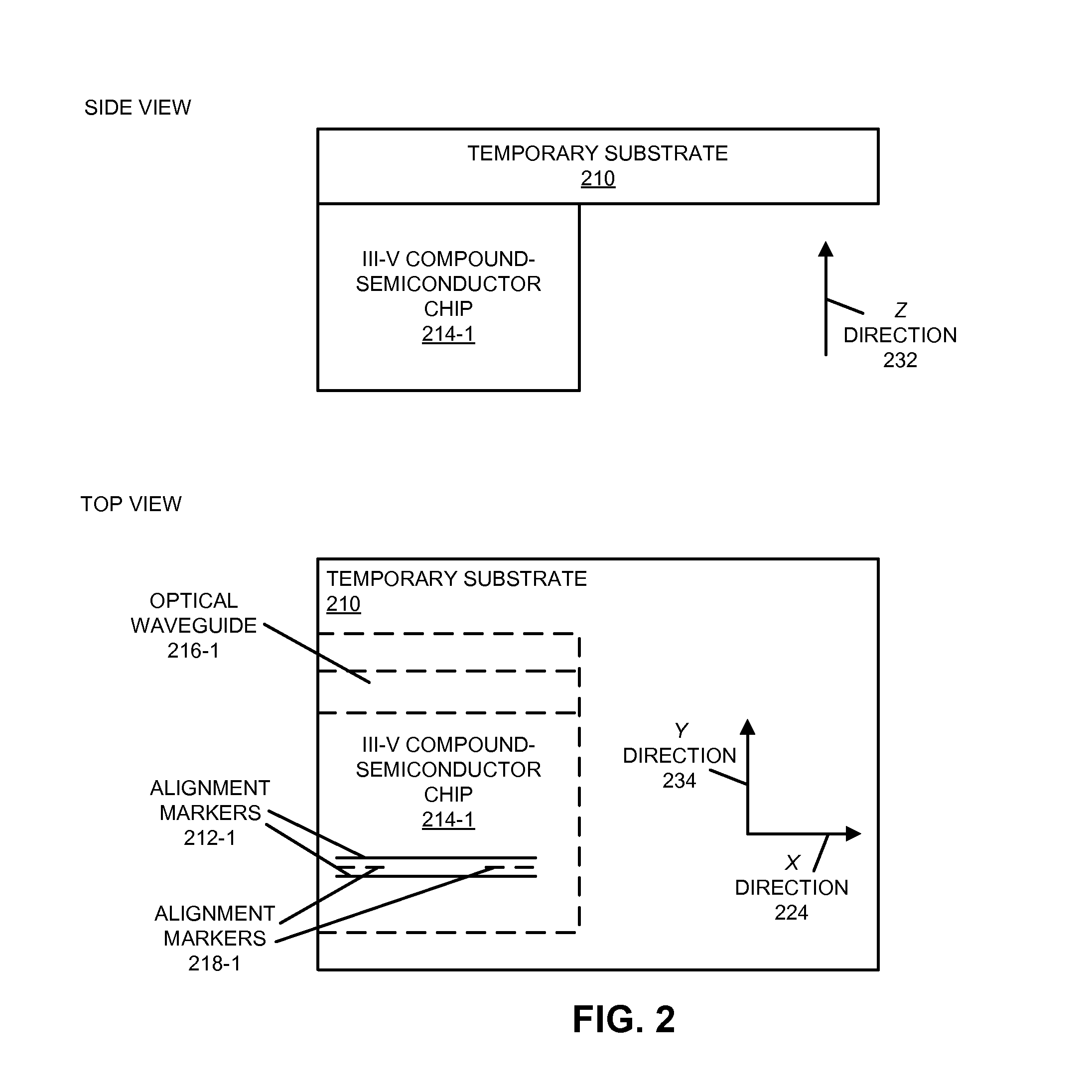

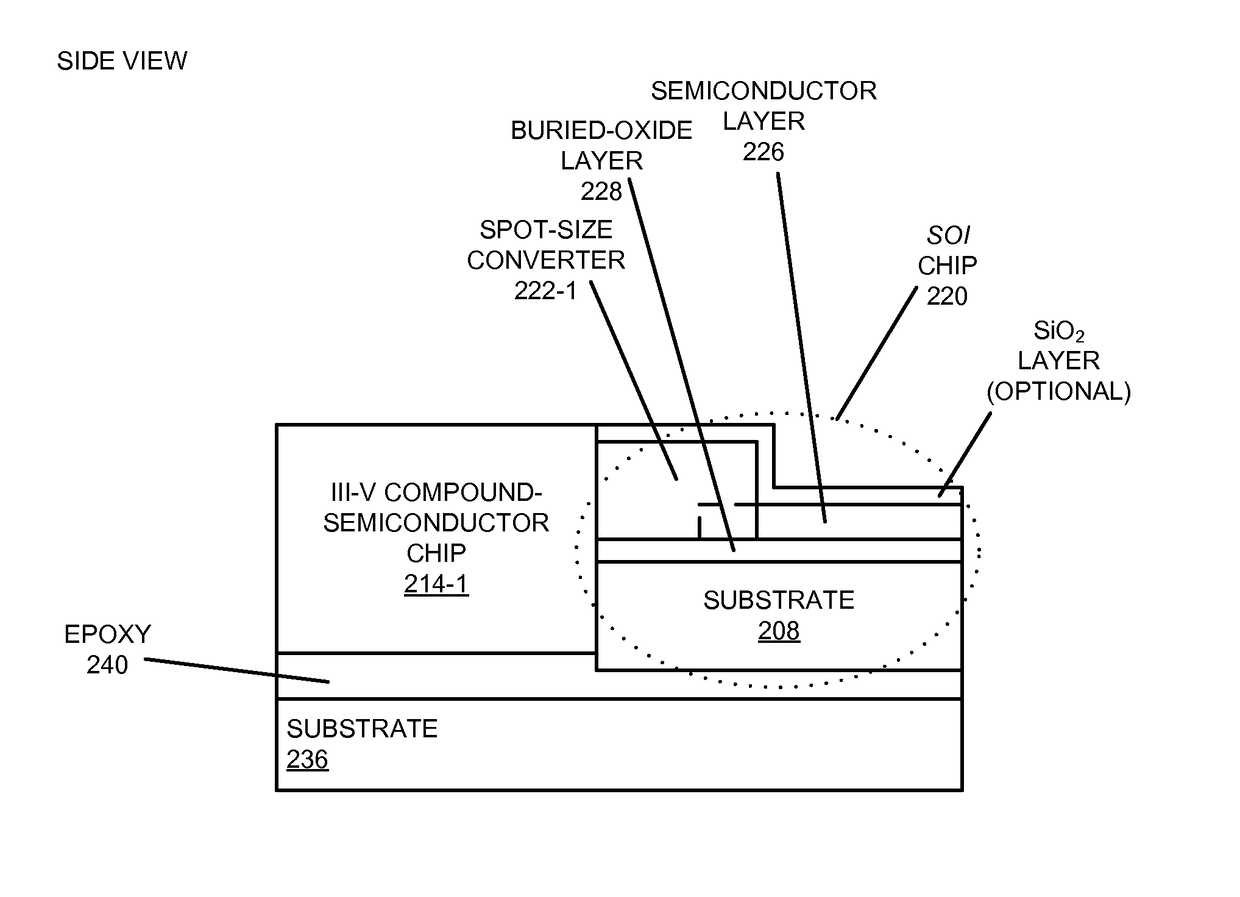

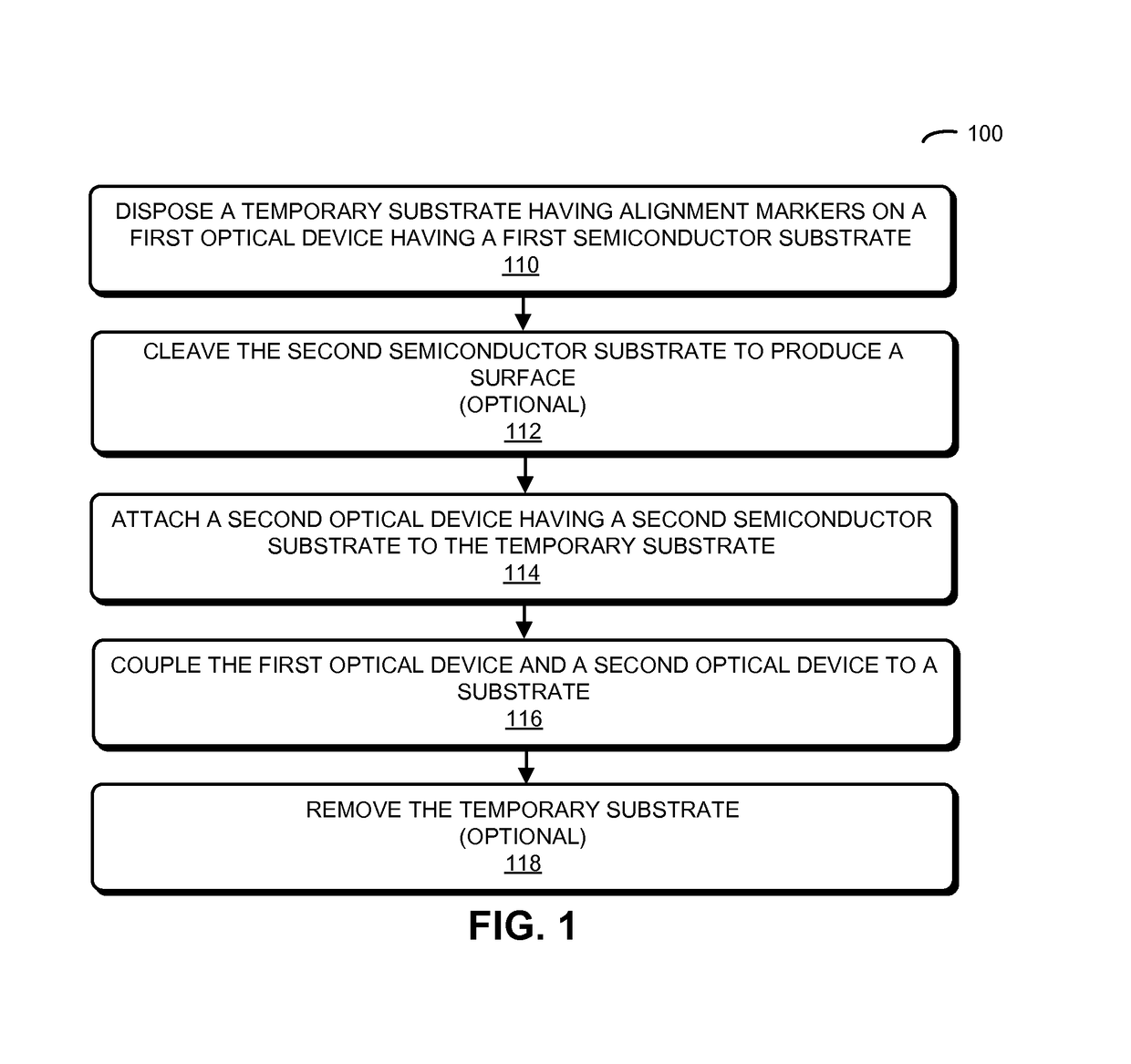

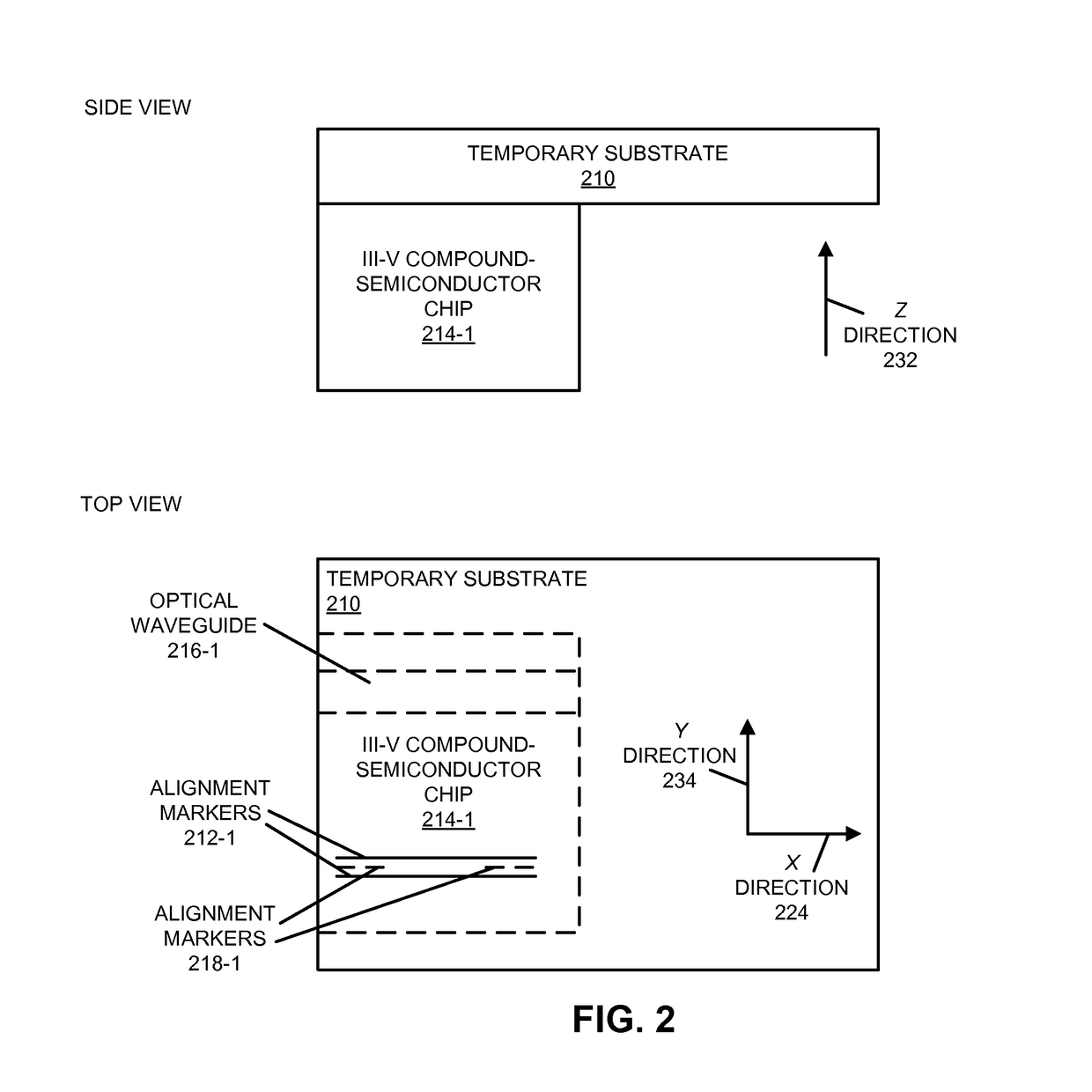

Hybrid integration of edge-coupled chips

ActiveUS20160170158A1Easy to separateLaser detailsLaser active region structureManufacturing technologySemiconductor chip

A technique for fabricating a hybrid optical source is described. During this fabrication technique, a III-V compound-semiconductor active gain medium is integrated with a silicon-on-insulator (SOI) chip (or wafer) using edge coupling to form a co-planar hybrid optical source. Using a backside etch-assisted cleaving technique, and a temporary transparent substrate with alignment markers, a III-V compound-semiconductor chip with proper edge polish and coating can be integrated with a processed SOI chip (or wafer) with accurate alignment. This fabrication technique may significantly reduce the alignment complexity when fabricating the hybrid optical source, and may enable wafer-scale integration.

Owner:ORACLE INT CORP

Wafer level integration of passive devices

ActiveUS20160093592A1Semiconductor/solid-state device detailsSolid-state devicesVoltage regulationEngineering

A semiconductor device is described that includes an integrated circuit coupled to a first semiconductor substrate with a first set of passive devices (e.g., inductors) on the first substrate. A second semiconductor substrate with a second set of passive devices (e.g., capacitors) may be coupled to the first substrate. Interconnects in the substrates may allow interconnection between the substrates and the integrated circuit. The passive devices may be used to provide voltage regulation for the integrated circuit. The substrates and integrated circuit may be coupled using metallization.

Owner:APPLE INC

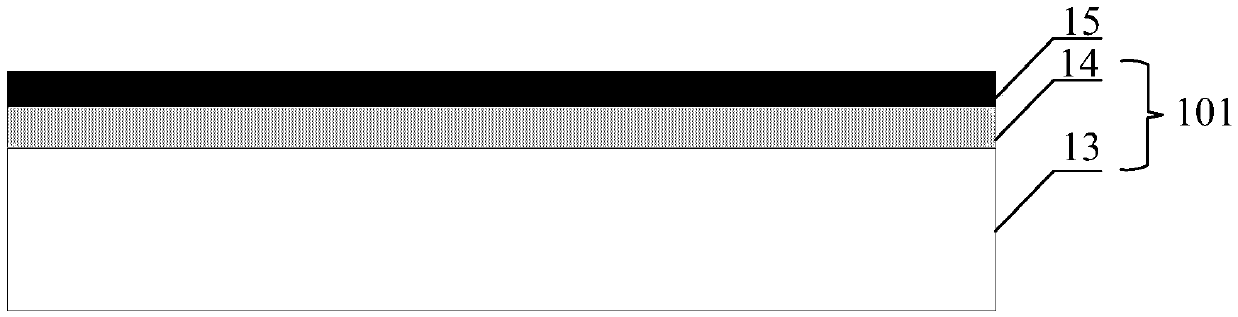

Preparation method of Si-based substrate heterogeneous integrated graphene

The invention relates to a preparation method of Si-based substrate heterogeneous integrated graphene. The method comprises the following steps: providing a Si-based substrate, and forming a dielectric layer on the upper surface of the Si-based substrate; providing a composite structure, wherein the composite structure comprises a sacrificial substrate and a metal layer covering the upper surfaceof the sacrificial substrate; depositing a graphene film on the upper surface of the composite structure to form a graphene layer covering the metal layer; bonding the side, covered with the dielectric layer, of the Si-based substrate with the side, covered with the graphene film, of the composite structure; and etching the metal layer by adopting an etching process to realize separation of the sacrificial substrate, so that the graphene film is transferred to the Si-based substrate. According to the method, a graphene film is transferred to a Si-based substrate, so that the problem of wafer-level integration of the graphene film and the Si-based substrate is solved, and support is provided for application of graphene in the field of microelectronic devices.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

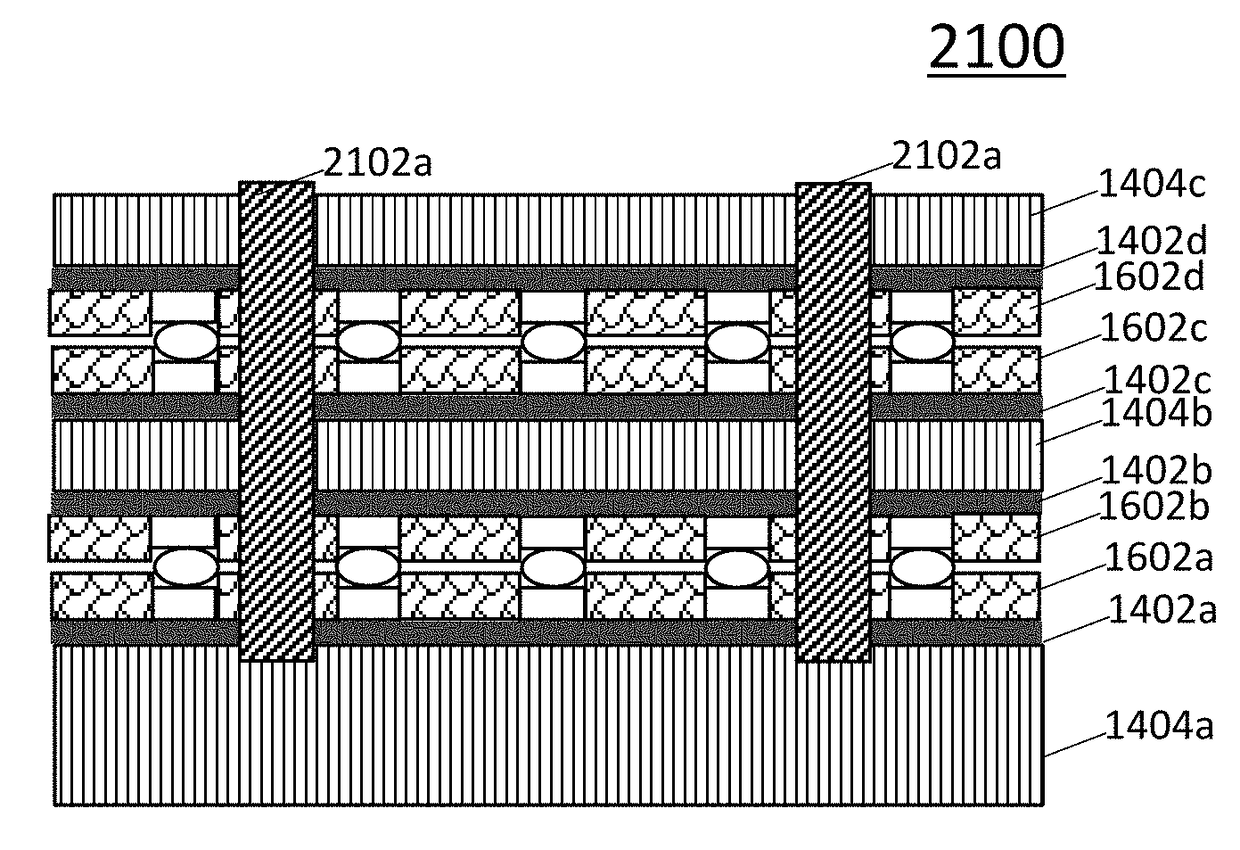

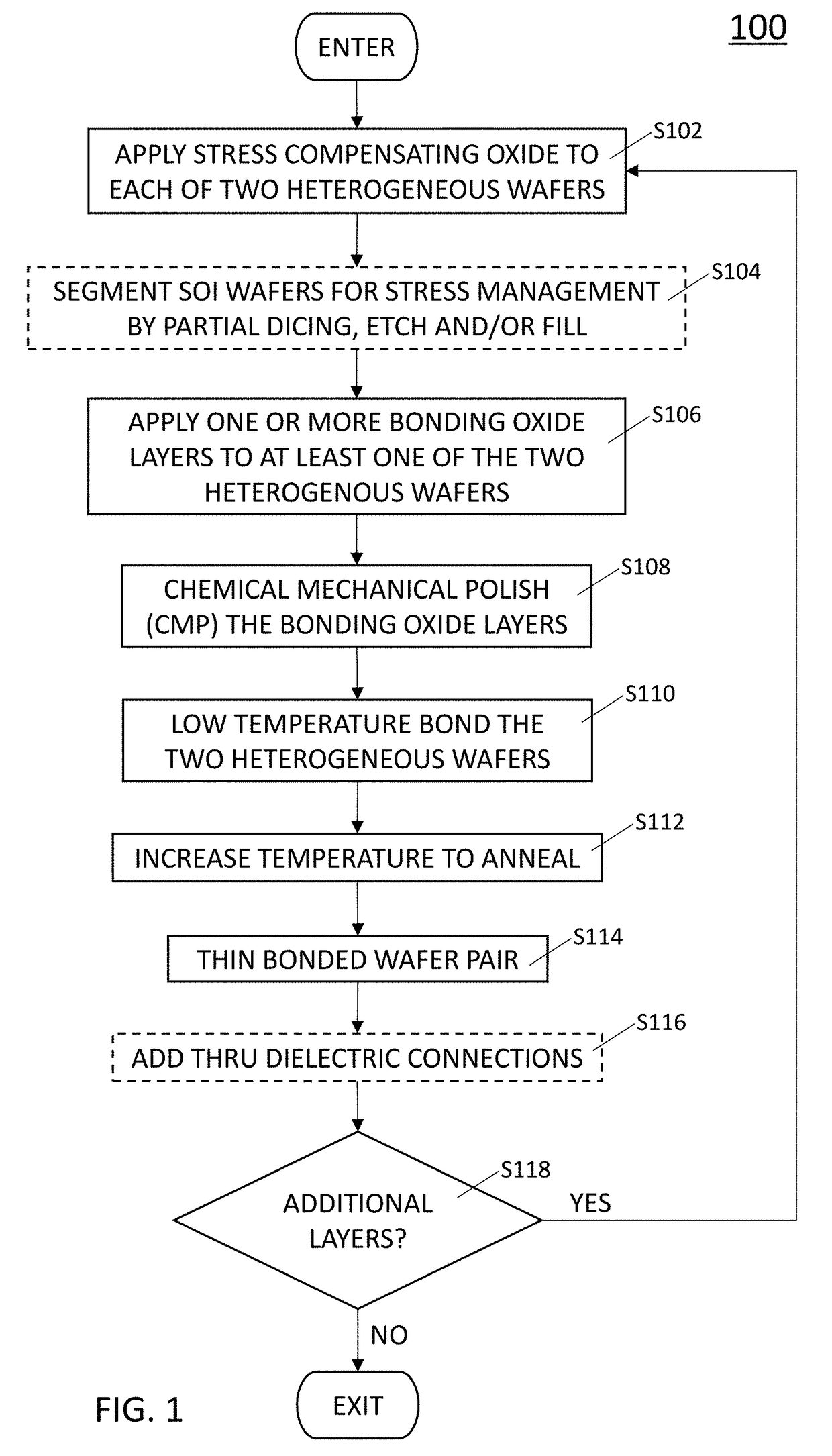

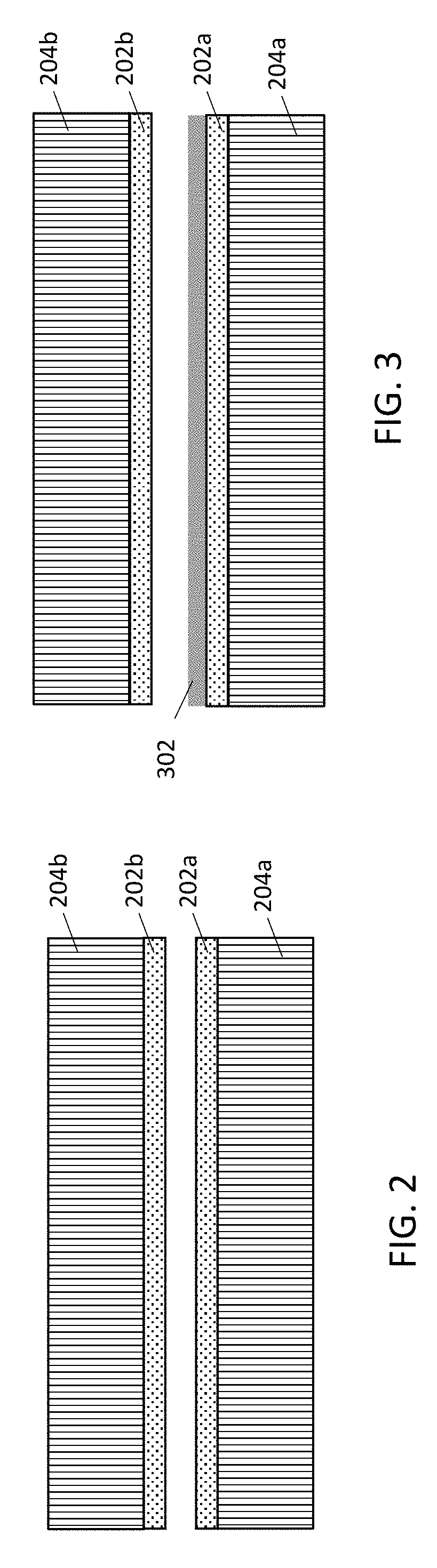

Wafer level integration including design/co-design, structure process, equipment stress management, and thermal management

ActiveUS20180082888A1TransistorSemiconductor/solid-state device detailsEngineeringWafer-scale integration

A multi-layer wafer and method of manufacturing such wafer are provided. The method comprises applying a stress compensating oxide layer to each of two heterogeneous wafers, applying at least one bonding oxide layer to at least one of the two heterogeneous wafers, chemical-mechanical polishing the at least one bonding oxide layer, and low temperature bonding the two heterogeneous wafers to form a multi-layer wafer pair. The multi-layer wafer comprises two heterogeneous wafers, each of the heterogeneous wafers having a stress compensating oxide layer and at least one bonding oxide layer applied to at least one of the two heterogeneous wafers. The two heterogeneous wafers are low temperature bonded together to form the multi-layer wafer.

Owner:IBM CORP

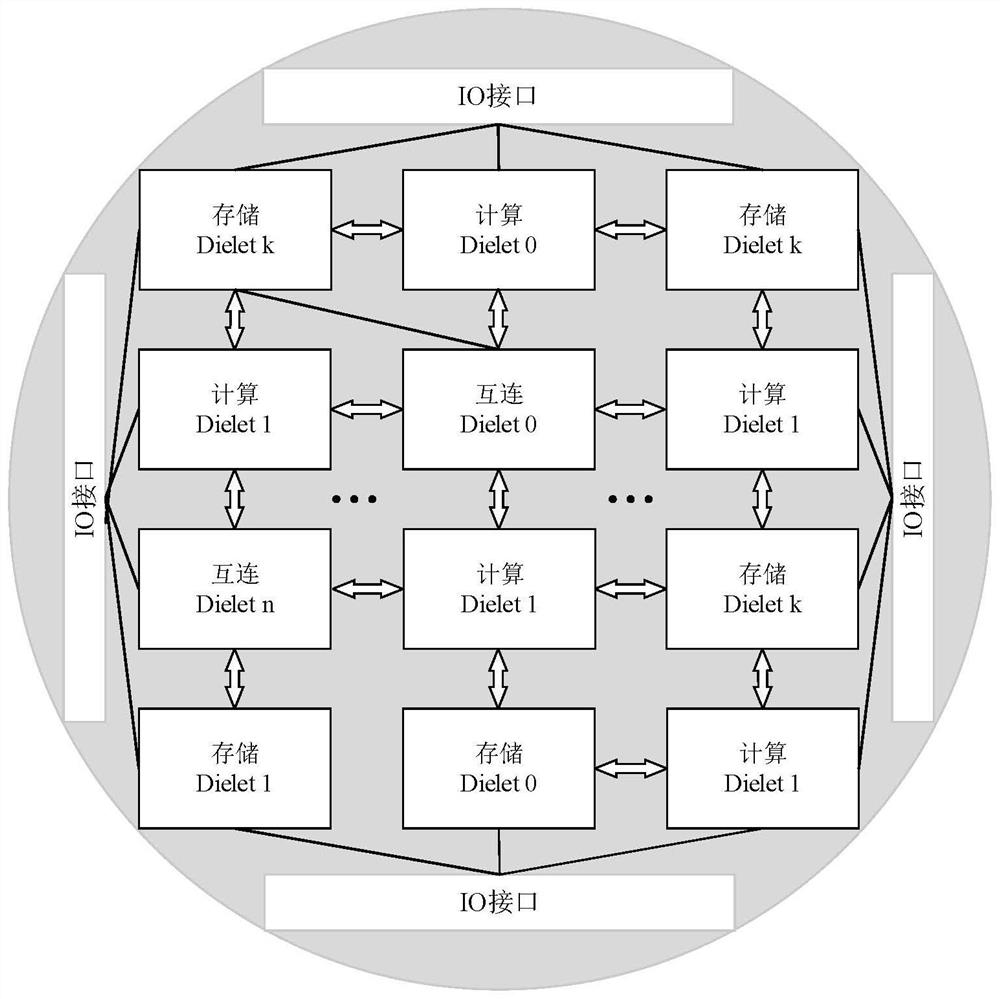

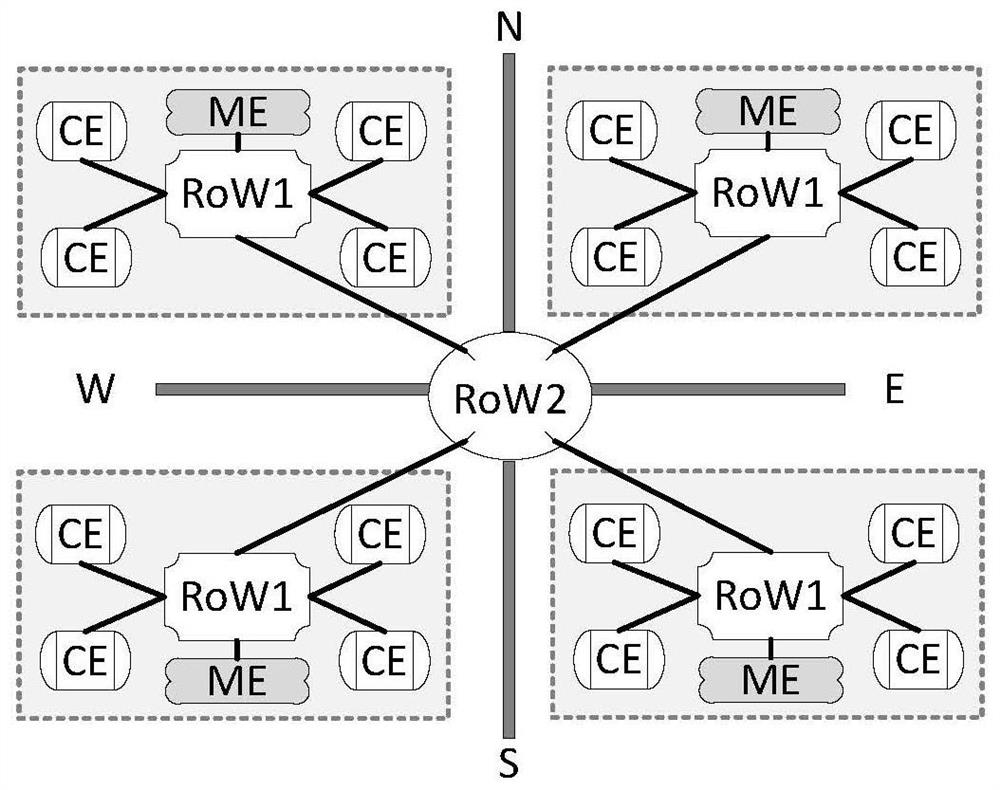

Software-on-chip defined interconnection network device and method

ActiveCN112562767AHighly integratedSimplified typesStatic storageComputer architectureInterconnection

The invention provides a software-on-chip defined interconnection network device and method. The device comprises a silicon substrate and a system-on-chip network arranged on the silicon substrate, nodes in the system-on-chip network comprise a computing node, a storage node and a network node, and the network node comprises an on-chip routing device, each node in the system-on-chip network beinginterconnected through the routing-on-chip device. The method comprises the following steps: performing cluster division on nodes in a system-on-chip network, each cluster comprising a computing node,a storage node and an on-chip routing device; and the components are connected by adopting a software-defined interconnection structure. According to the invention, the integration level of the wafer-level integrated system can be increased, the flexibility is improved, the fault-tolerant capability is improved, and the application scene is expanded.

Owner:CHINA NAT DIGITAL SWITCHING SYST ENG & TECHCAL R&D CENT +1

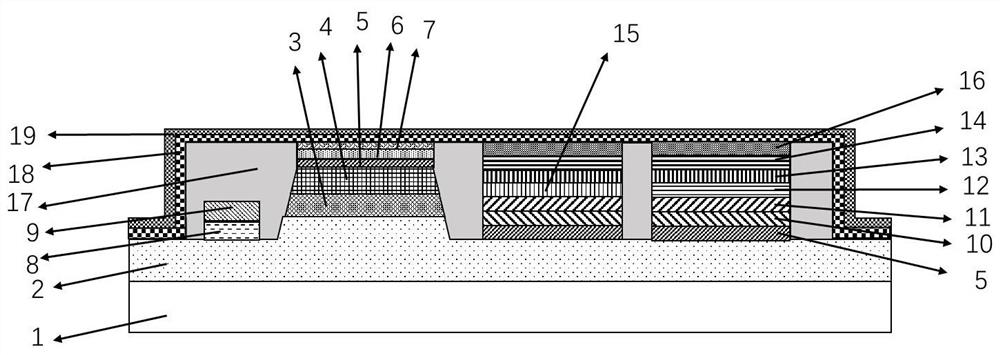

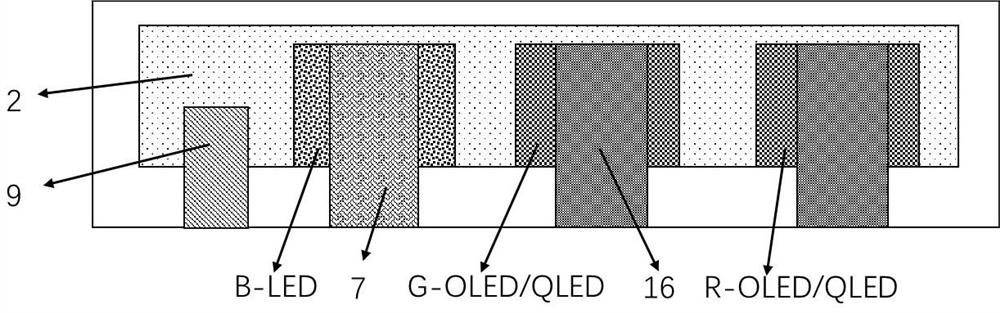

Integrally packaged micro-display chip and preparation method thereof

PendingCN113299678AImprove transfer yieldImprove convenienceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringGreen-light

The invention relates to an integrated packaging micro display chip, and the chip is characterized in that the chip comprises a substrate, a blue light Micro-LED sub-pixel, a red light Micro-OLED or Micro-QLED sub-pixel and a red light Micro-OLED or Micro-QLED sub-pixel; an n electrode of the Micro-LED sub-pixel is connected with one electrode of the Micro-OLED or the Micro-QLED, and a p electrode of the Micro-LED sub-pixel, the other electrode of the red light Micro-OLED or the Micro-QLED and the other electrode of the green light Micro-OLED or the Micro-QLED are respectively led out to form four leading-out electrodes of the integrated packaging micro-display chip. According to the invention, a blue light Micro-LED sub-pixel, a red light Micro-OLED or Micro-QLED sub-pixel, and a green light Micro-OLED or Micro-QLED sub-pixel are combined, and a micro-display pixel chip with a larger size and controllable luminescence of three primary colors is formed through wafer-level integration and packaging.

Owner:FUZHOU UNIV +1

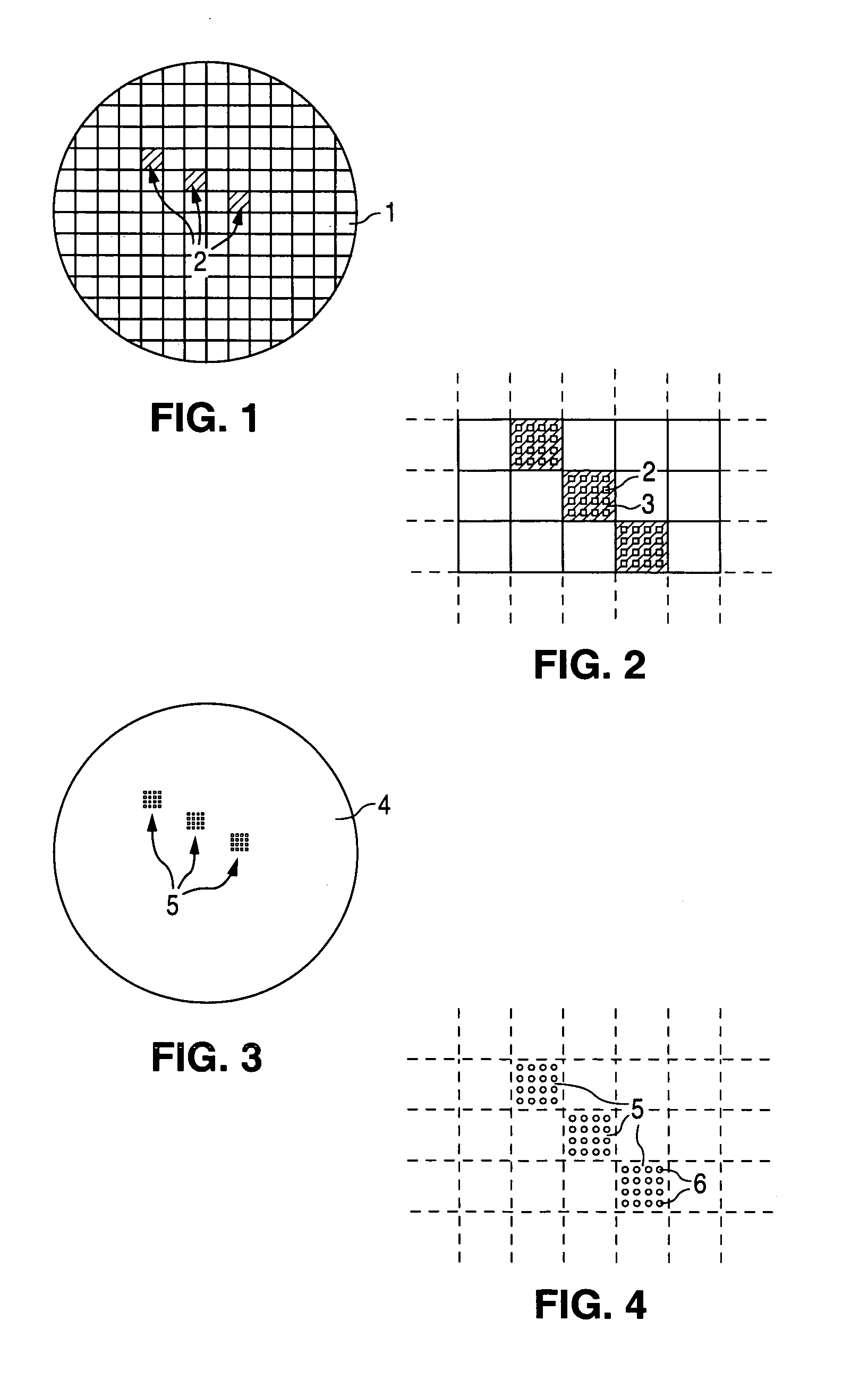

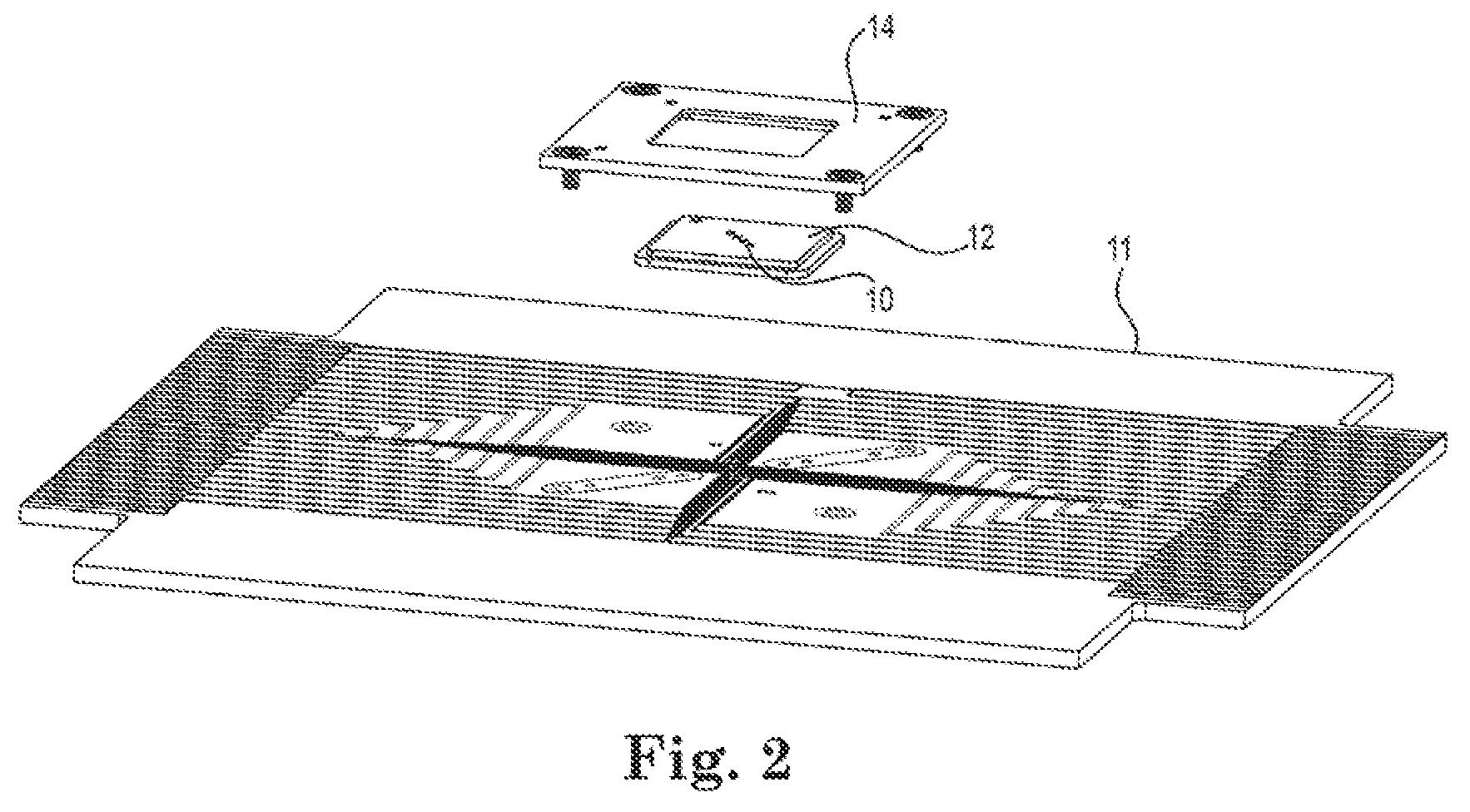

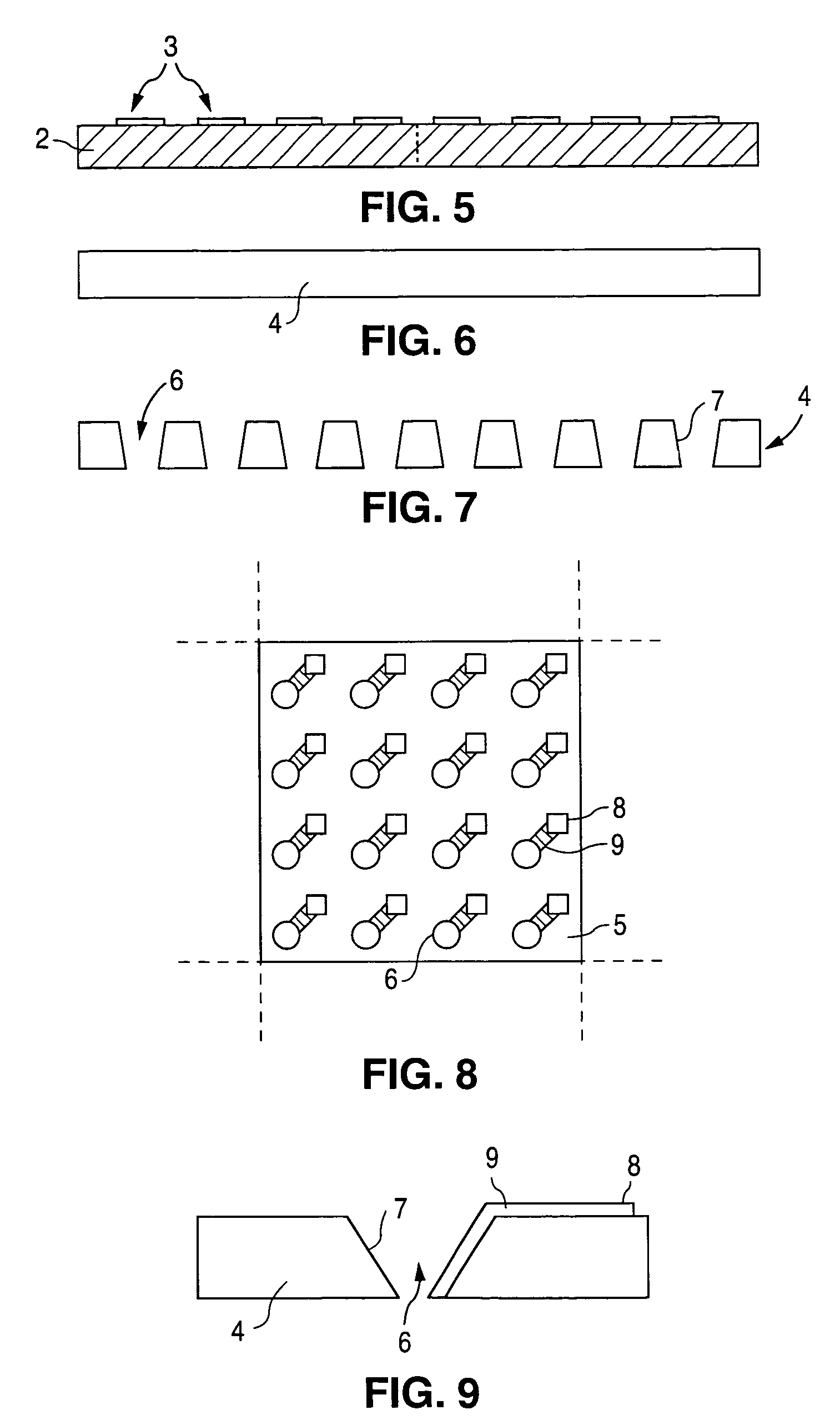

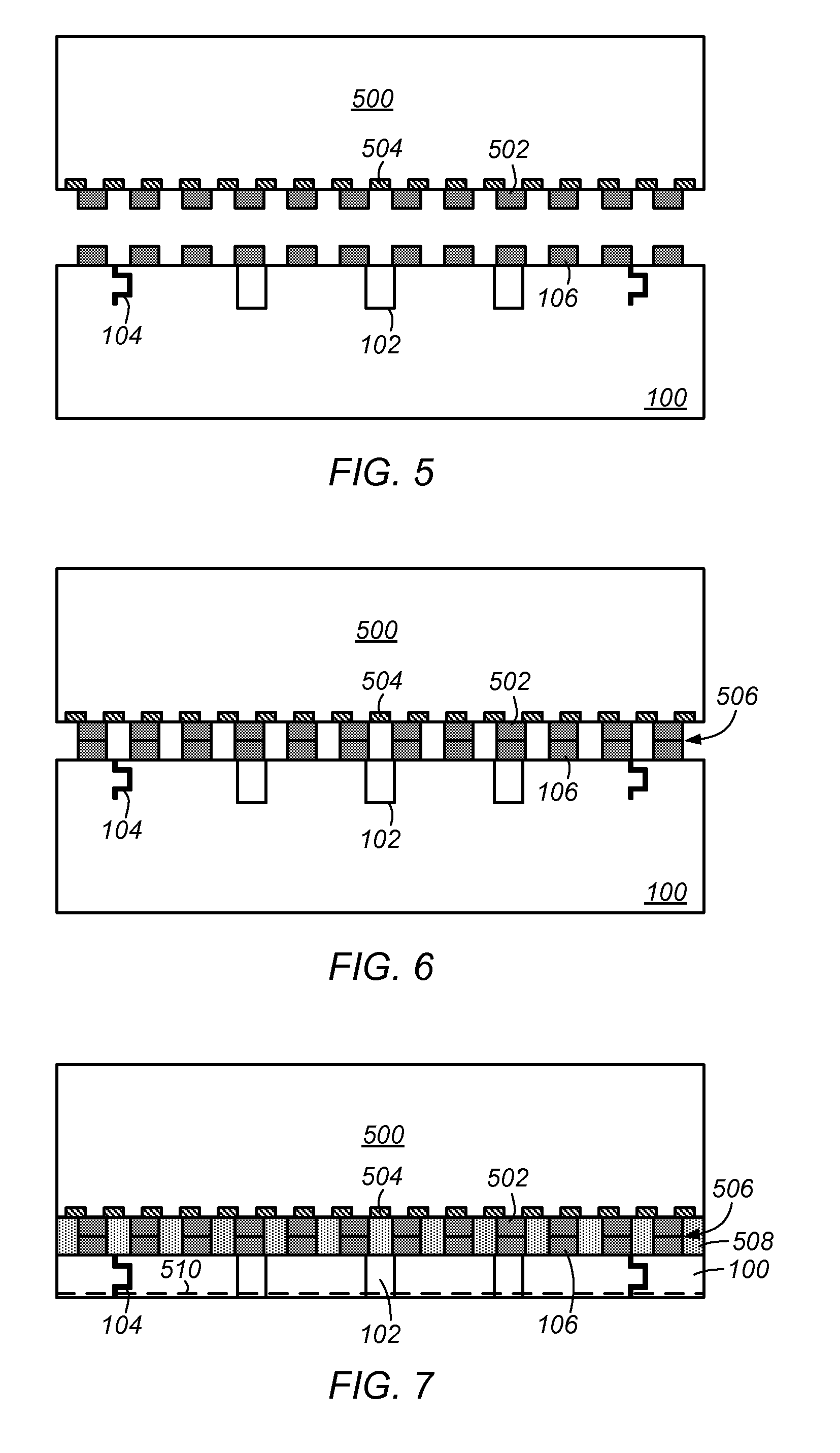

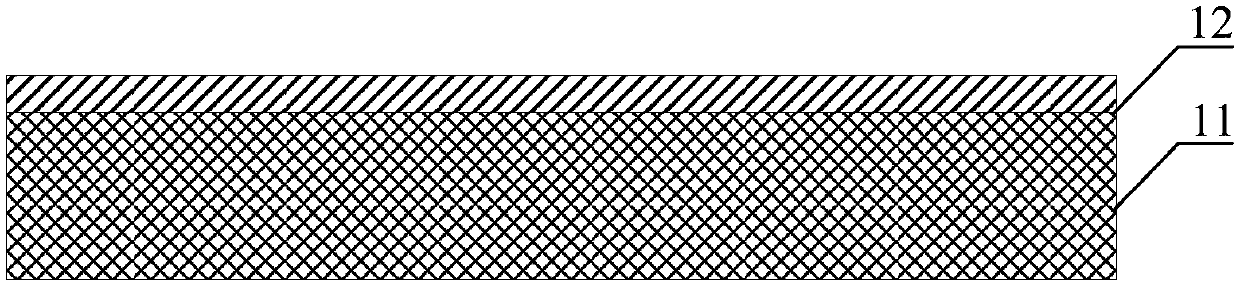

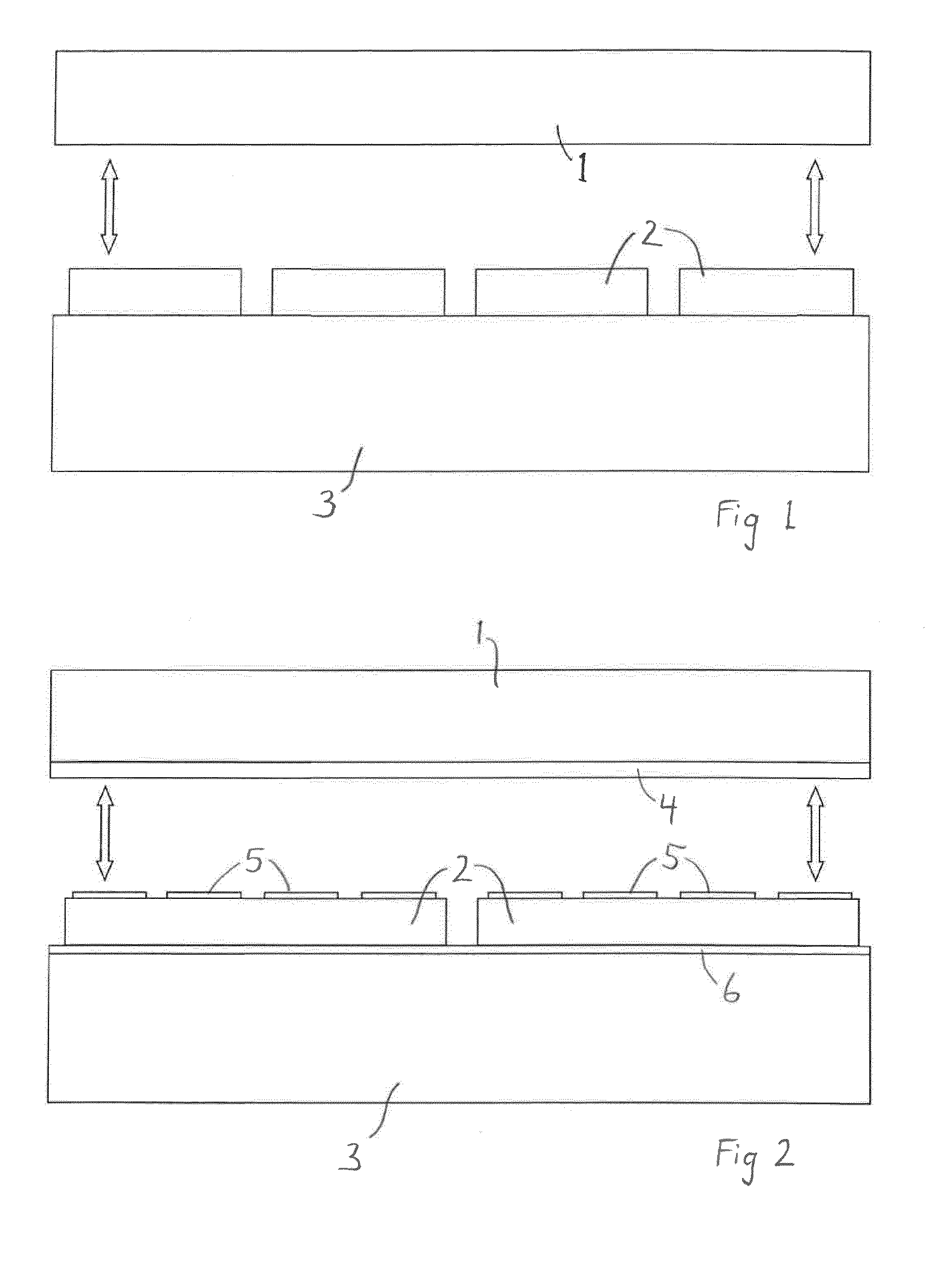

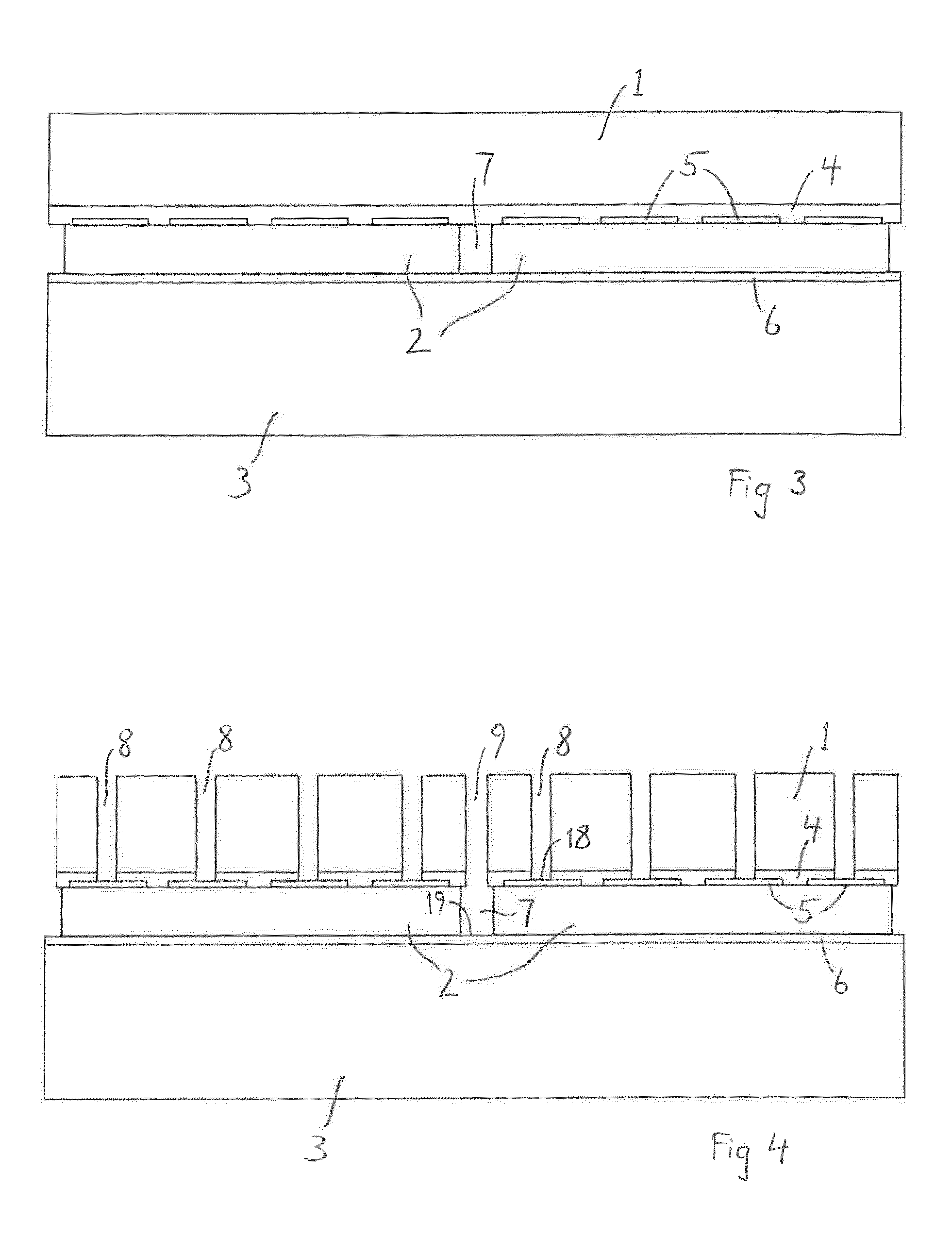

Method of wafer-scale integration of semiconductor devices and semiconductor device

ActiveUS20150129999A1Semiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor materials

The method of wafer-scale integration of semiconductor devices comprises the steps of providing a semiconductor wafer (1), a further semiconductor wafer (2), which differs from the first semiconductor wafer in at least one of diameter, thickness and semiconductor material, and a handling wafer (3), arranging the further semiconductor wafer on the handling wafer, and bonding the further semiconductor wafer to the semiconductor wafer. The semiconductor device may comprise an electrically conductive contact layer (6) arranged on the further semiconductor wafer (2) and a metal layer connecting the contact layer with an integrated circuit.

Owner:AMS AG

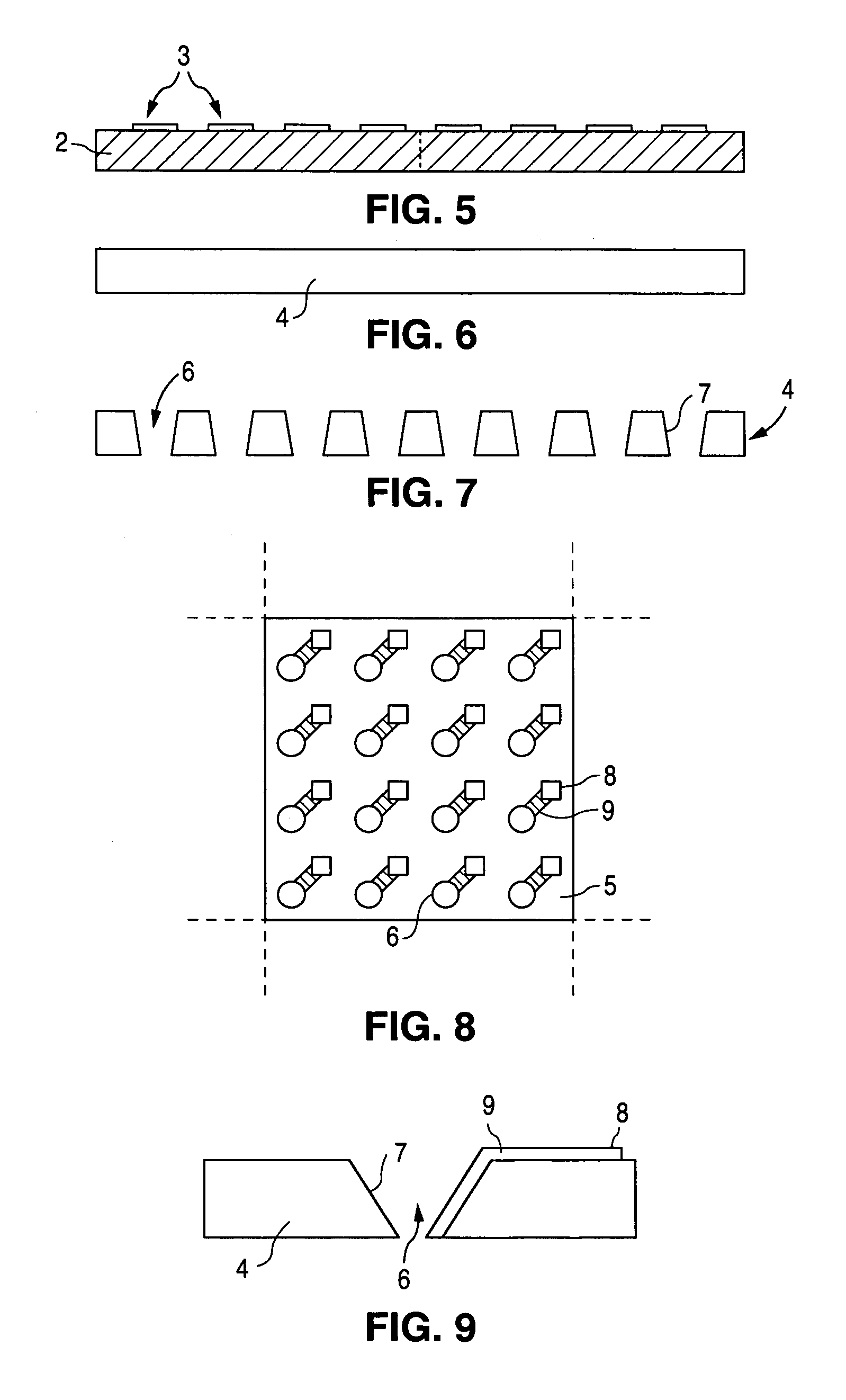

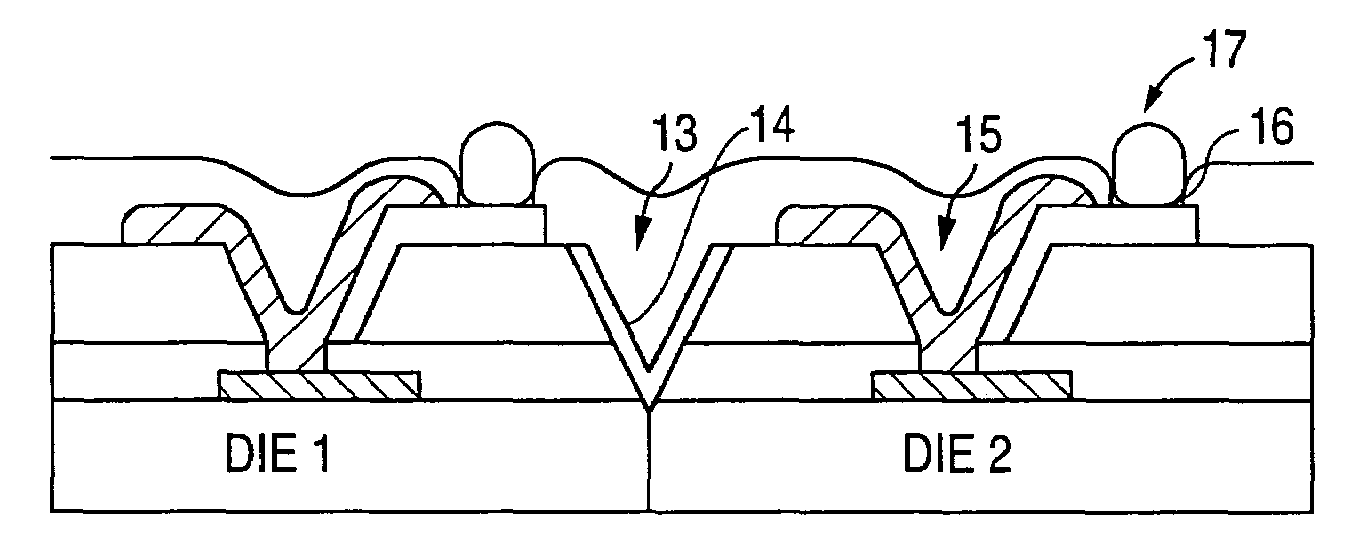

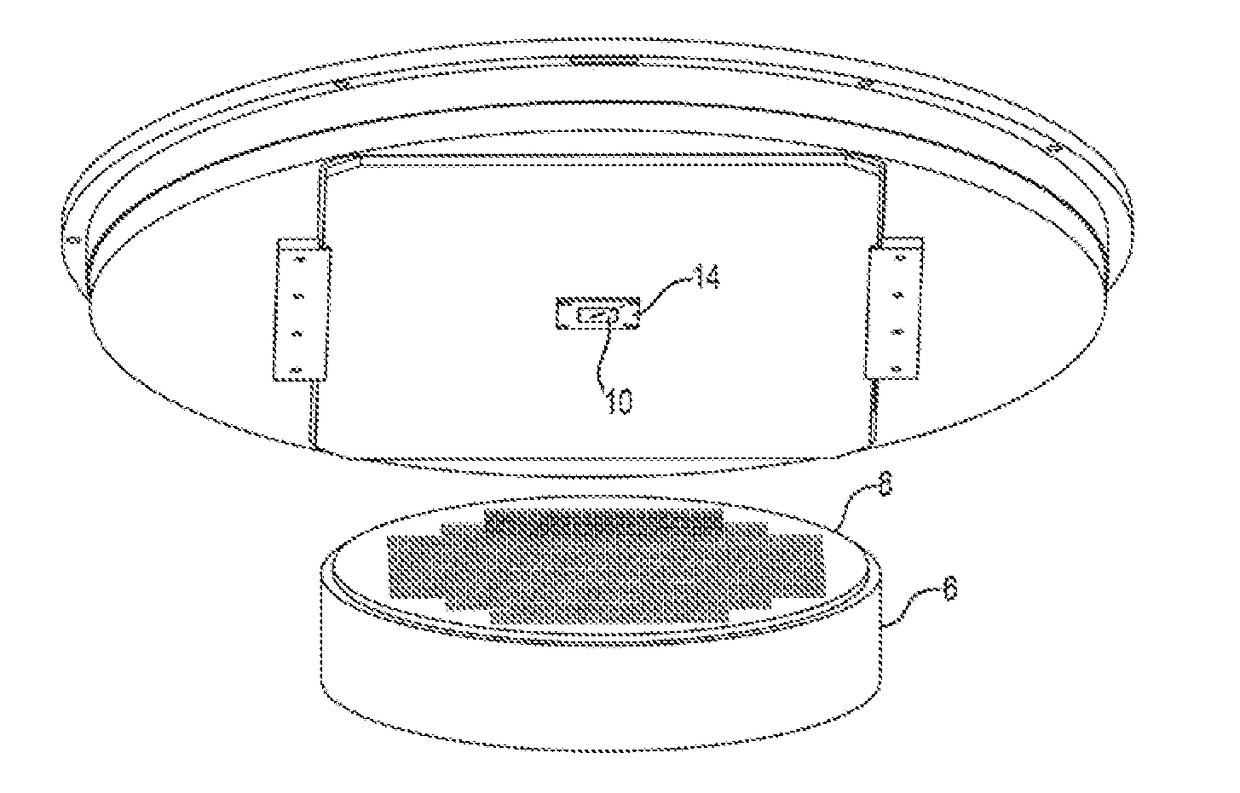

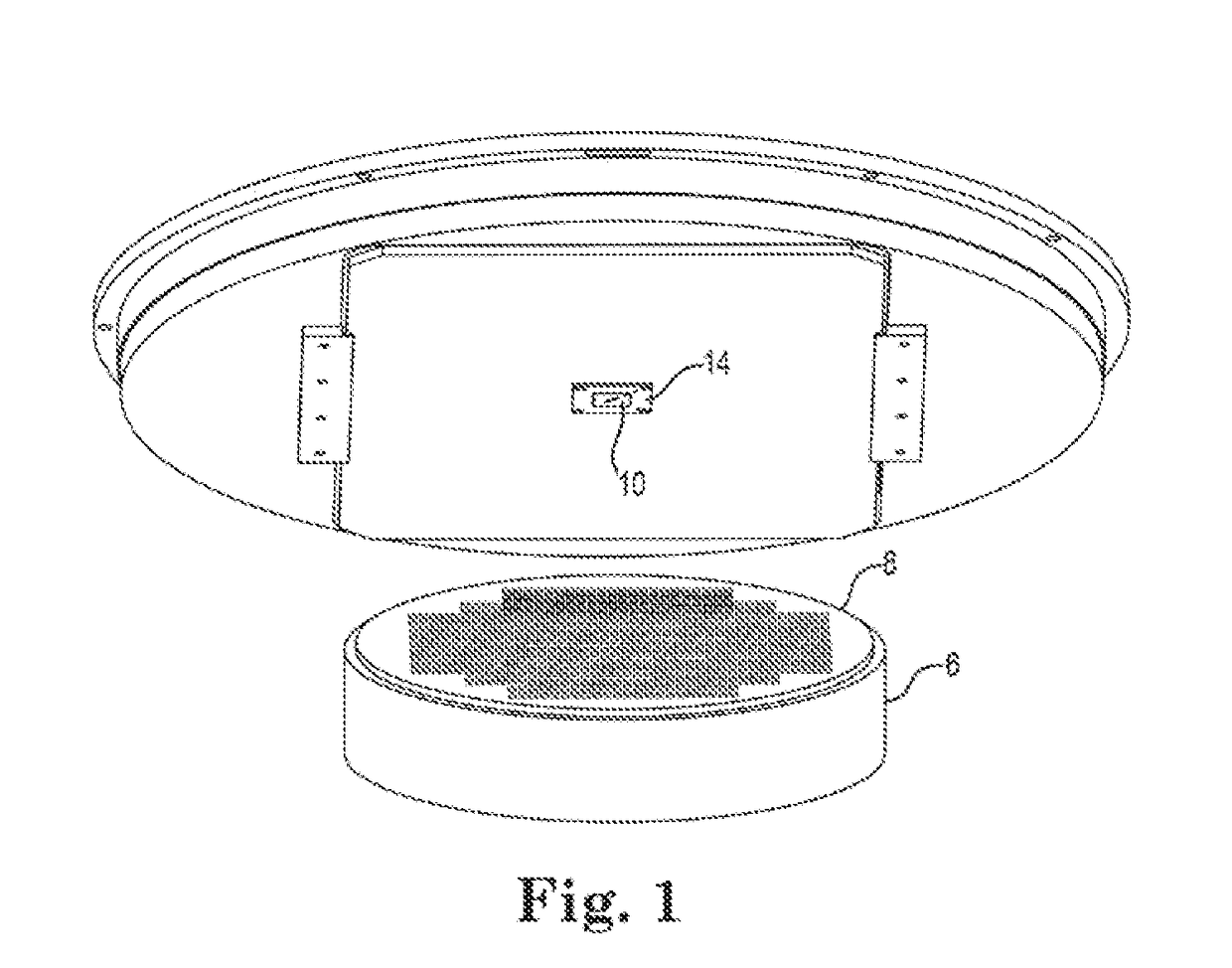

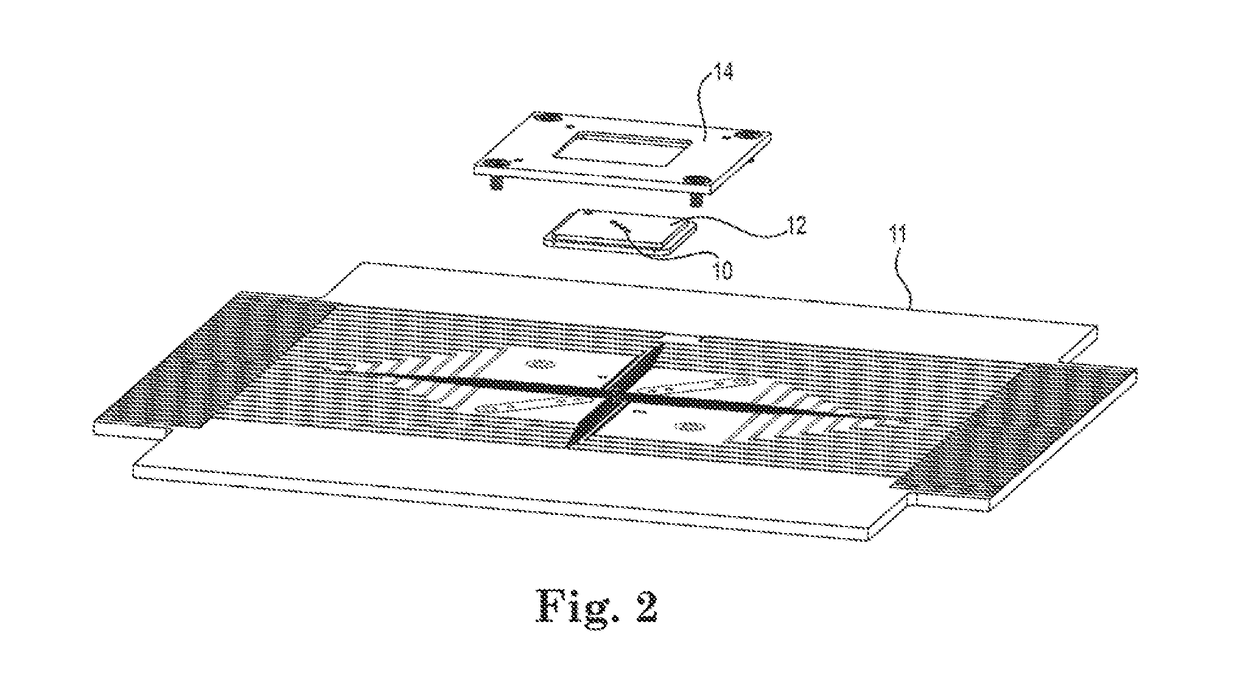

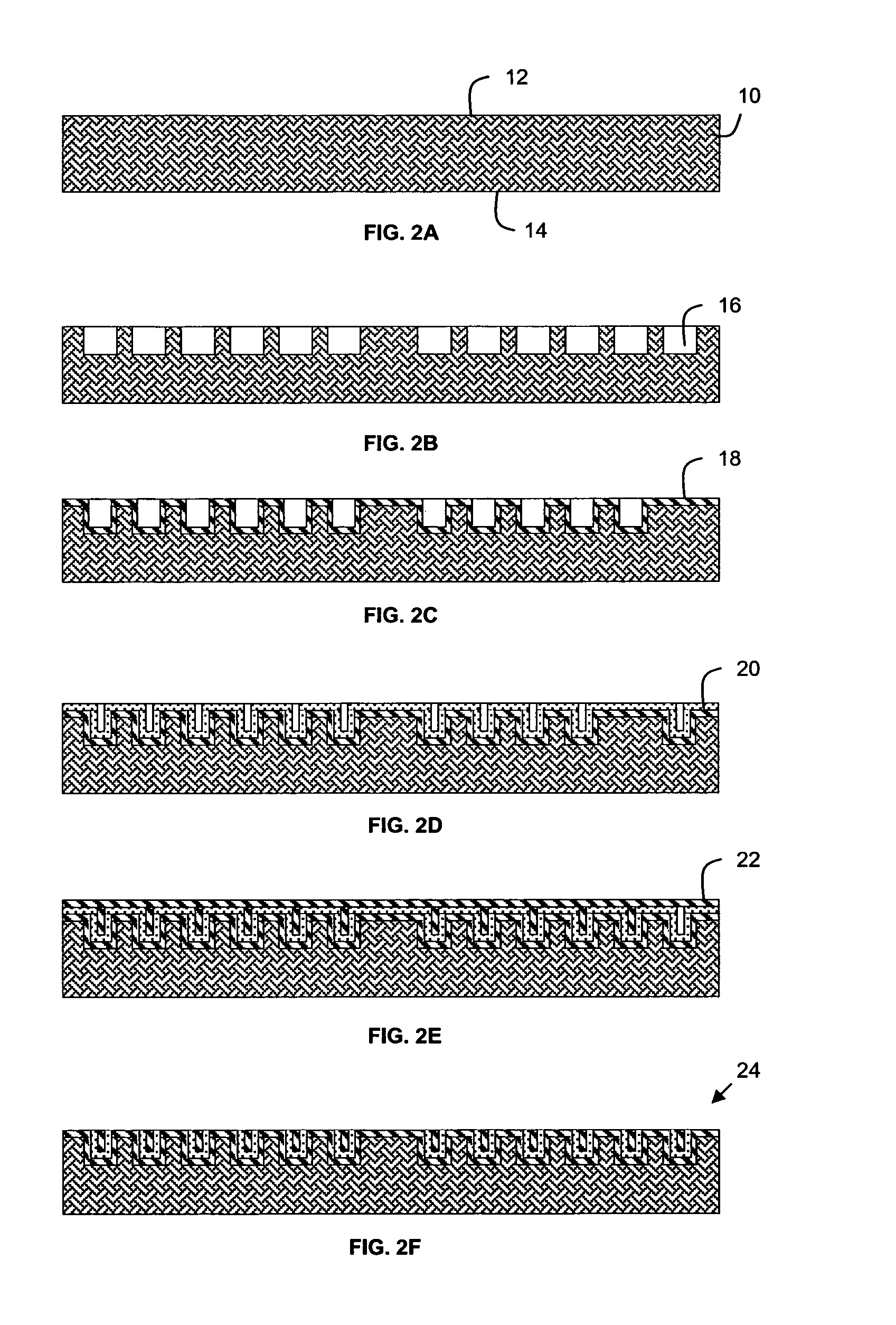

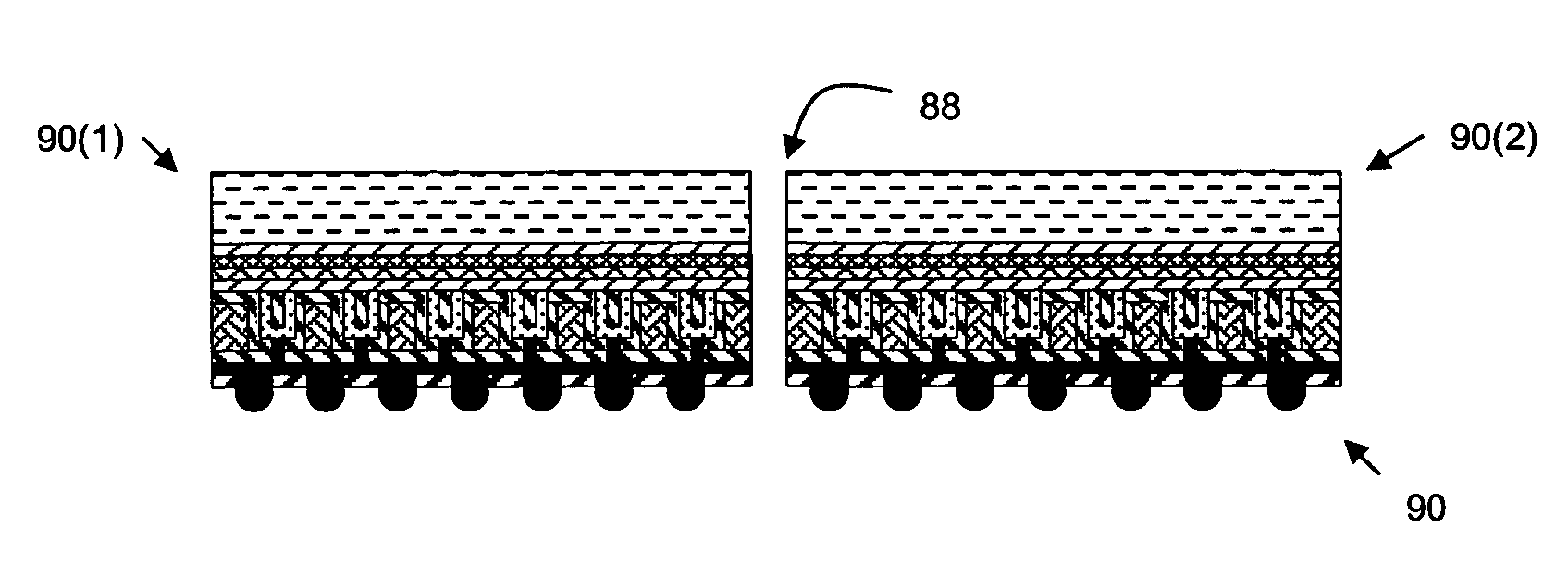

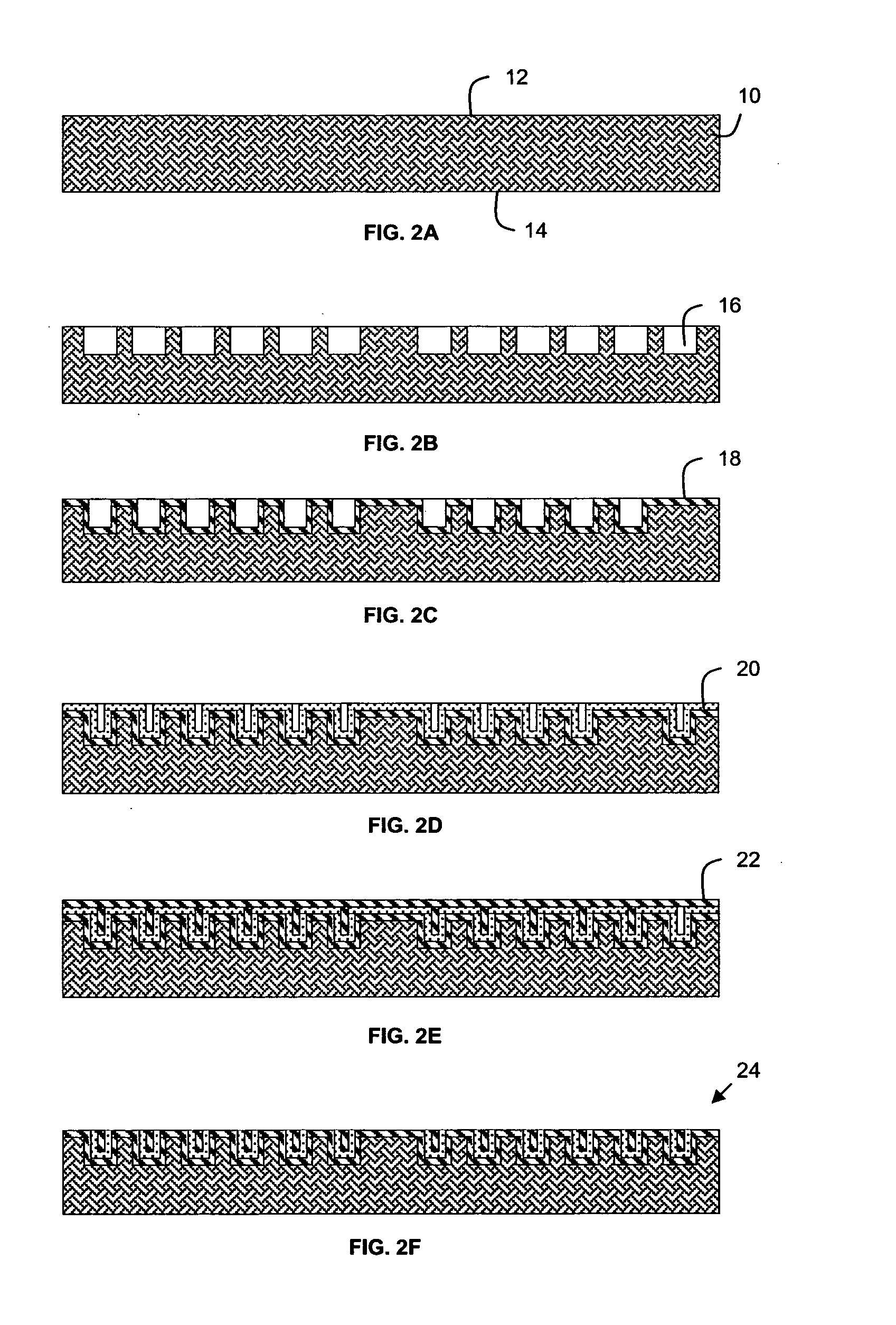

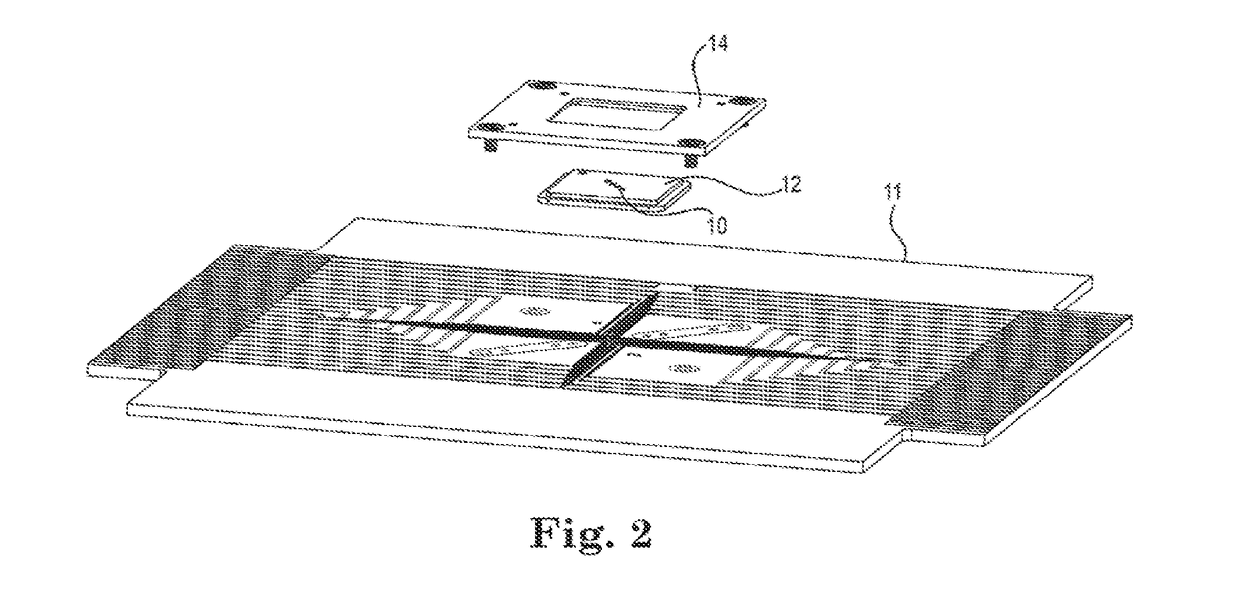

Wafer level integration module with interconnects

InactiveUS7998854B2Semiconductor/solid-state device testing/measurementSolid-state devicesWafer fabricationEngineering

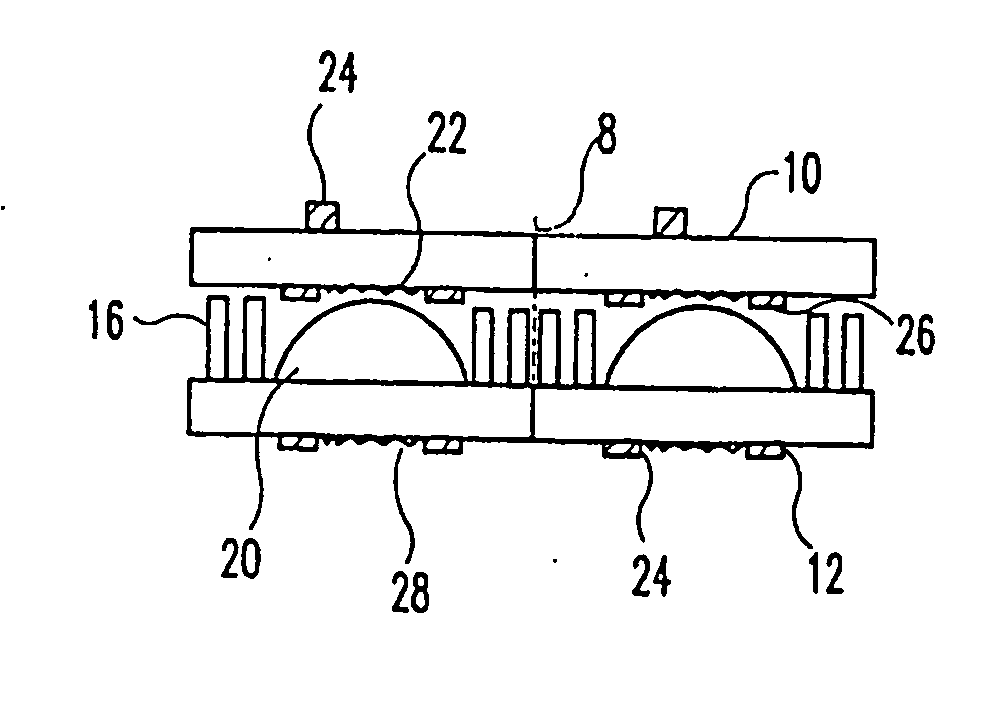

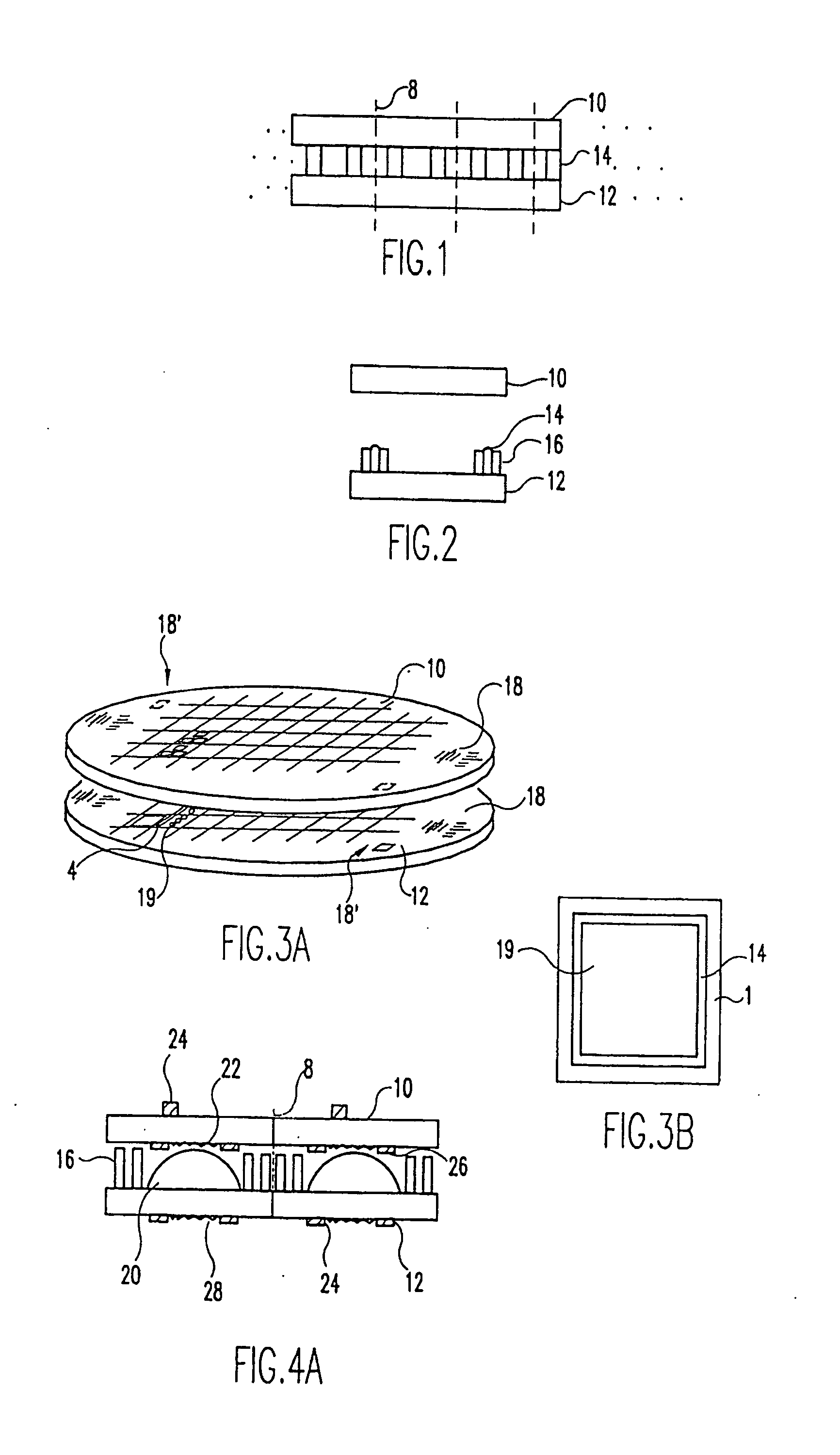

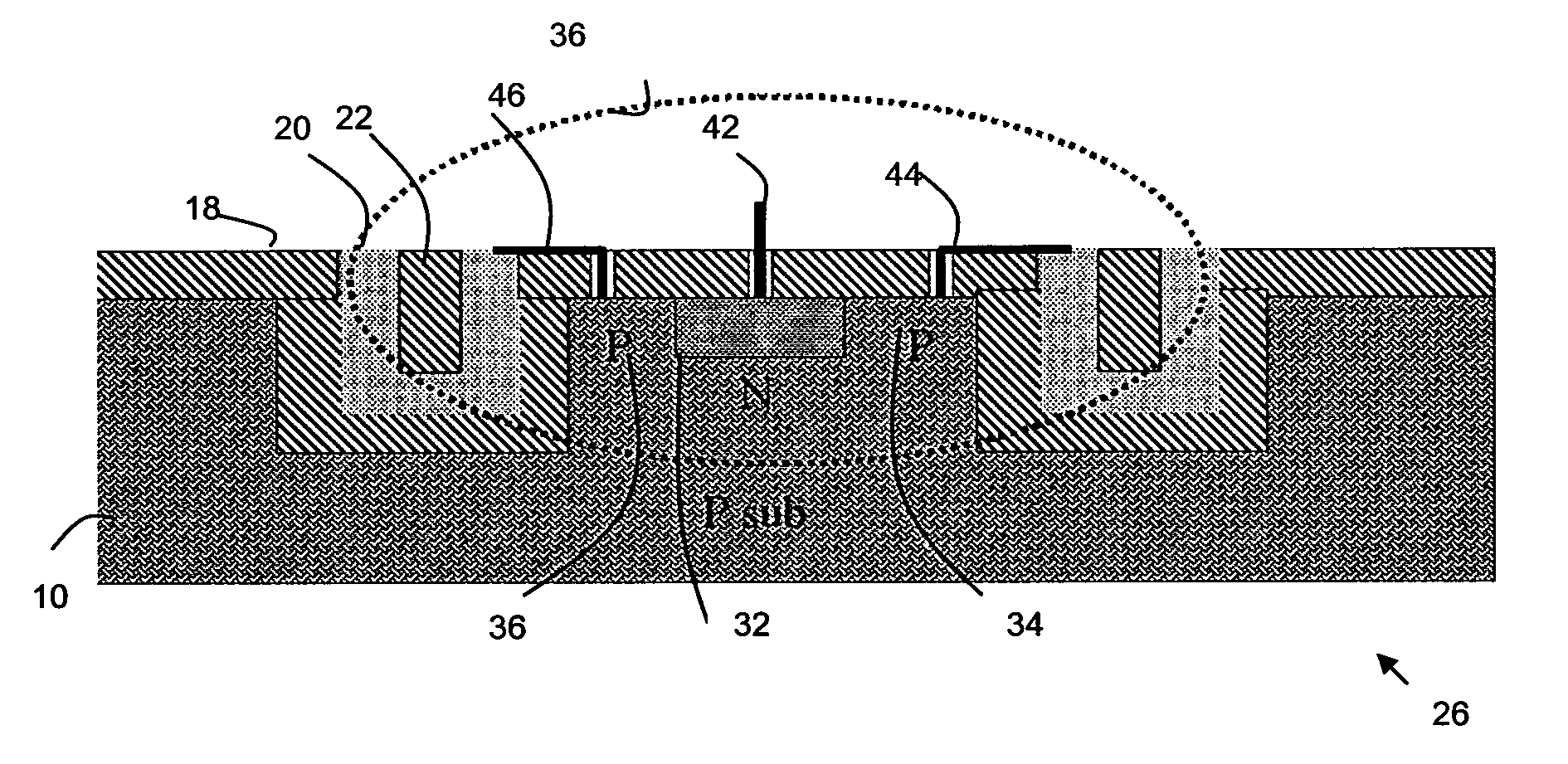

A method and apparatus for manufacturing an integrated circuit (IC) device (90) is disclosed. A wafer (10) is first provided having a first or top surface and a second or bottom surface. The wafer may be a blank polished or unpolished silicon wafer or the like. High aspect ratio micro-structures (16) that are specifically designed to provide a die level interconnect configuration and mapping, are provided on the first blank surface (12) of the wafer. The wafer with preformed conductive interconnect microstructures (16) are further processed for device fabrication, for example, at the wafer fabrication facilities. Once the front side (12) devices are fabricated, the silicon material (20) is then removed from a second side (14) of the device wafer (10), opposite the first side, to expose the high temperature conductive interconnect microstructures (16). Contacts are formed on the second side of the device wafer using conductive metal. These contacts are electrically connected to the interior of the microstructures and thereby electrically connect with the functional device (26). The dies (90(1)),(90(2)) are separated along the separation zones (88) between the dies to produce individualized functional and packaged dies, each of which serves as a fully packaged IC device (90).

Owner:VISWANADAM GAUTHAM

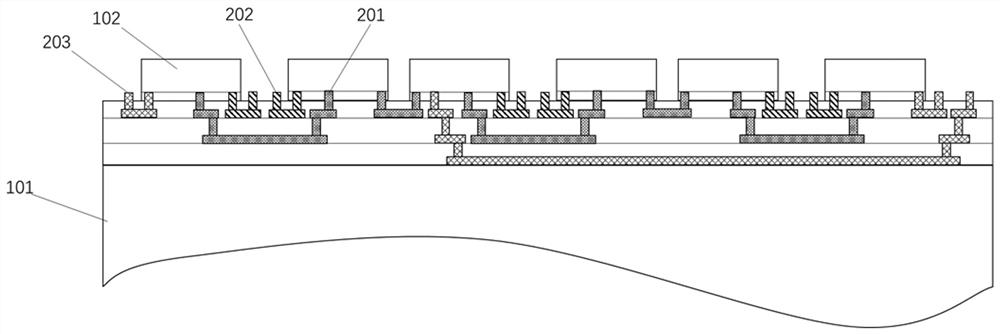

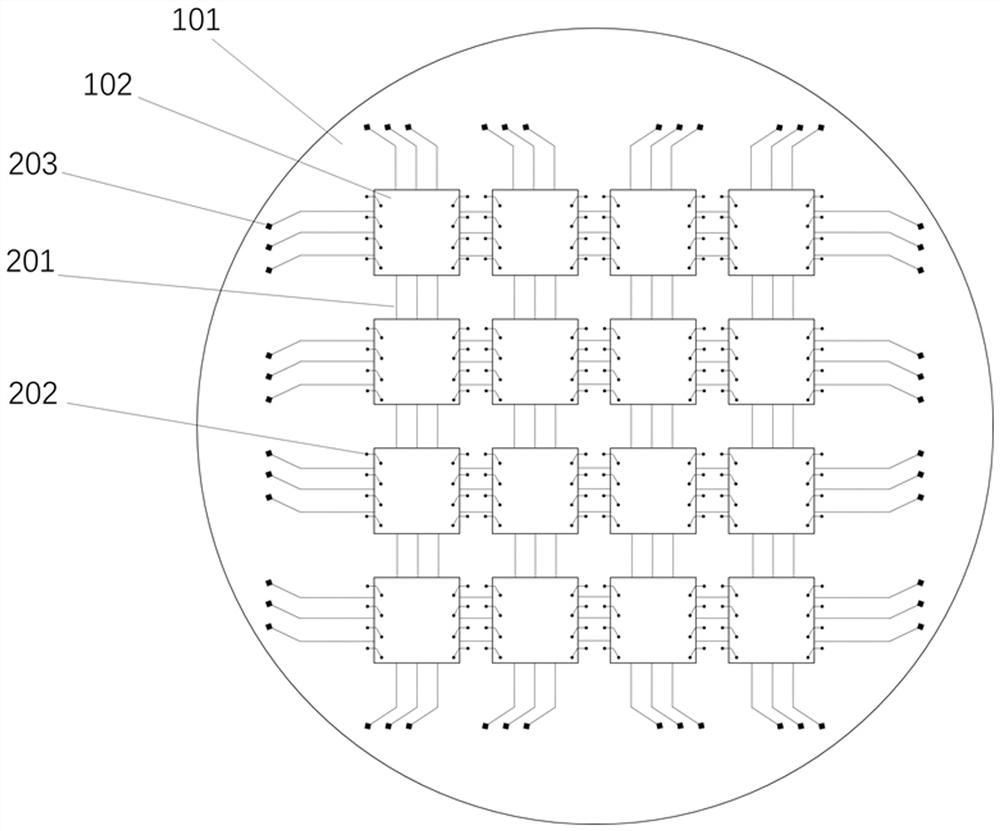

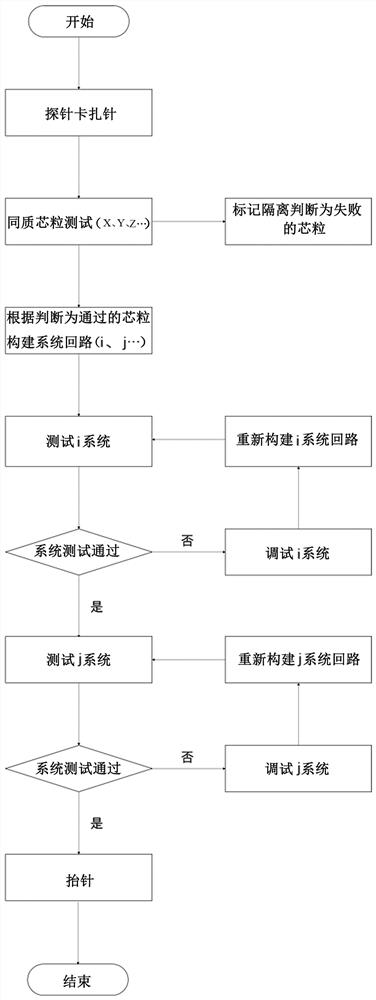

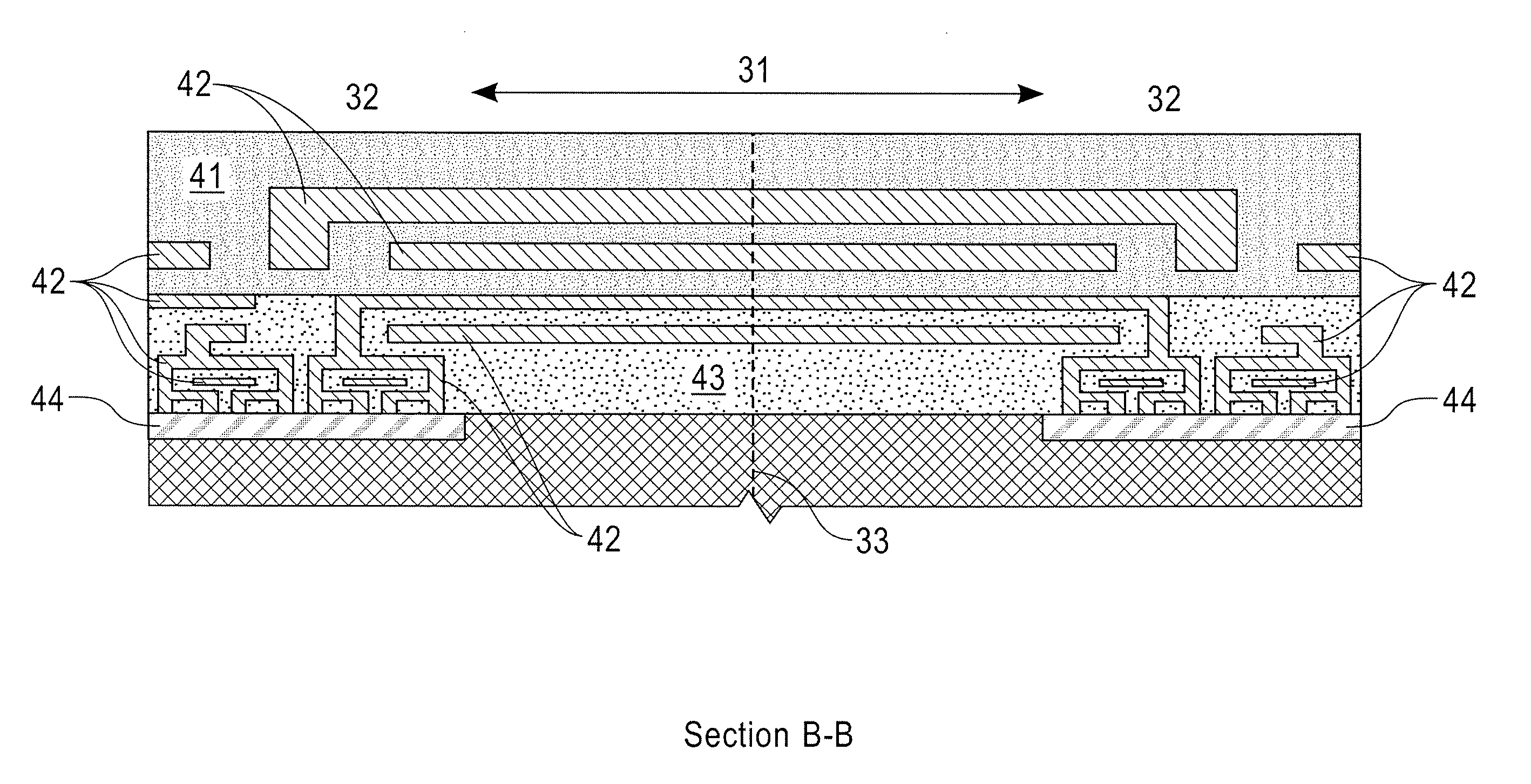

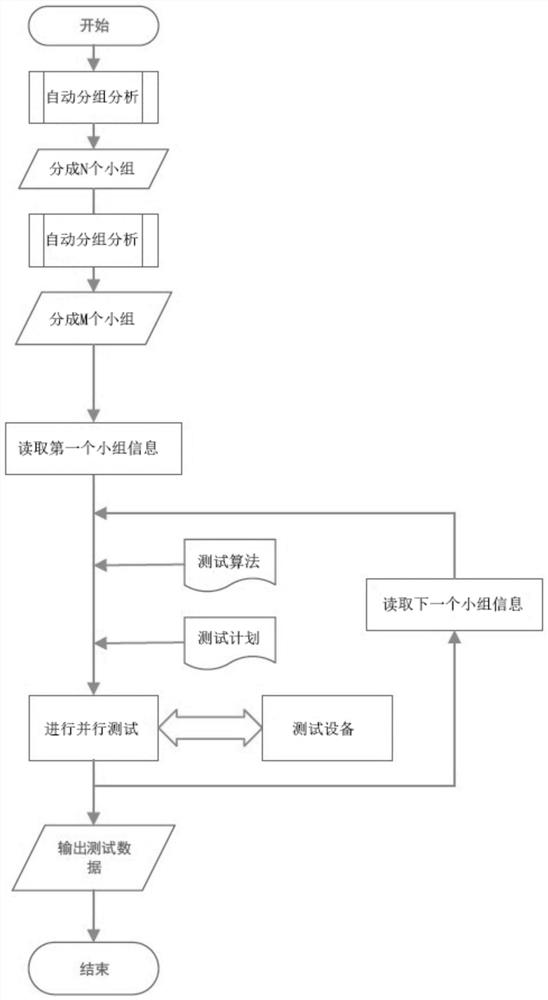

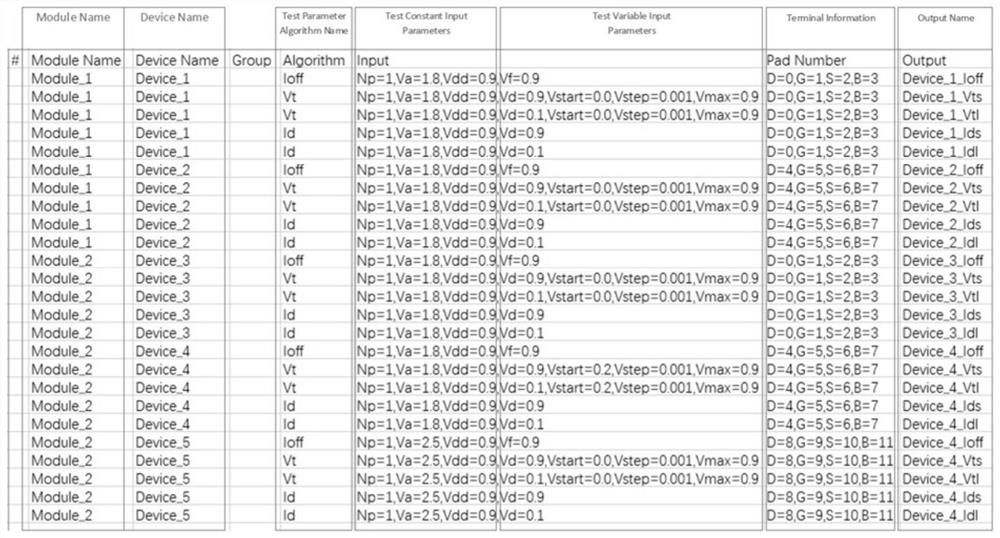

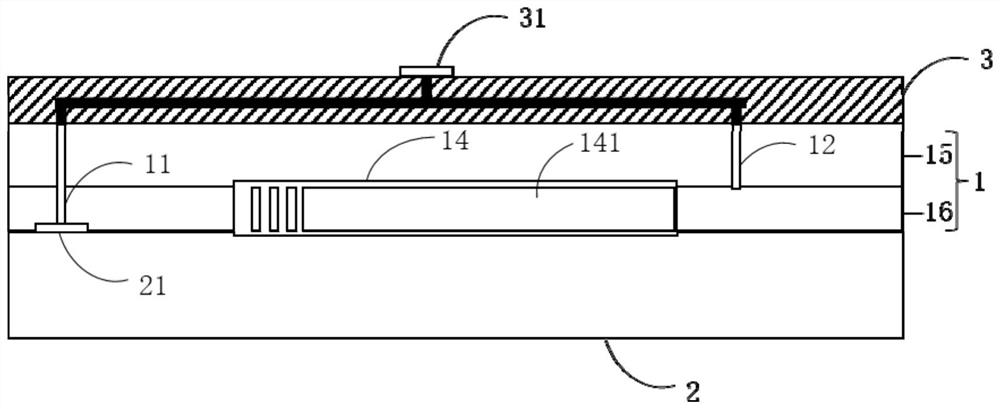

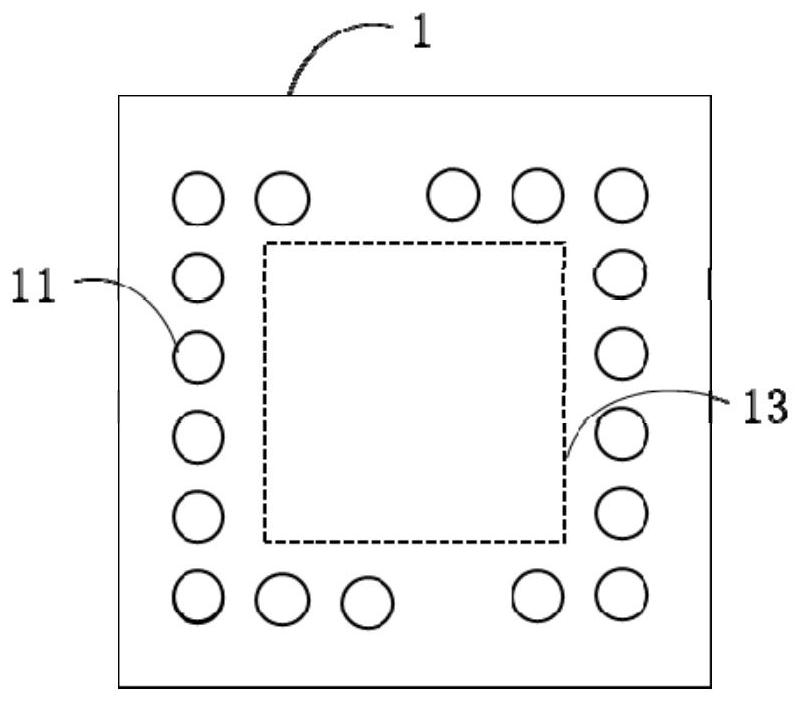

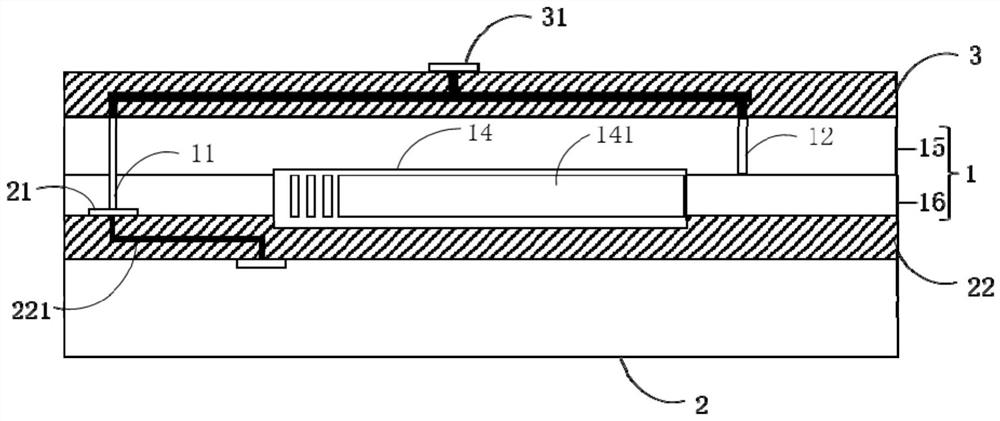

Test structure and test method of wafer-level integrated system

ActiveCN114843250AGuaranteed uptimeSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSystem testingHemt circuits

The invention discloses a test structure and a test method of a wafer-level integrated system. The test structure is composed of a wafer substrate, core particles bonded on a wafer, a core particle test circuit led out from the periphery of the core particles on the wafer, and a system test circuit led out to the periphery of the wafer through wafer interconnection. According to the testing method, testing of the integrated core particles and testing of the integrated system are achieved through one-time needle inserting. The method comprises the following steps: firstly, carrying out corresponding wafer-level chip testing on homogeneous core particles, after testing the failed core particles, entering a next type of homogeneous core particle testing, and after testing all the core particles, constructing a system link according to the tested core particles, and carrying out system-level testing on a wafer-level integrated system. According to the invention, the test of the bonded core particles and the test of the on-chip integrated system can be completed through one-time needle insertion, the invalid core particles can be screened out through the core particle test, and the system-level test can ensure the correctness of a system link and the reliable operation of the whole on-chip system.

Owner:ZHEJIANG LAB

Supercomputer using wafer scale integration

ActiveUS9568960B2Unacceptable stressSemiconductor/solid-state device detailsSolid-state devicesElectricitySupercomputer

A semiconductor structure includes a substrate with cooling layers, cooling channels, coolant inlets and outlets in fluid communication with the cooling channels, and a device layer on the cooling layers with one or more connection points and a device layer area. The device layer thermal coefficient of expansion is substantially equal to that of the cooling layers. A plurality of laminate substrates are disposed on, and electrically attached to, the device layer. The laminate substrate thermal coefficient of expansion differs from that of the device layer, each laminate substrate is smaller than the device layer portion to which it is attached, and each laminate substrate includes gaps between sides of adjacent laminate substrates. The laminate substrates are not electrically or mechanically connected to each other across the gaps therebetween and the laminate substrates are small enough to prevent warping of the device, interconnection and cooling layers due to thermal expansion.

Owner:INT BUSINESS MASCH CORP

Hybrid integration of edge-coupled chips

ActiveUS9618709B2Easy to separateCoupling light guidesOptical waveguide light guideManufacturing technologySemiconductor chip

A technique for fabricating a hybrid optical source is described. During this fabrication technique, a III-V compound-semiconductor active gain medium is integrated with a silicon-on-insulator (SOI) chip (or wafer) using edge coupling to form a co-planar hybrid optical source. Using a backside etch-assisted cleaving technique, and a temporary transparent substrate with alignment markers, a III-V compound-semiconductor chip with proper edge polish and coating can be integrated with a processed SOI chip (or wafer) with accurate alignment. This fabrication technique may significantly reduce the alignment complexity when fabricating the hybrid optical source, and may enable wafer-scale integration.

Owner:ORACLE INT CORP

Wafer level integration module with interconnects

InactiveUS20110065215A1Semiconductor/solid-state device testing/measurementSolid-state devicesWafer fabricationSilicon

A method and apparatus for manufacturing an integrated circuit (IC) device (90) is disclosed. A wafer (10) is first provided having a first or top surface and a second or bottom surface. The wafer may be a blank polished or unpolished silicon wafer or the like. High aspect ratio micro-structures (16) that are specifically designed to provide a die level interconnect configuration and mapping, are provided on the first blank surface (12) of the wafer. The wafer with preformed conductive interconnect microstructures (16) are further processed for device fabrication, for example, at the wafer fabrication facilities. Once the front side (12) devices are fabricated, the silicon material (20) is then removed from a second side (14) of the device wafer (10), opposite the first side, to expose the high temperature conductive interconnect microstructures (16). Contacts are formed on the second side of the device wafer using conductive metal. These contacts are electrically connected to the interior of the microstructures and thereby electrically connect with the functional device (26). The dies (90(1)),(90(2)) are separated along the separation zones (88) between the dies to produce individualized functional and packaged dies, each of which serves as a fully packaged IC device (90).

Owner:VISWANADAM GAUTHAM

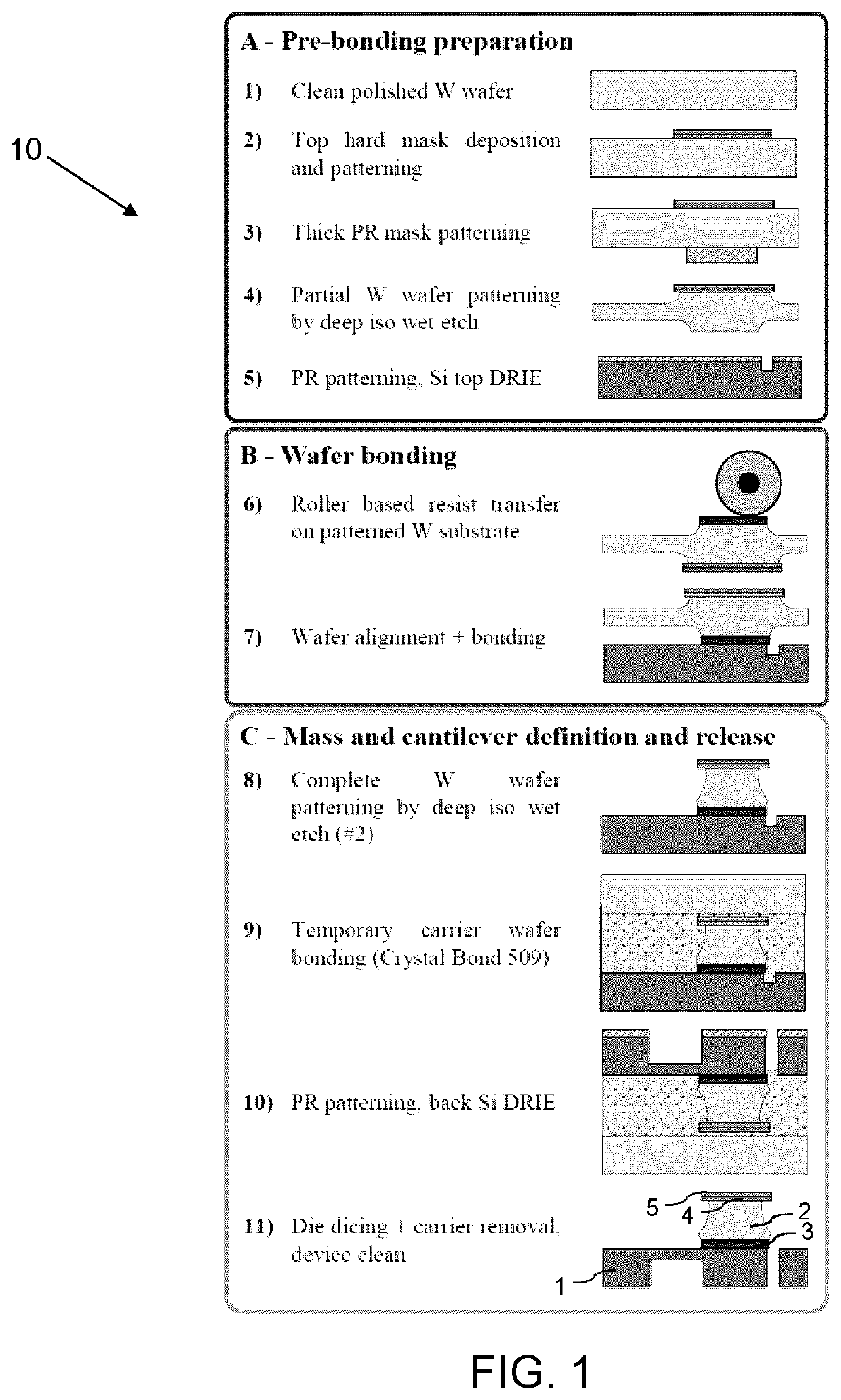

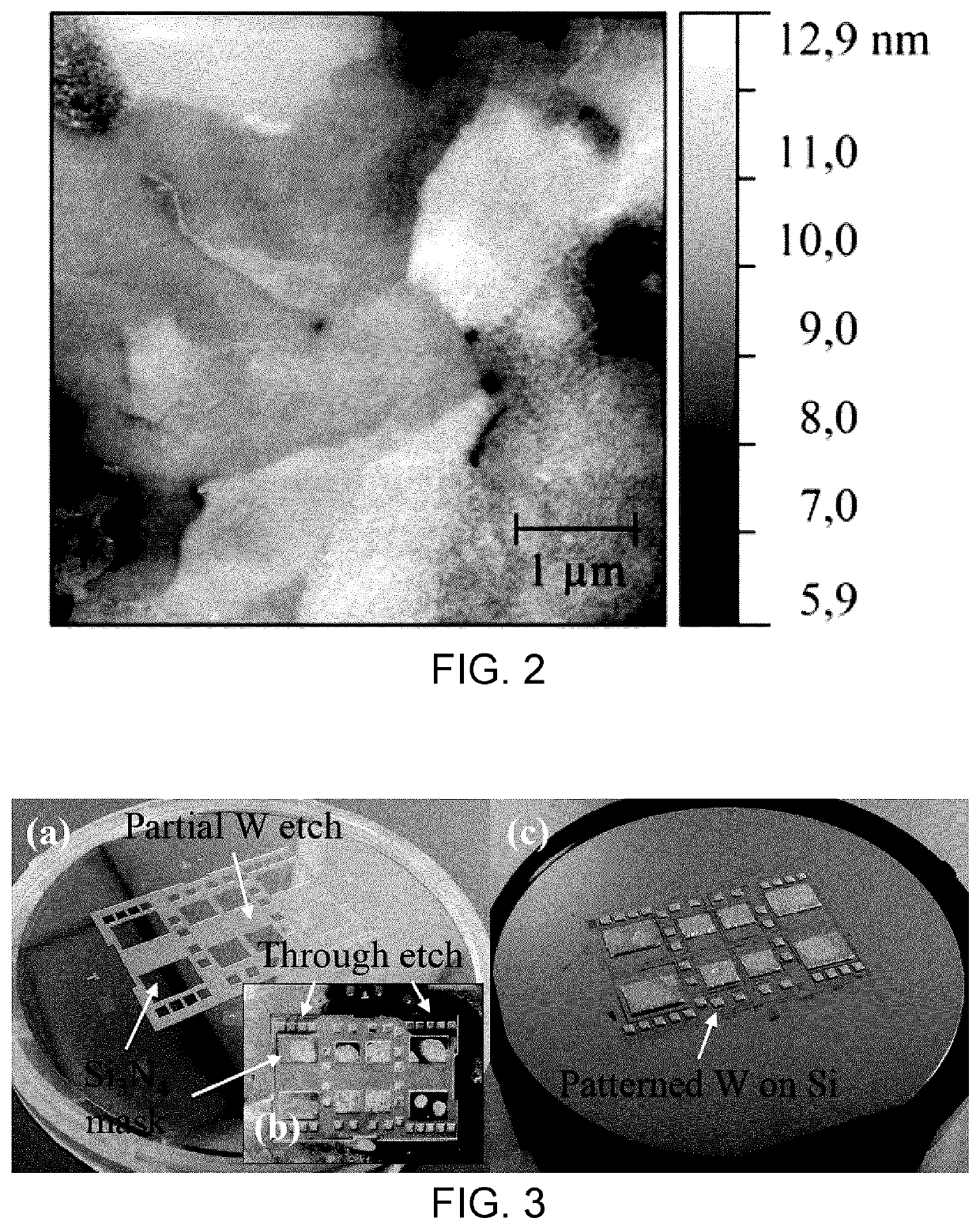

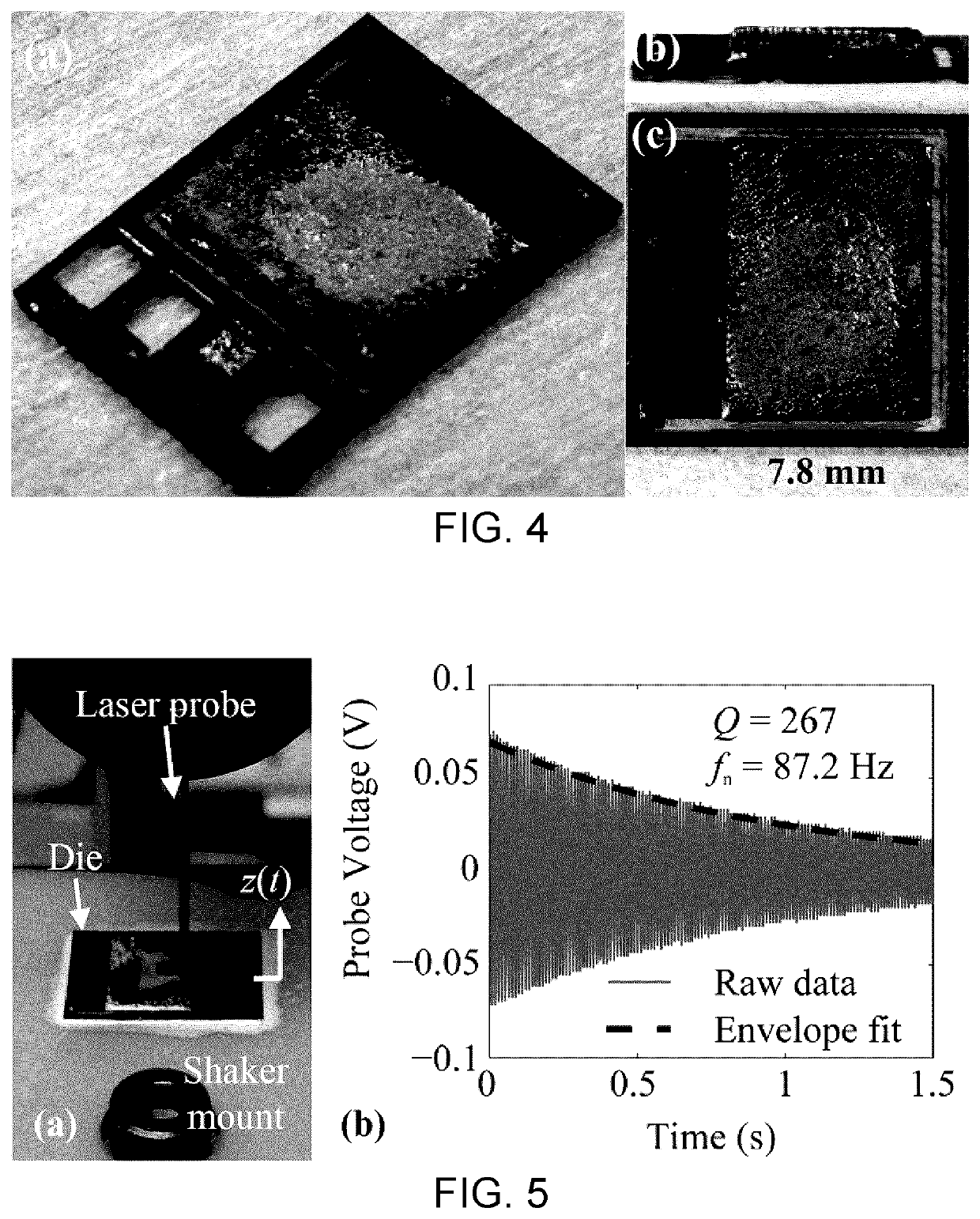

Inertial devices with wafer-level integration of higher density proof masses and method of manufacturing

InactiveUS20210140767A1High density proof massAcceleration measurement using interia forcesSpeed measurement using gyroscopic effectsCantilevered beamWafering

An inertial device comprises a frame. A cantilever beam has a first end connected to the frame and a second end cantilevered relative to the frame, the cantilevered beam forming a spring portion between the first end and the second end, the cantilever beam having a support surface defining a support area. The frame and the cantilever beam are made from a support wafer, the support wafer being made of silicon, a thickness of the support wafer at the support area ranging between 0 μm and 800 μm. A mass bonded to the support surface of the silicon wafer at the support area, the mass being made of tungsten, a thickness of the mass being of at least 20 μm.

Owner:SCOPRA SCI & GENIE SEC

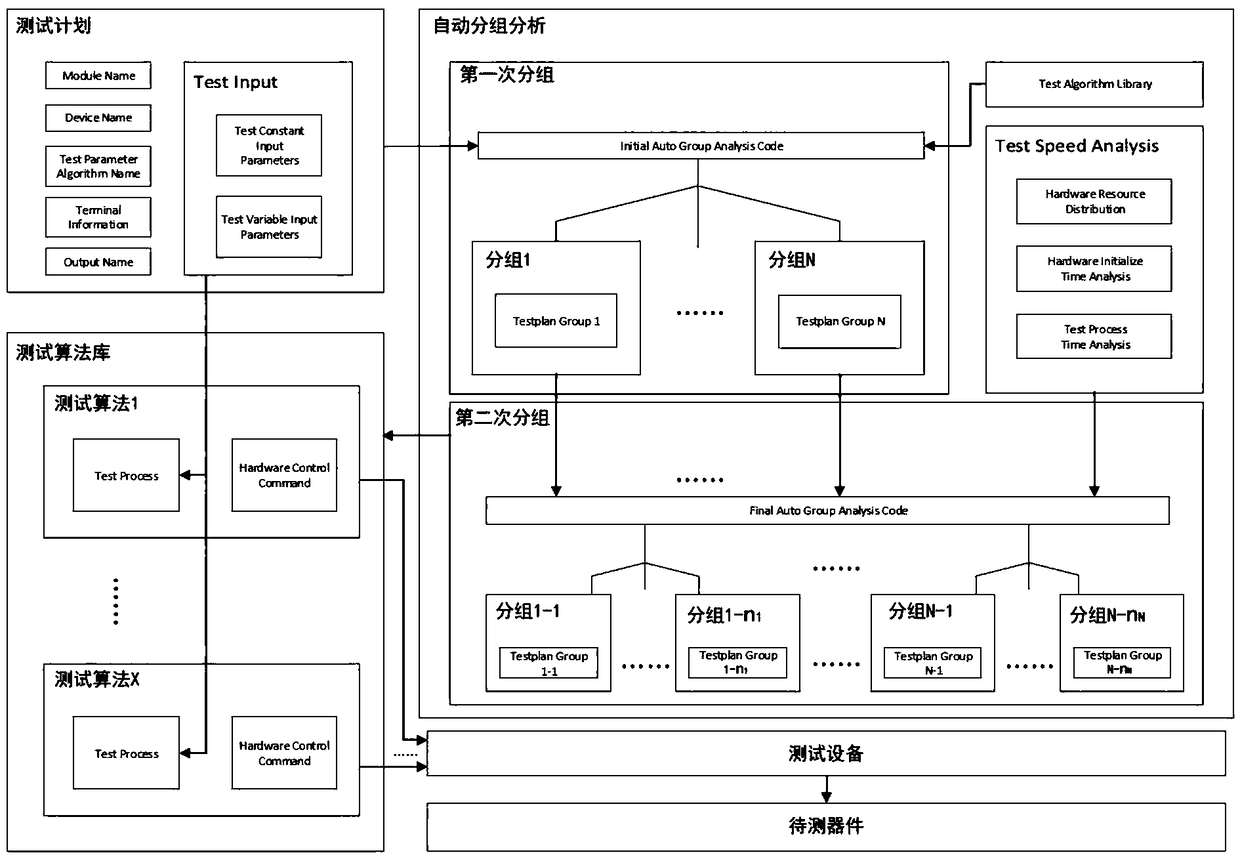

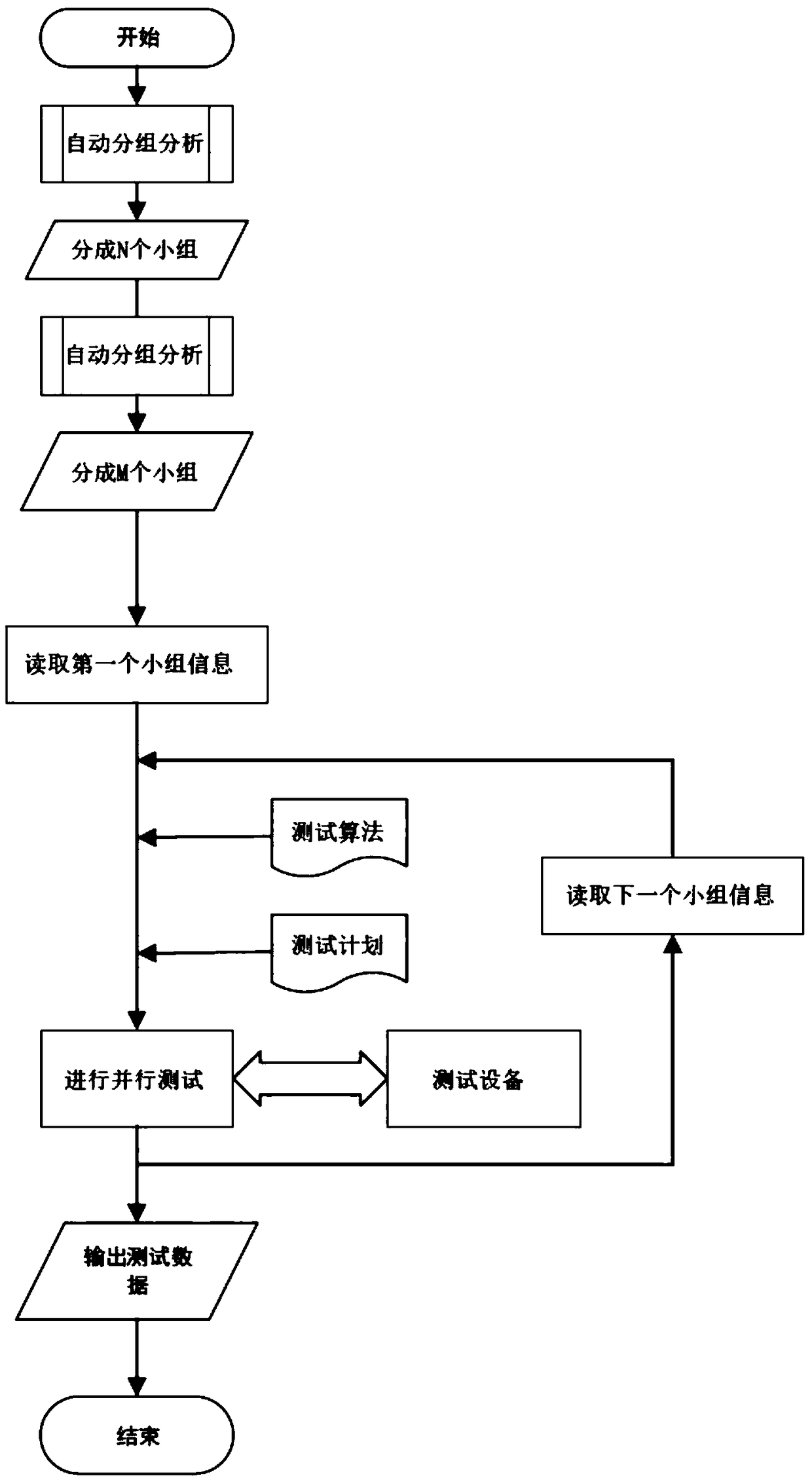

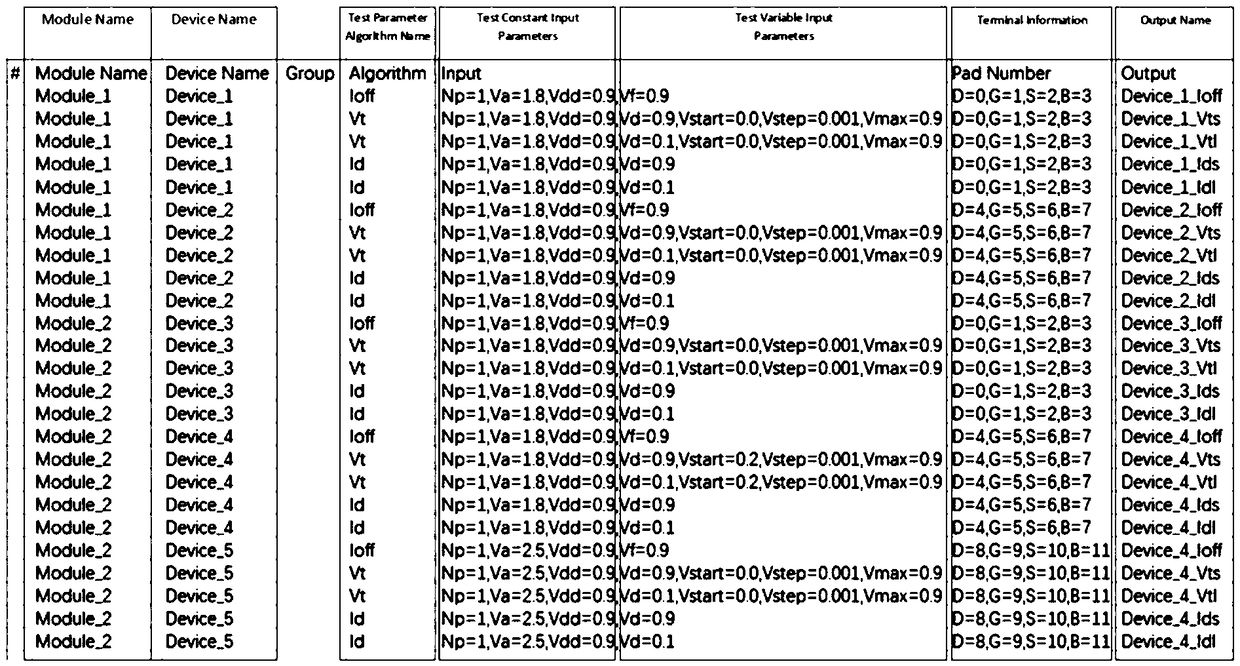

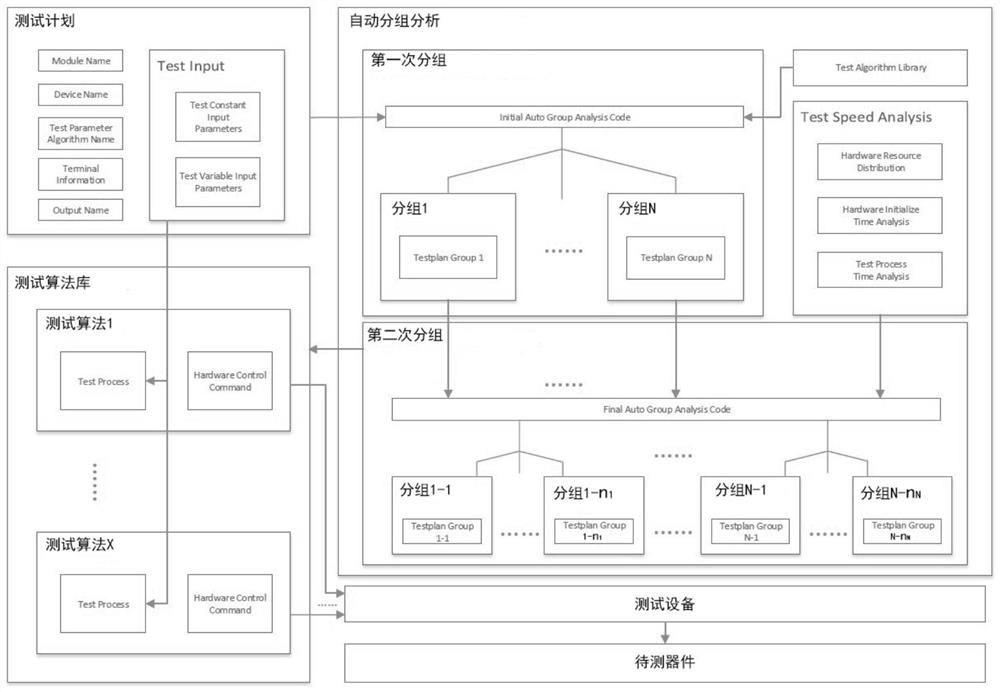

Storage medium and testing method for electrical parameter of wafer-level integrated circuit

ActiveCN109411380AExtended service lifeReduce error rateSemiconductor/solid-state device testing/measurementTest efficiencySoftware engineering

The invention relates to a storage medium and a testing method for the electrical parameter of a wafer-level integrated circuit. The testing method for the electrical parameter of the wafer-level integrated circuit comprises the following steps that: a) according to the electrical parameter of a structure to be tested and environment parameters required for testing, dividing test plan groups, anddividing test plans which have the same electrical parameter of the structure to be tested and the same environment parameters required for testing into one group; b) reading and configuring the environment parameter of the current test plan group; c) testing the electrical parameters of each testing structure in the current test plan group one by one; d) judging whether other test structures which are not tested are in the presence in the current test plan group or not; and e) judging whether other test groups which are not tested are in the presence or not. By use of the testing method, according to the type of the electrical parameter to be tested and the difference of the environment parameters, the test plans are classified, and testing efficiency is obviously improved.

Owner:SEMITRONIX

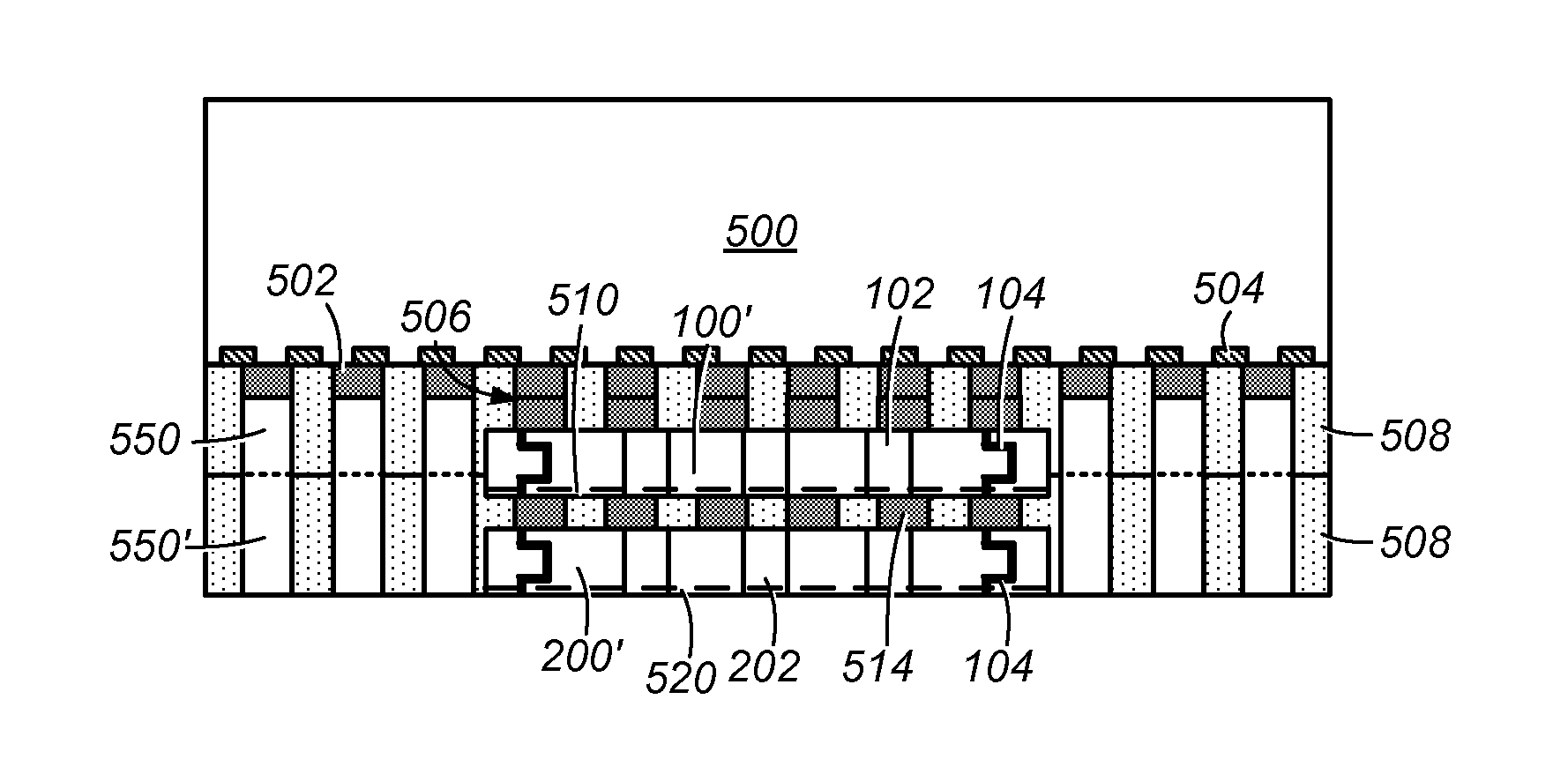

Wafer level integrated circuit probe array and method of construction

ActiveUS10078101B2Accurate locationEasy to processElectrical measurement instrument detailsElectrical testingElastomerBiomedical engineering

A testing device for wafer level testing of IC circuits is disclosed. An upper and lower pin (22, 62) are configured to slide relatively to each other and are held in electrically biased contact by an elastomer (80). To prevent rotation of the pins in the pin guide, a walled recess in the bottom of the pin guide engages flanges on the pins. In another embodiment, the pin guide maintains rotational alignment by being fitted around the pin profile or having projections abutting the pin. The pin guide (12) is maintained in alignment with the retainer 14 by establishing a registration corner (506) and driving the guide into the corner by elastomers in at least one diagonally opposite corner.

Owner:JOHNSTECH INT

Wafer Level Integrated Circuit Probe Array and Method of Construction

ActiveUS20190041429A1Easy to processGuarantees proper engagementElectrical measurement instrument detailsElectrical testingElastomerBiomedical engineering

A testing device for wafer level testing of IC circuits is disclosed. An upper and lower pin (22, 62) are configured to slide relatively to each other and are held in electrically biased contact by an elastomer (80). To prevent rotation of the pins in the pin guide, a walled recess in the bottom of the pin guide engages flanges on the pins. In another embodiment, the pin guide maintains rotational alignment by being fitted around the pin profile or having projections abutting the pin. The pin guide (12) is maintained in alignment with the retainer 14 by establishing a registration corner (506) and driving the guide into the corner by elastomers in at least one diagonally opposite corner.

Owner:JOHNSTECH INT

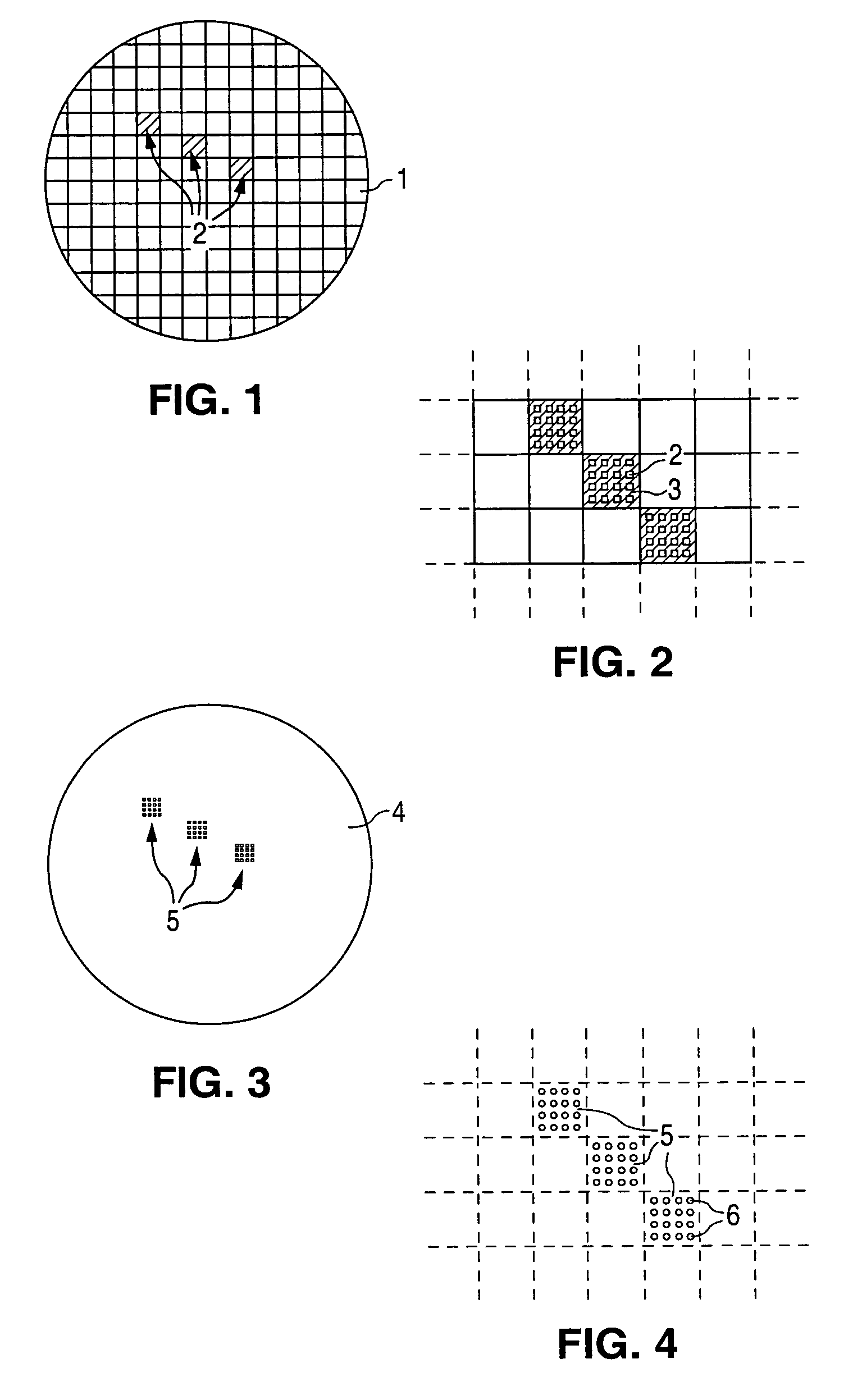

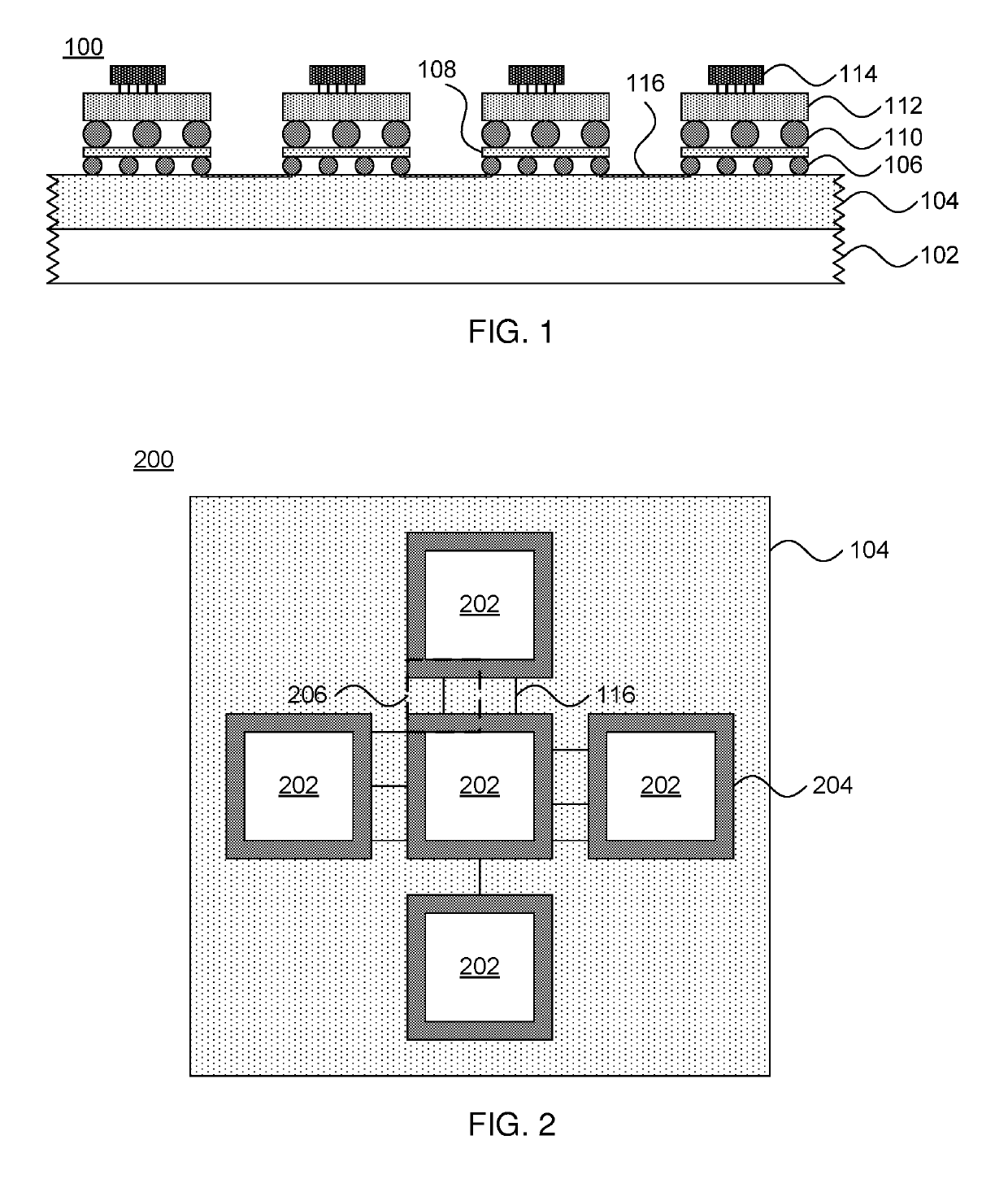

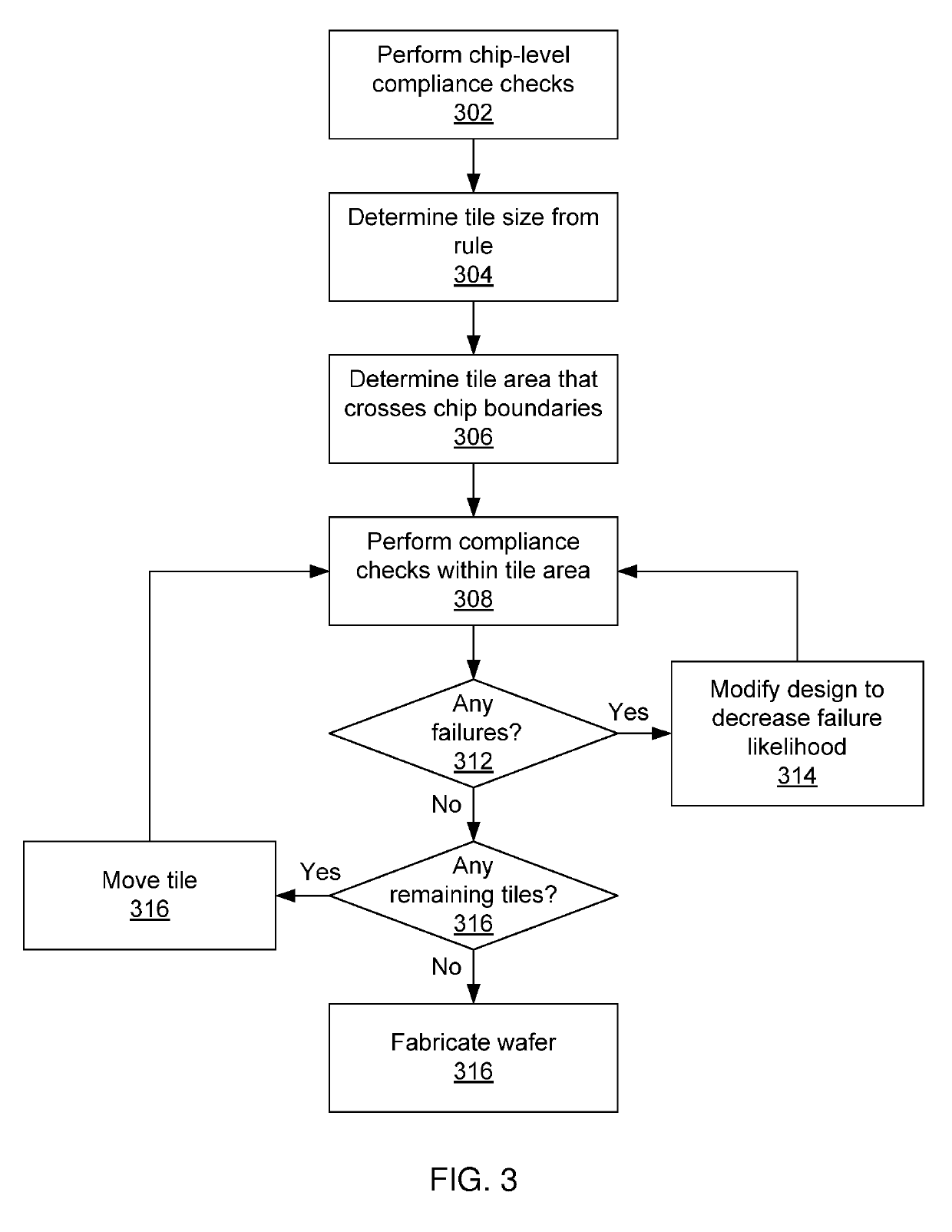

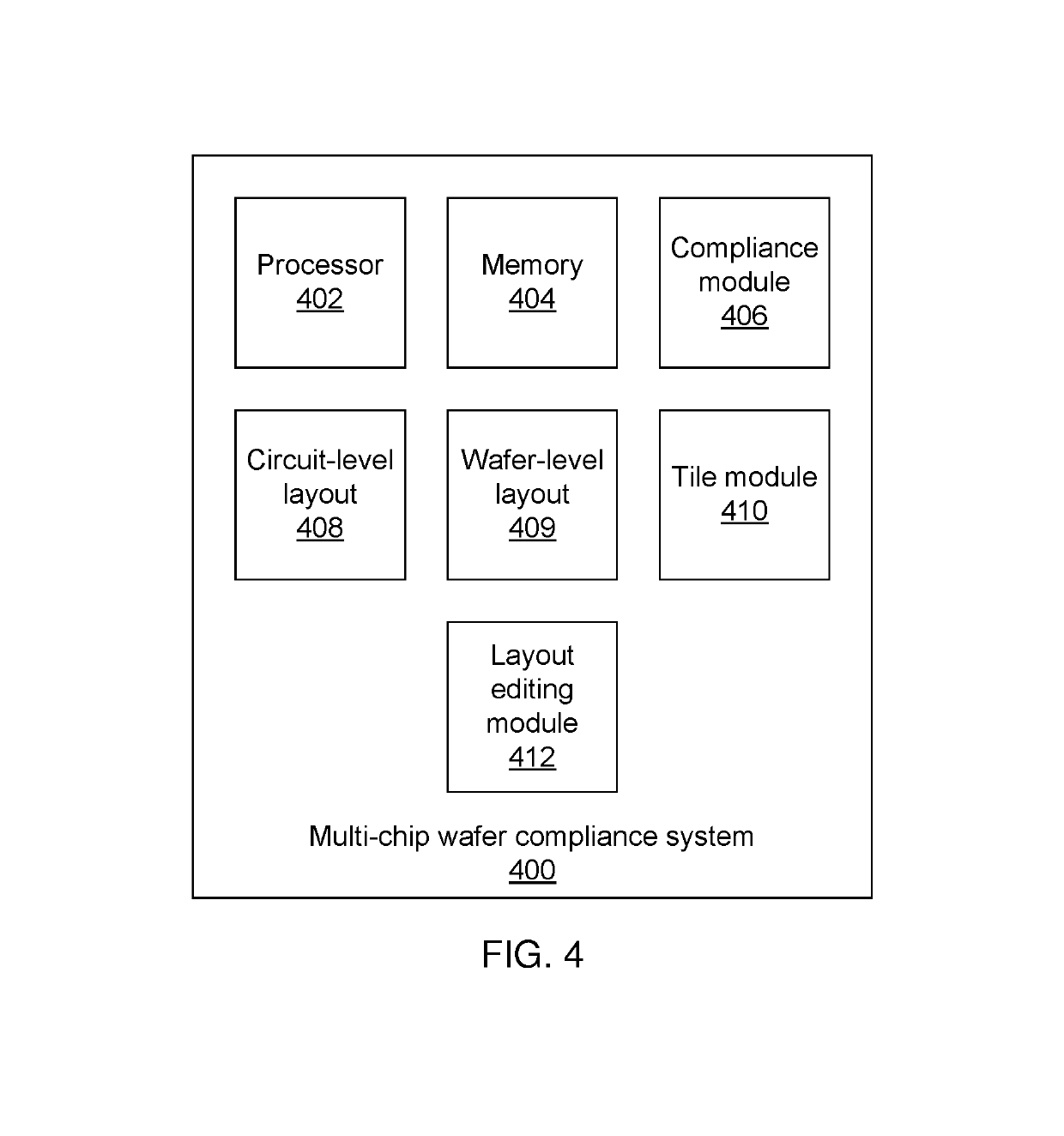

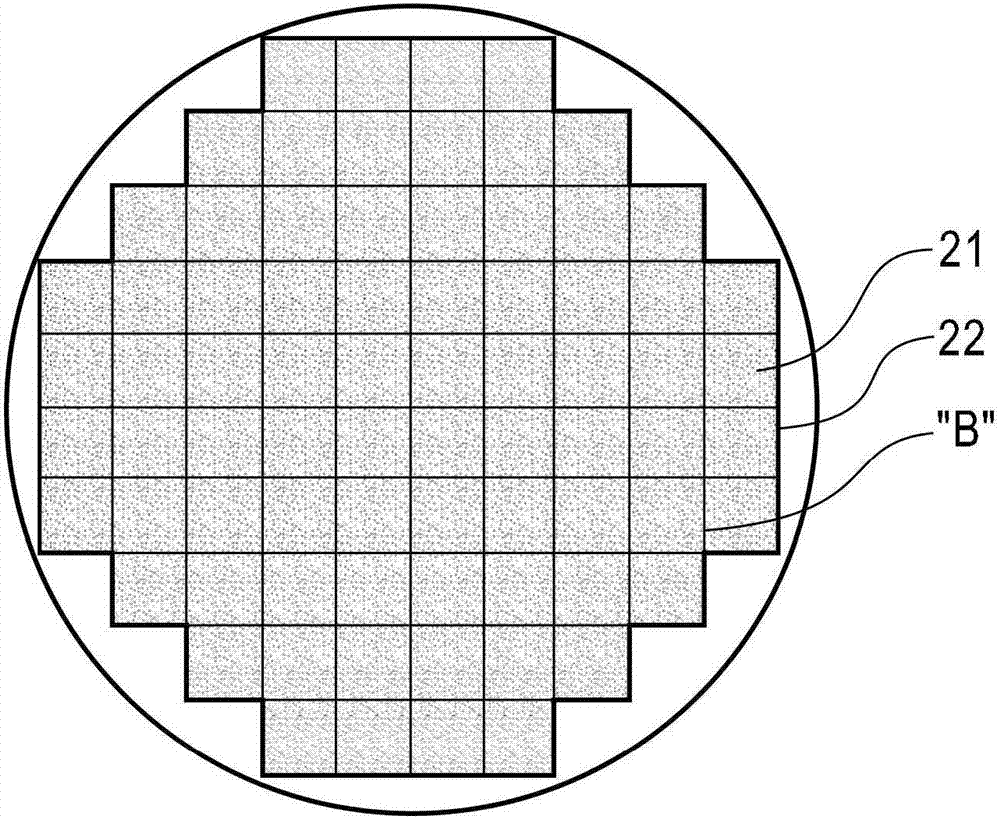

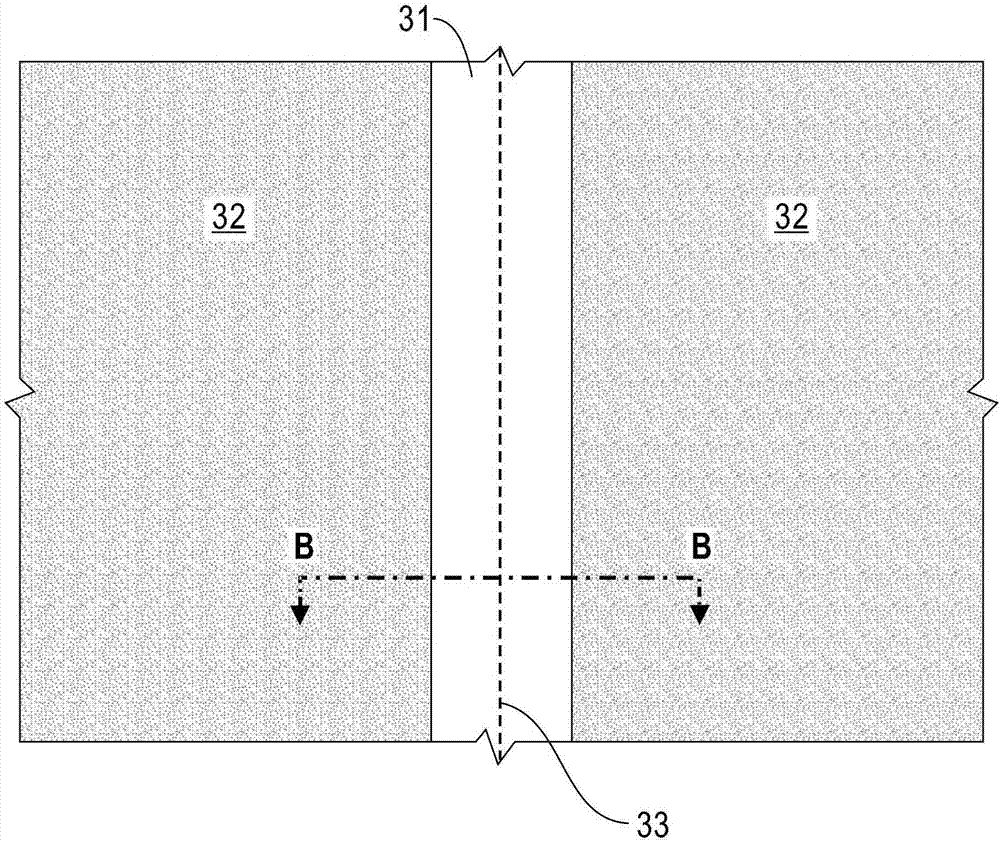

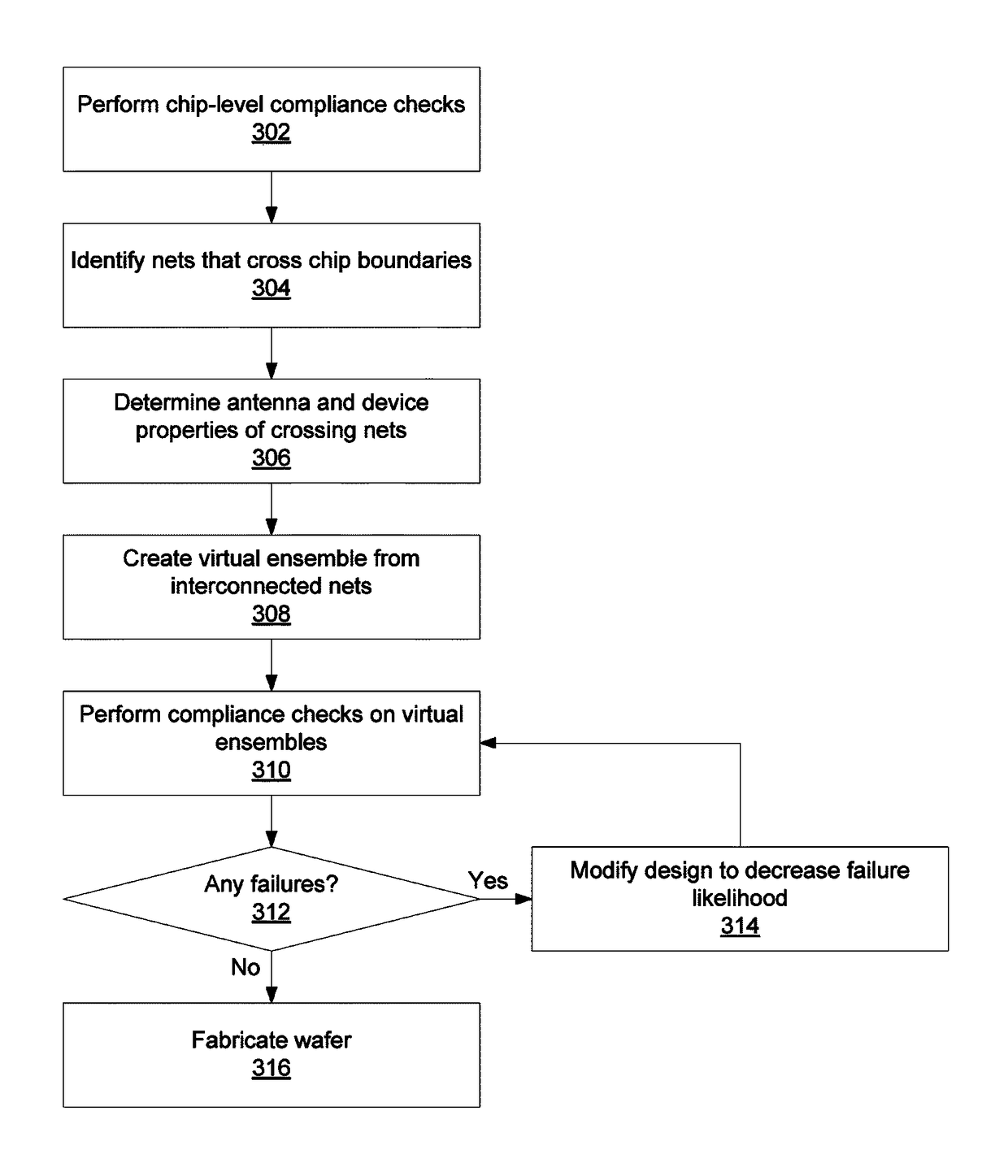

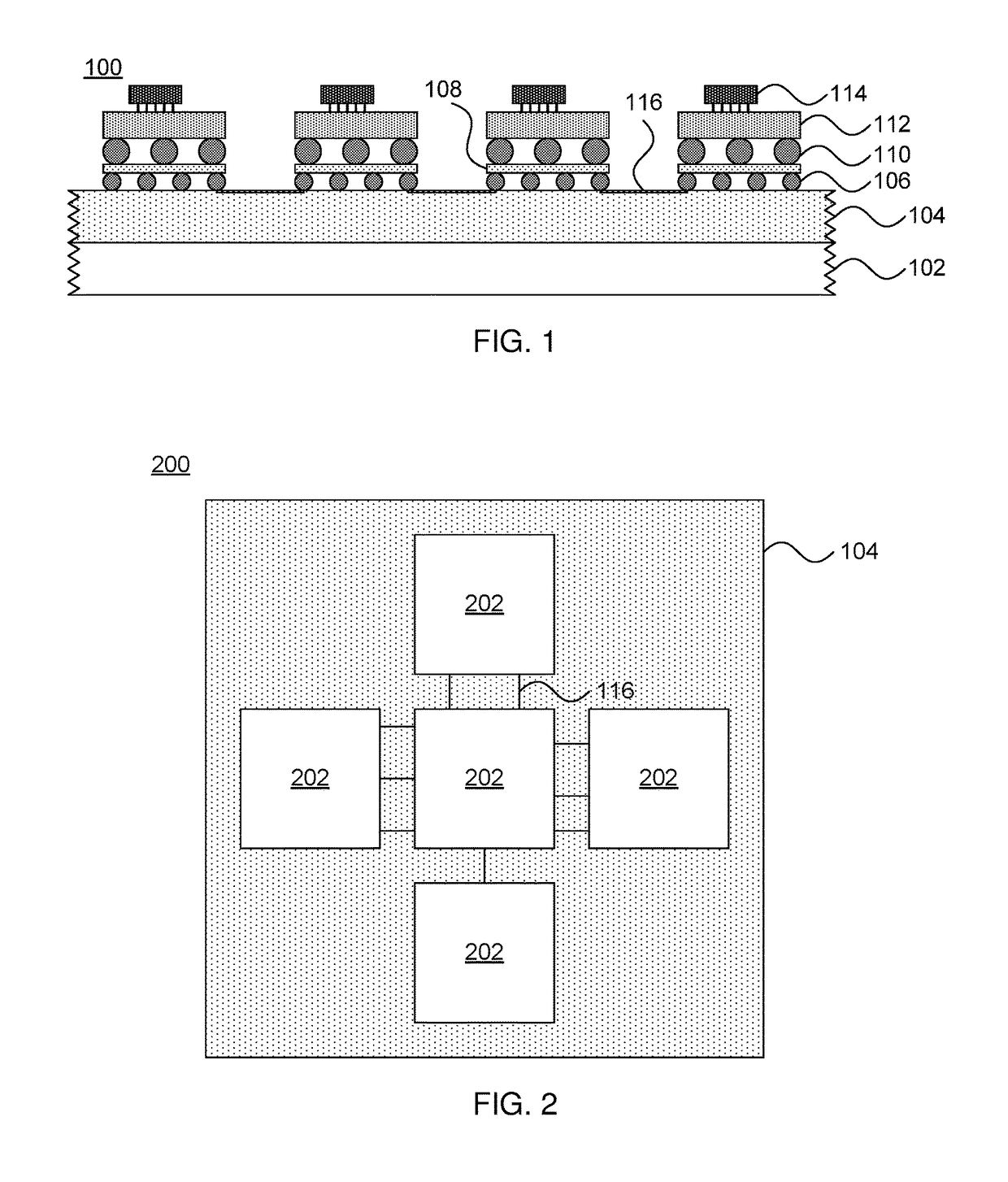

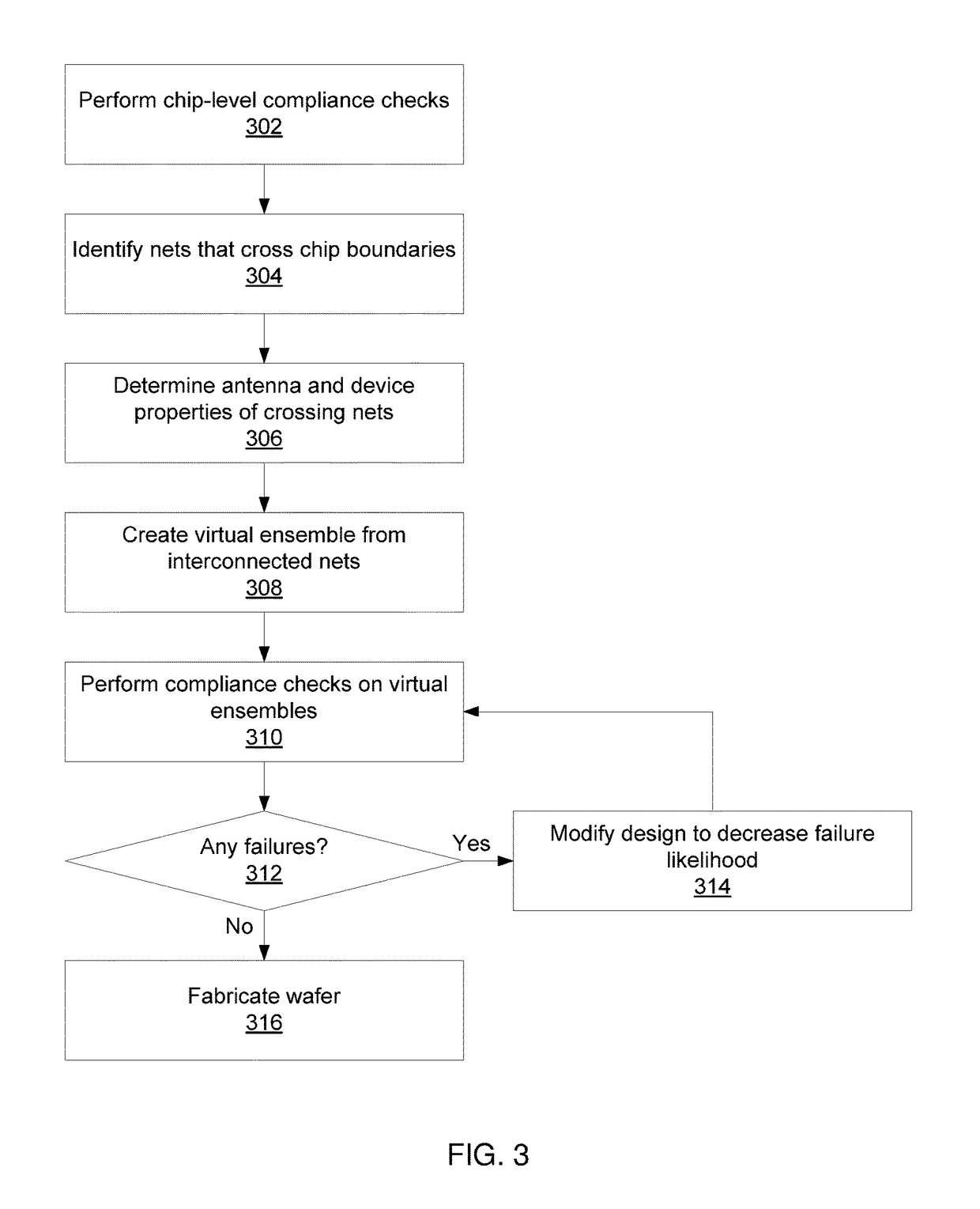

Checking wafer-level integrated designs for rule compliance

Methods and systems for checking a wafer-level design for compliance with a rule include determining whether each chip layout out of multiple chip layouts complies internally with one or more layout design rules. A tile area is determined, having a size that is based on the one or more layout design rules, that crosses a boundary between adjacent chip layouts and that leaves at least a portion of each chip layout uncovered. It is determined whether portions of the plurality of chip layouts inside the tile area comply with the one or more layout design rules. The chip layouts are modified, if chip layout area within the tile area fails to comply with the design rule, to bring non-compliant periphery chip regions into compliance.

Owner:INT BUSINESS MASCH CORP

Supercomputer using wafer scale integration

ActiveCN107251213ADigital data processing detailsSemiconductor/solid-state device detailsSupercomputerSemiconductor structure

A semiconductor structure includes a substrate with cooling layers, cooling channels, coolant inlets and outlets in fluid communication with the cooling channels, and a device layer on the cooling layers with one or more connection points and a device layer area. The device layer thermal coefficient of expansion is substantially equal to that of the cooling layers. A plurality of laminate substrates are disposed on, and electrically attached to, the device layer. The laminate substrate thermal coefficient of expansion differs from that of the device layer, each laminate substrate is smaller than the device layer portion to which it is attached, and each laminate substrate includes gaps between sides of adjacent laminate substrates. The laminate substrates are not electrically or mechanically connected to each other across the gaps therebetween and the laminate substrates are small enough to prevent warping of the device, interconnection and cooling layers due to thermal expansion.

Owner:INT BUSINESS MASCH CORP

A method for testing electrical parameters of storage media and wafer-level integrated circuits

ActiveCN109411380BExtended service lifeReduce error rateSemiconductor/solid-state device testing/measurementTest inputTest group

The invention relates to a storage medium and a testing method for the electrical parameter of a wafer-level integrated circuit. The testing method for the electrical parameter of the wafer-level integrated circuit comprises the following steps that: a) according to the electrical parameter of a structure to be tested and environment parameters required for testing, dividing test plan groups, anddividing test plans which have the same electrical parameter of the structure to be tested and the same environment parameters required for testing into one group; b) reading and configuring the environment parameter of the current test plan group; c) testing the electrical parameters of each testing structure in the current test plan group one by one; d) judging whether other test structures which are not tested are in the presence in the current test plan group or not; and e) judging whether other test groups which are not tested are in the presence or not. By use of the testing method, according to the type of the electrical parameter to be tested and the difference of the environment parameters, the test plans are classified, and testing efficiency is obviously improved.

Owner:杭州广立测试设备有限公司

Checking wafer-level integrated designs for antenna rule compliance

Methods and systems for checking a wafer-level design for compliance with a rule include identifying nets that cross chip boundaries for each of a plurality of chip layouts. Net properties are determined for each of the identified nets. Interconnected identified nets are combined into one or more virtual ensembles having properties defined by a sum of the properties of the respective interconnected nets. Each virtual ensemble is evaluated for compliance with a design rule. The chip layouts related to virtual ensembles that do not comply with the design rule are modified to bring non-compliant virtual ensembles into compliance.

Owner:INT BUSINESS MASCH CORP

Wafer level applied RF shields

InactiveCN103858227AMagnetic/electric field screeningSemiconductor/solid-state device detailsMetalIntegrated circuit

An embodiment of a method of forming an on-chip RF shield on an integrated circuit chip in accordance with the present disclosure includes providing a wafer level integrated circuit component wafer having a front side and a back side before singulation; applying a resin metal layer on a back side of the wafer; and then separating the wafer into discrete RF shielded components. It is this resin metal layer on the back side that acts effectively as the RF shield, after singulation, i.e. separation of the wafer, into discrete RF shielded components.

Owner:HUATIAN TECH KUNSHAN ELECTRONICS

MEMS integrated device and preparation method thereof

PendingCN114334880AAchieve vertical interconnectionEnable direct integrationTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesIntegrated circuit manufacturingRedistribution layer

The invention provides an MEMS integrated device and a preparation method thereof. The device comprises a first rewiring layer, an MEMS layer and an application-specific integrated circuit layer, the MEMS layer and the application-specific integrated circuit layer are connected through wafer-level low-temperature silicon-silicon bonding; the MEMS layer is provided with a first through hole and a second through hole which are filled with copper, the first through hole penetrates through the MEMS layer, and the second through hole penetrates through the cover plate layer and is connected with the MEMS movable structure layer; the first redistribution layer includes an internal wiring connecting the first via, the second via, and the external electrode. The internal electrode is electrically connected with the first through hole. Wafer-level integration and packaging of the MEMS device and the application-specific integrated circuit are completed through wafer-level low-temperature silicon-silicon bonding, the through holes filled with copper are formed in the MEMS layer to achieve vertical interconnection between multiple chip layers, the situation that through holes used for internal and external communication are additionally formed in the application-specific integrated circuit is avoided, copper filling is compatible with the advanced integrated circuit manufacturing process, and the manufacturing cost is reduced. The MEMS device can be directly integrated with an application-specific integrated circuit wafer of less than 90 nanometers, so that the compatibility is improved, the packaging cost is reduced, and the packaging efficiency is improved.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP