Test structure and test method of wafer-level integrated system

An integrated system and test structure technology, applied in the direction of single semiconductor device testing, semiconductor/solid-state device components, sorting, etc., can solve the problem of not adapting to the wafer-level system test method, and achieve the effect of ensuring reliable operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

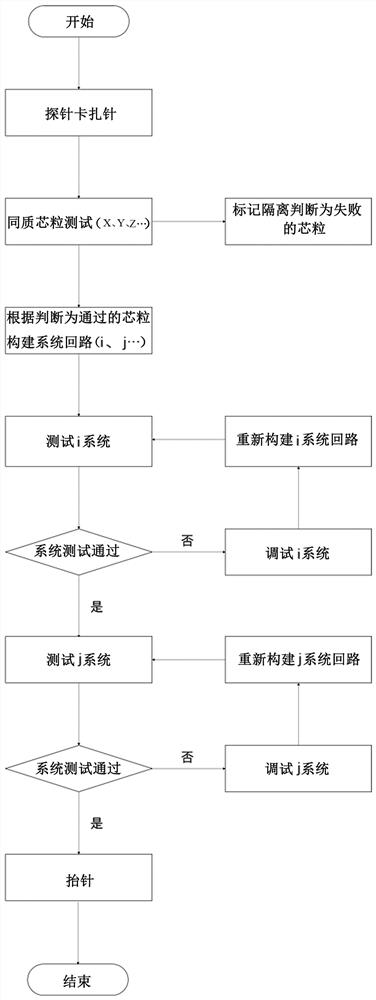

[0033] In order to make the objectives, technical solutions and technical effects of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and embodiments of the description.

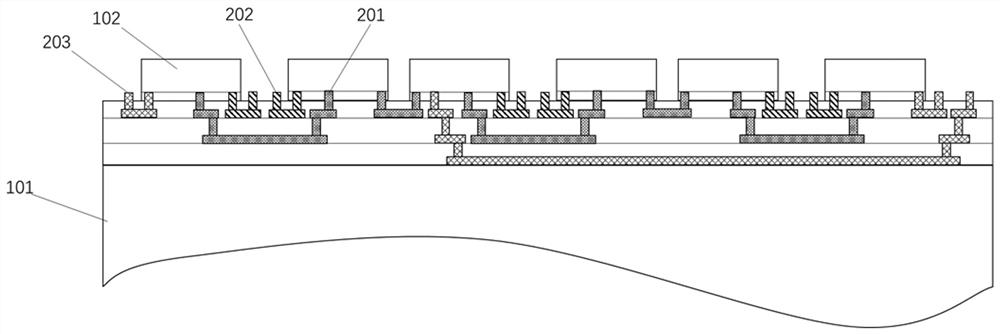

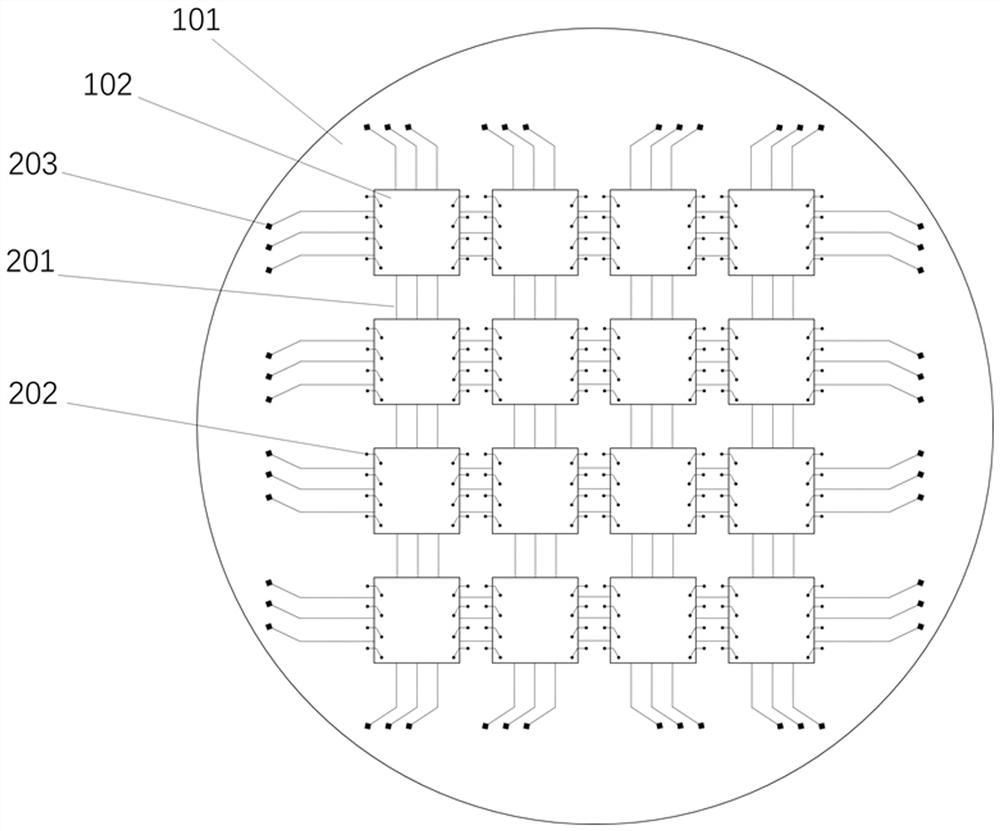

[0034] A test structure for a wafer-level integrated system, such as figure 1 and figure 2 As shown, it includes a wafer substrate 101 and n (n≥2) chips 102 bonded to the wafer, and the chips are connected to each other through the wafer electrical interconnection structure 201. The die test circuit 202 is led out from the periphery and the system test circuit 203 is led out through the inter-wafer interconnection.

[0035] The n chips form at least one complete operable system through the wafer electrical interconnection structure 201 .

[0036] The n core particles are homogeneous core particles or heterogeneous core particles.

[0037] The n core particles are all good-quality core particles sliced after passin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More