Patents

Literature

86 results about "System level testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System Testing System testing is the first level in which the complete application is tested as a whole. System testing is the first level in which the complete application is tested as a whole. The goal at this level is to evaluate whether the system has complied with all of the outlined requirements and to see that it meets Quality Standards.

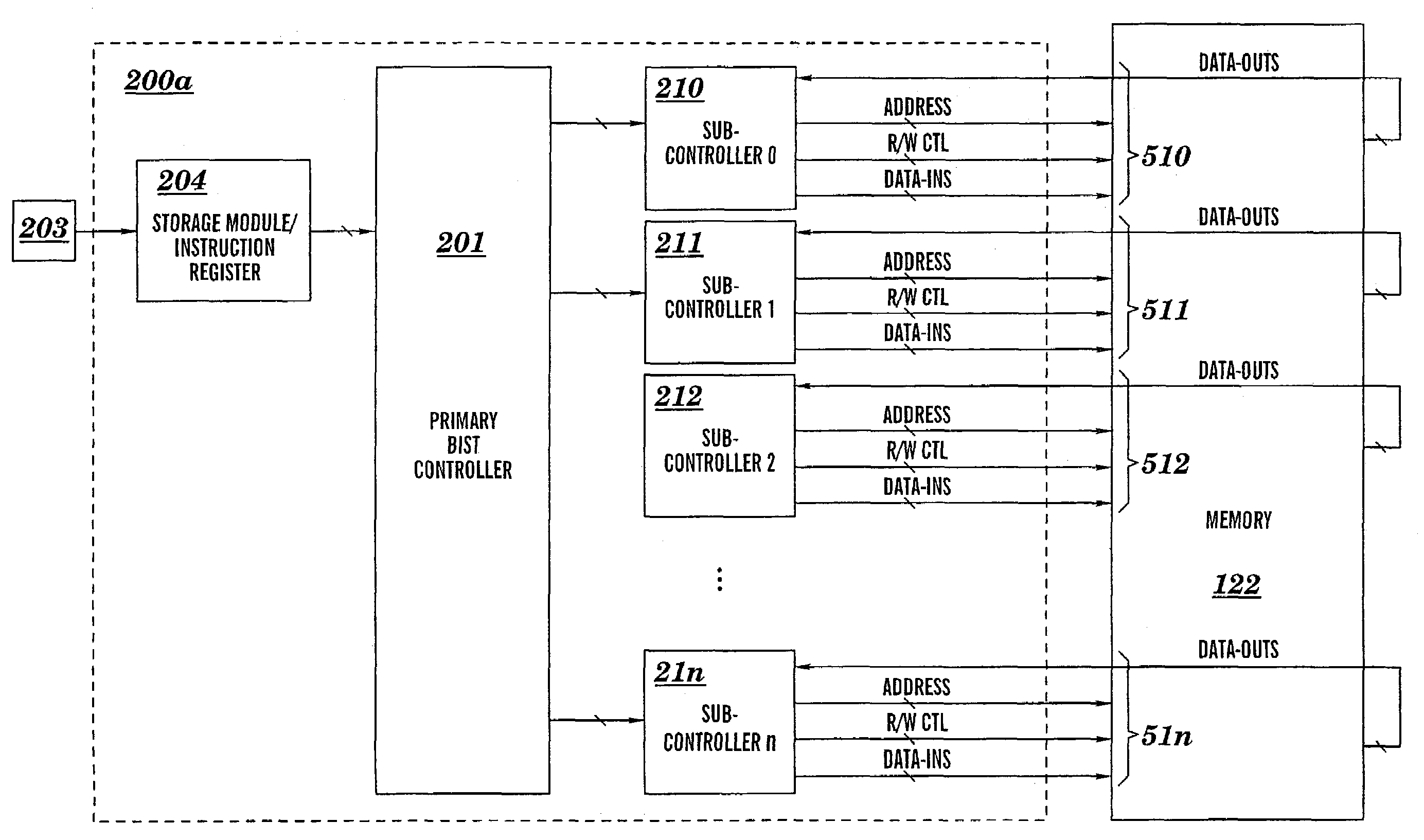

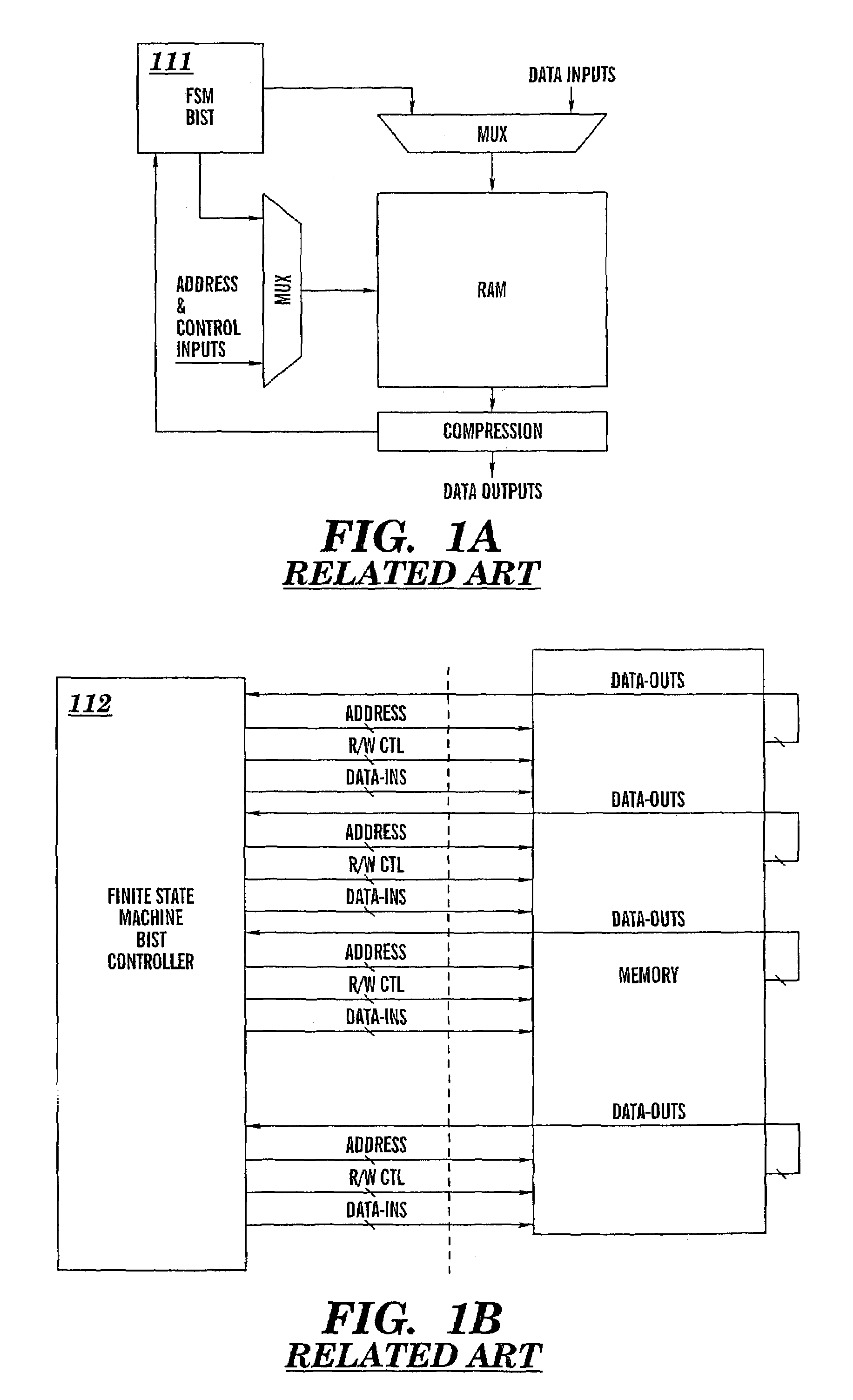

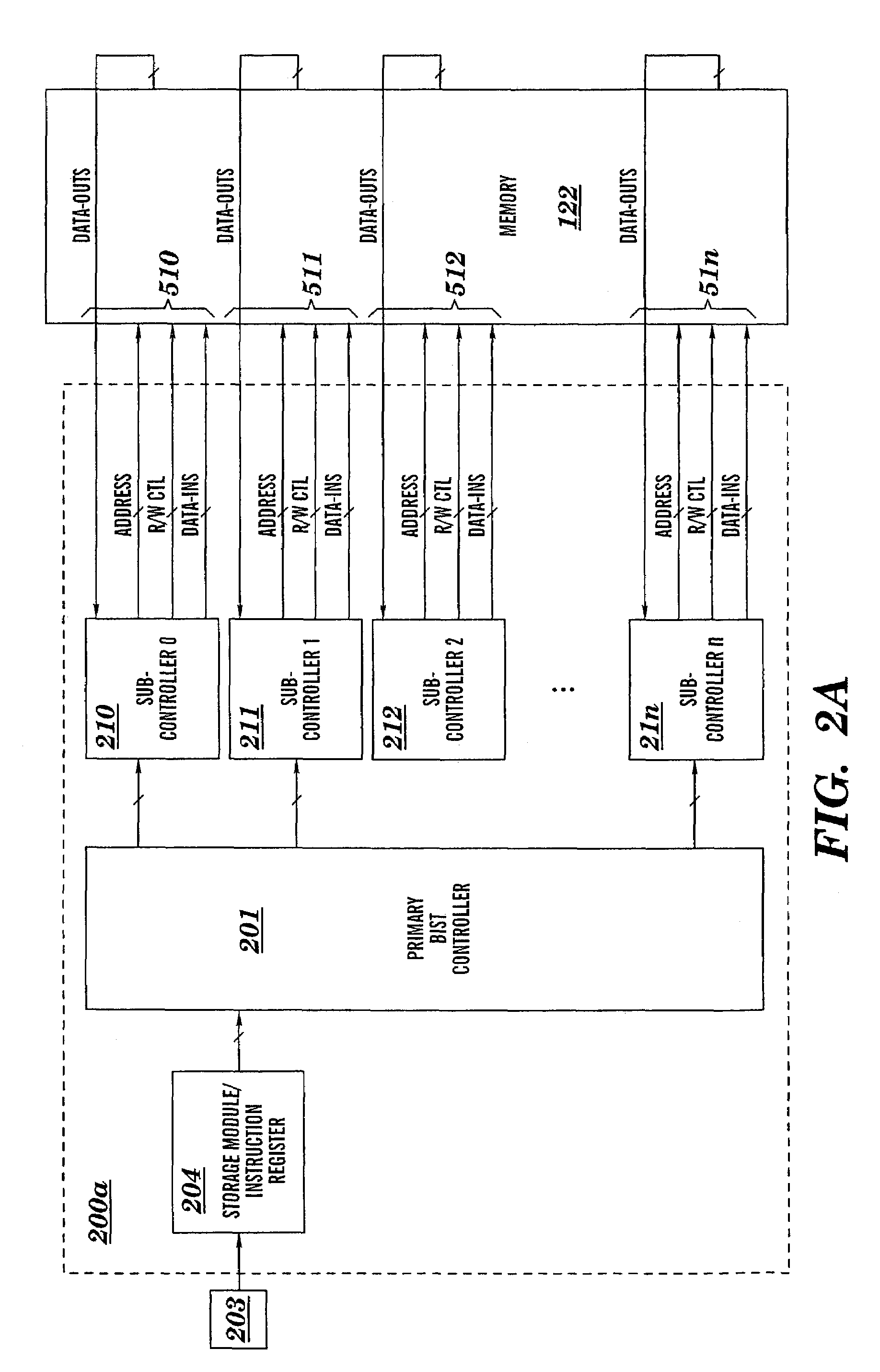

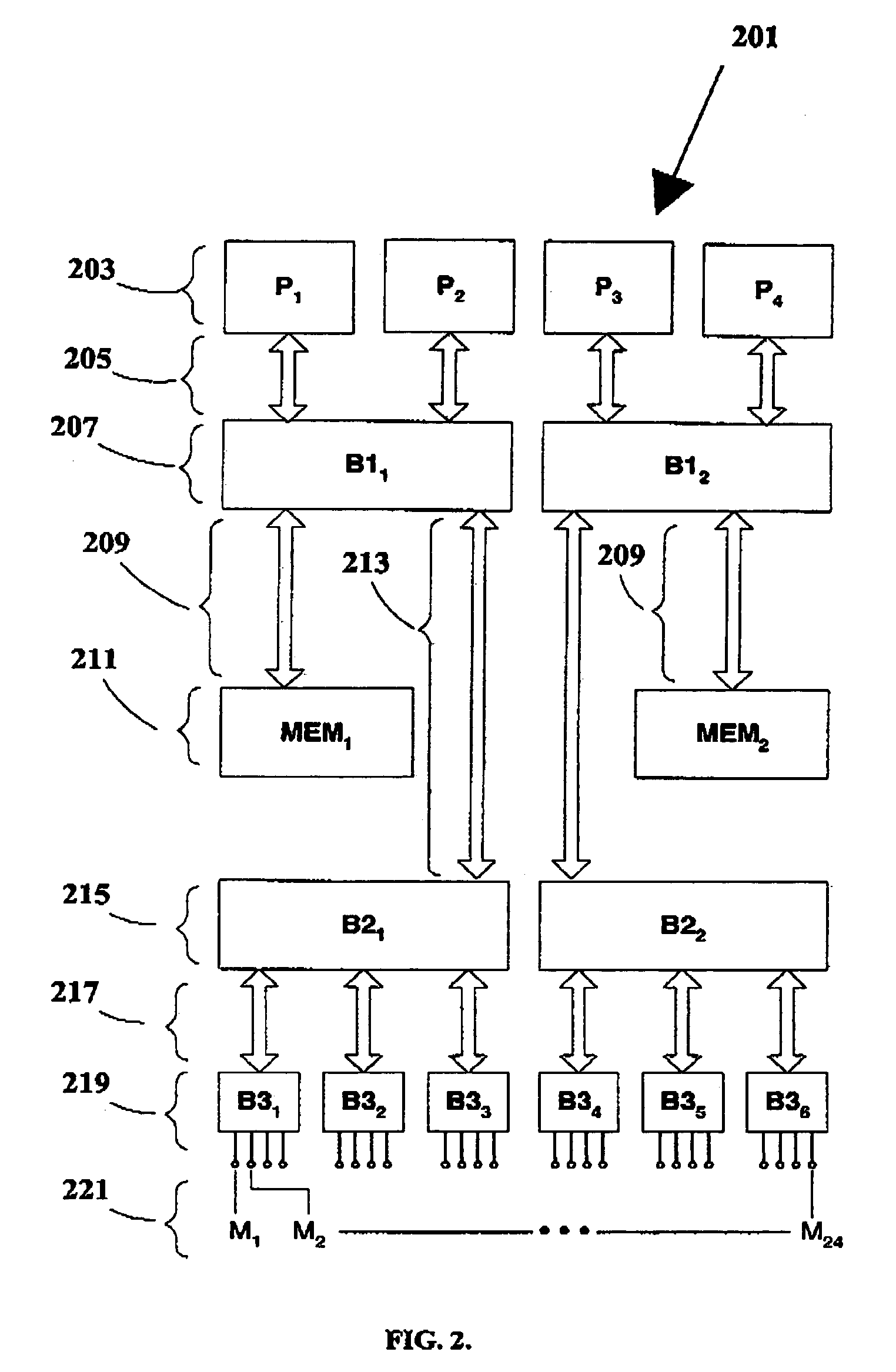

Programable multi-port memory BIST with compact microcode

InactiveUS7168005B2Easy to testIncrease flexibilityElectronic circuit testingFunctional testingAs DirectedMaster controller

A microcode programmable built-in-self-test (BIST) circuit and method for testing a multiported memory via multiple ports, either simultaneously or sequentially, as directed by a microcode instruction word. The microcode instruction word contains a plurality of executable subinstructions and one bit of information that controls whether the test operations prescribed in the plurality of subinstructions shall be executed in parallel or in series. The executable subinstructions are dispatched by a primary controller to subcontrollers which perform test operations at each port according to the subinstructions. The microcode programable BIST architecture flexibly facilitates the testing of multiple devices, multiported devices, including multiported memory structures and complex dependent multiported memory structures. The BIST supports in-situ testing of the functionality of the memory at wafer, module, and burn-in, as well as system-level testing.

Owner:CADENCE DESIGN SYST INC

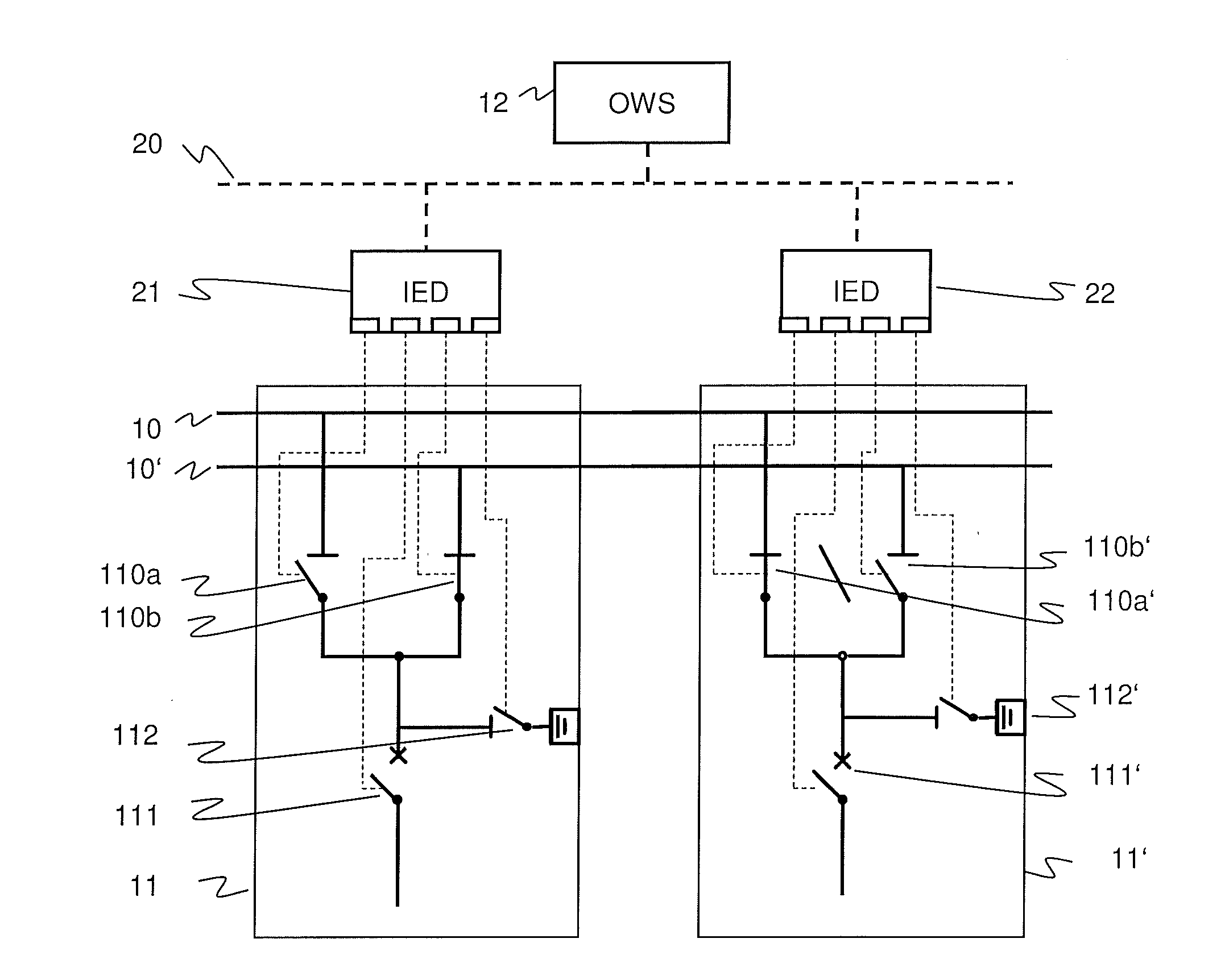

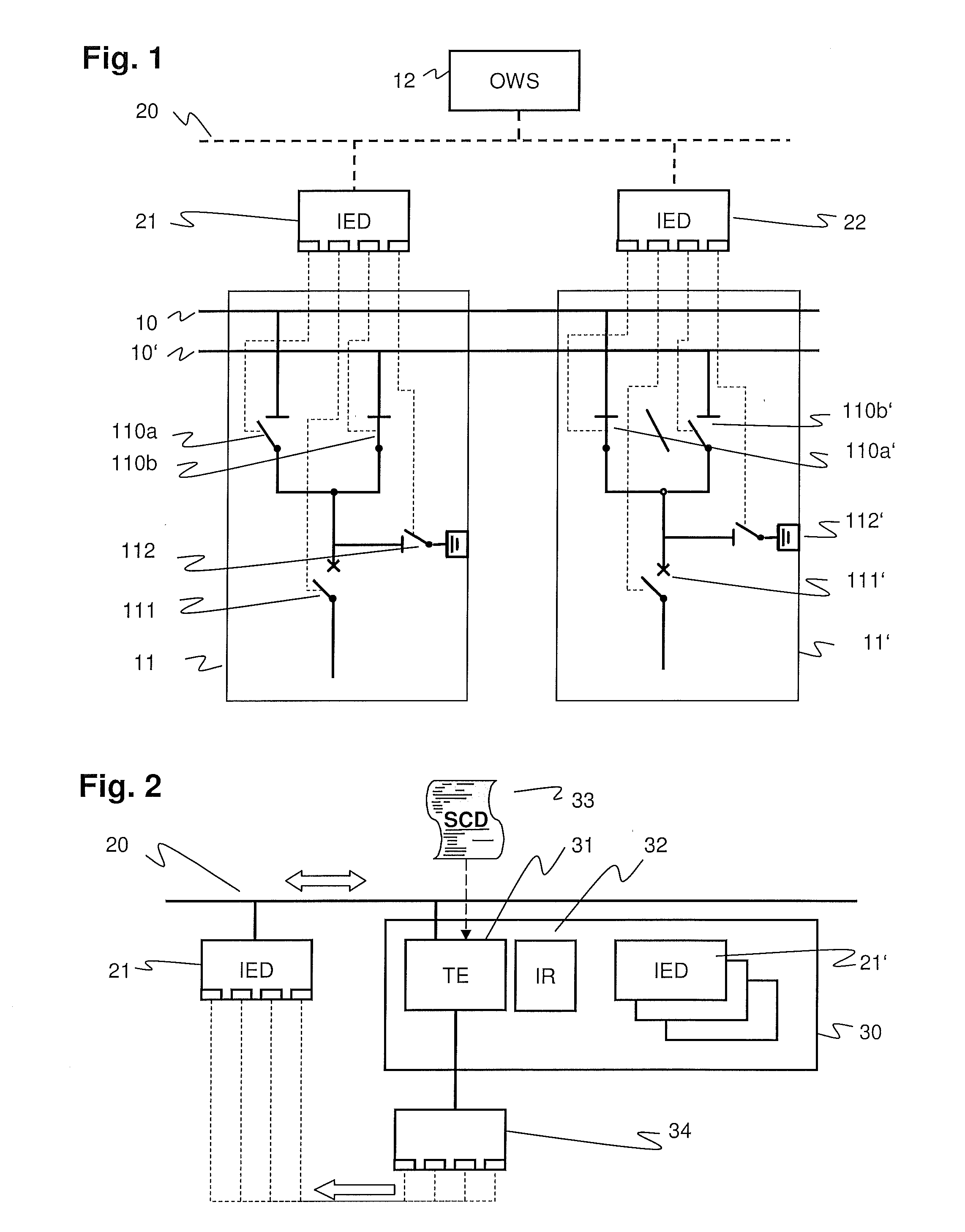

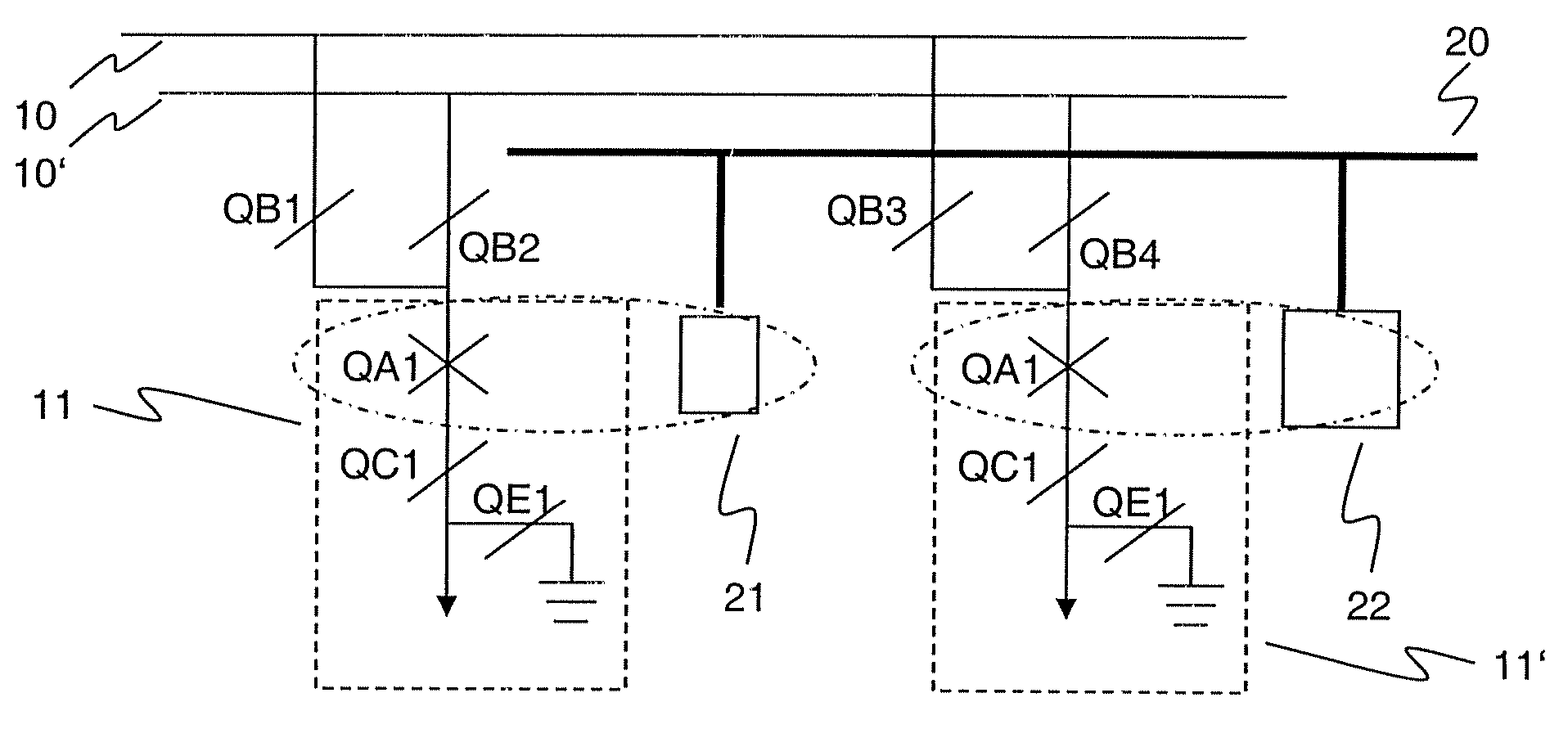

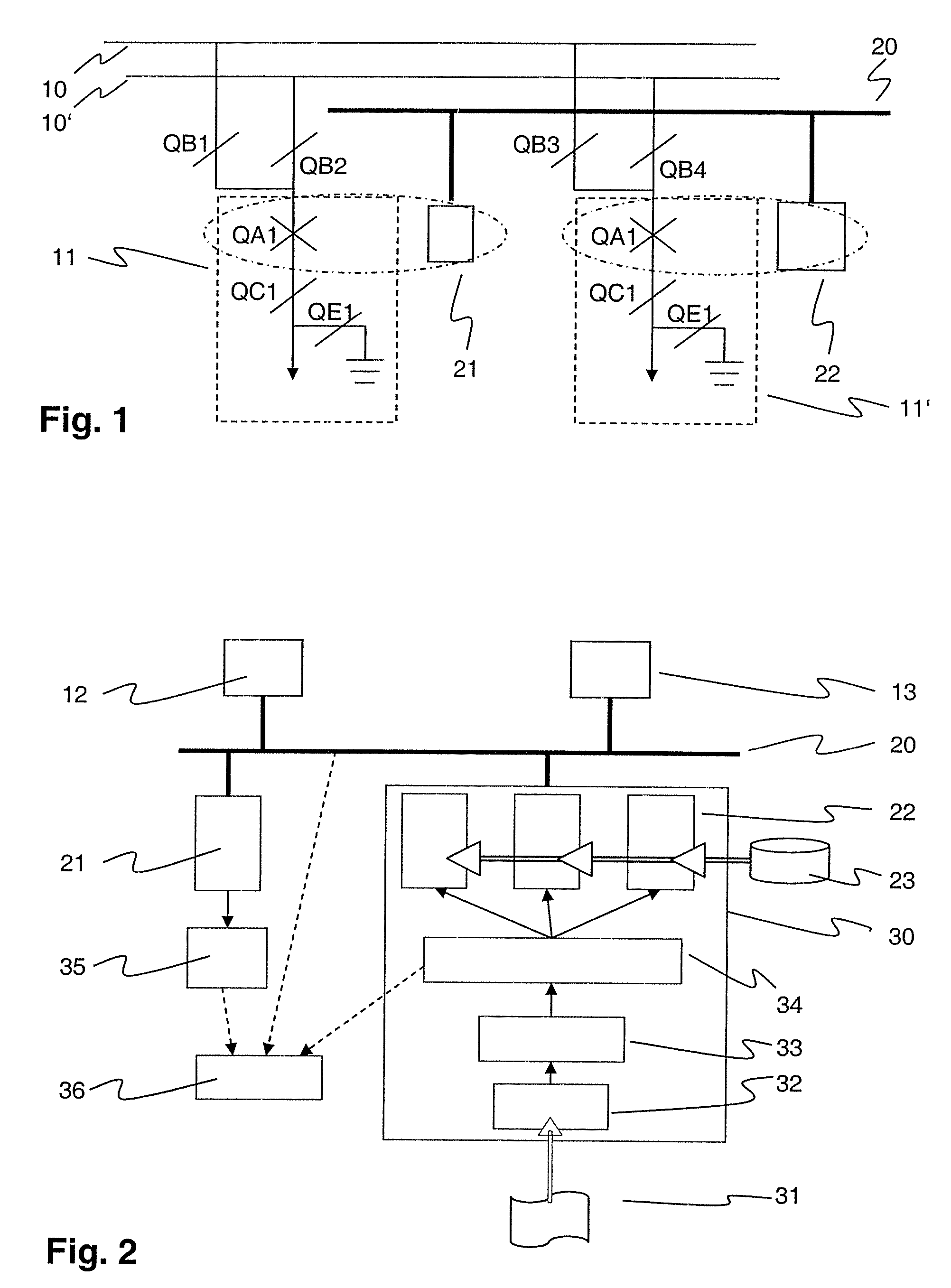

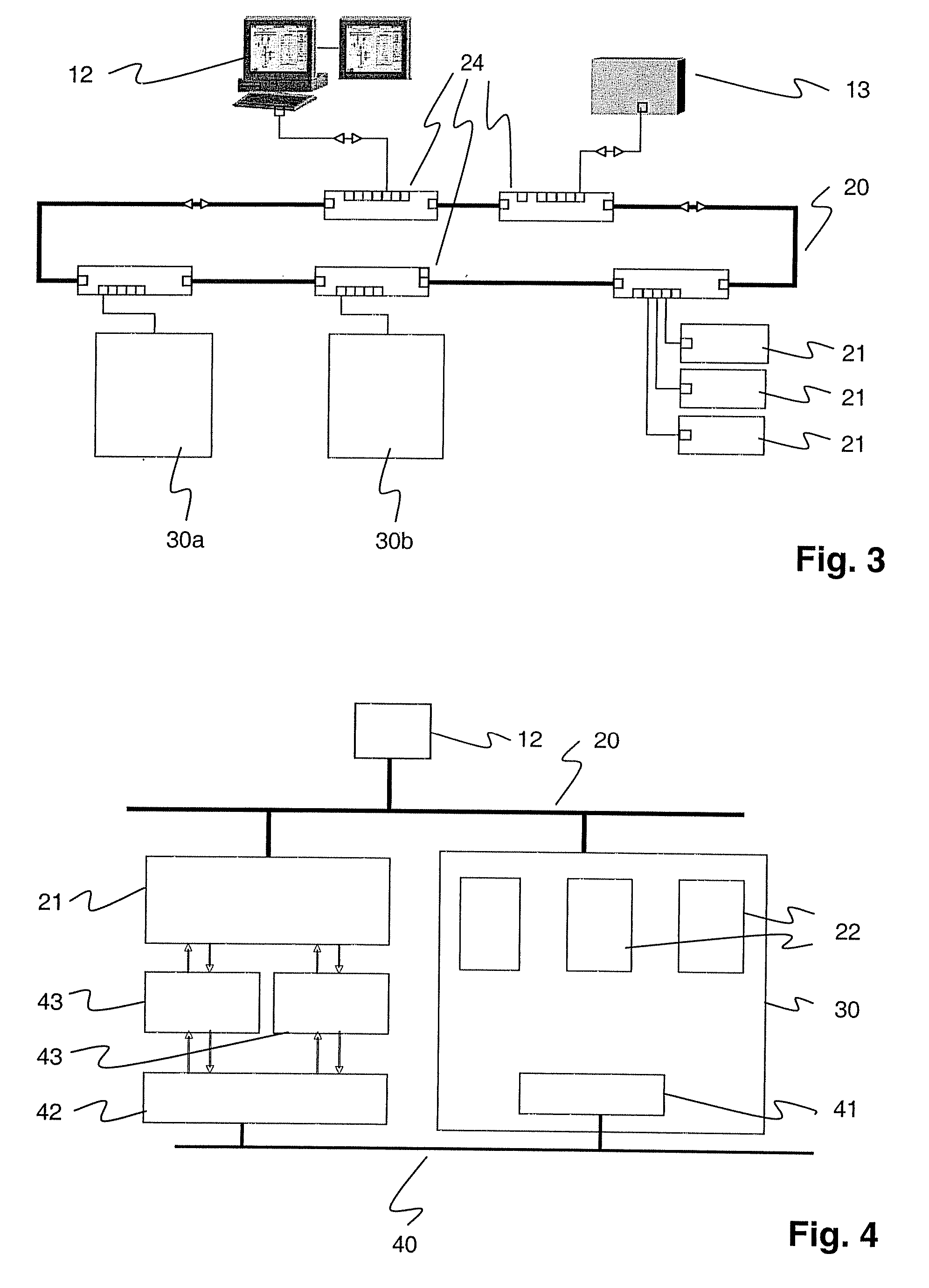

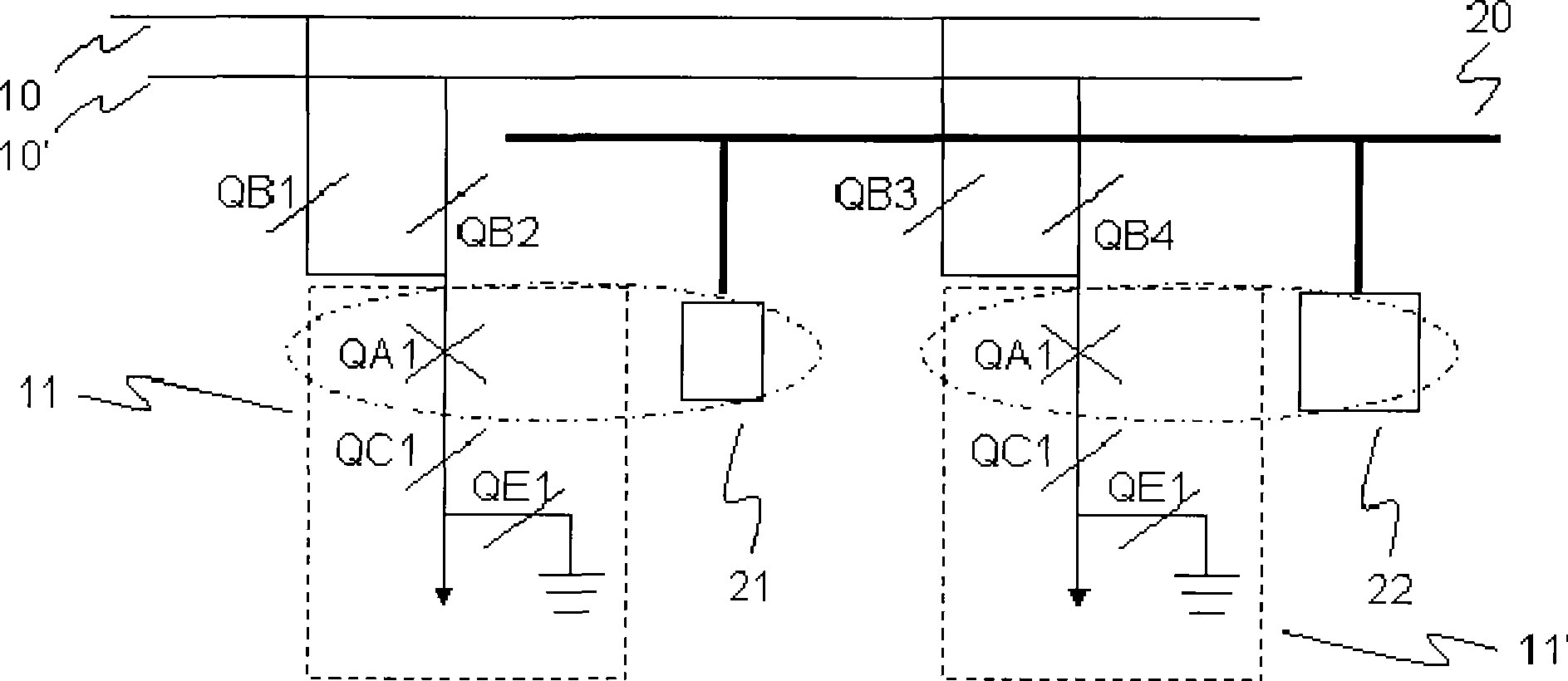

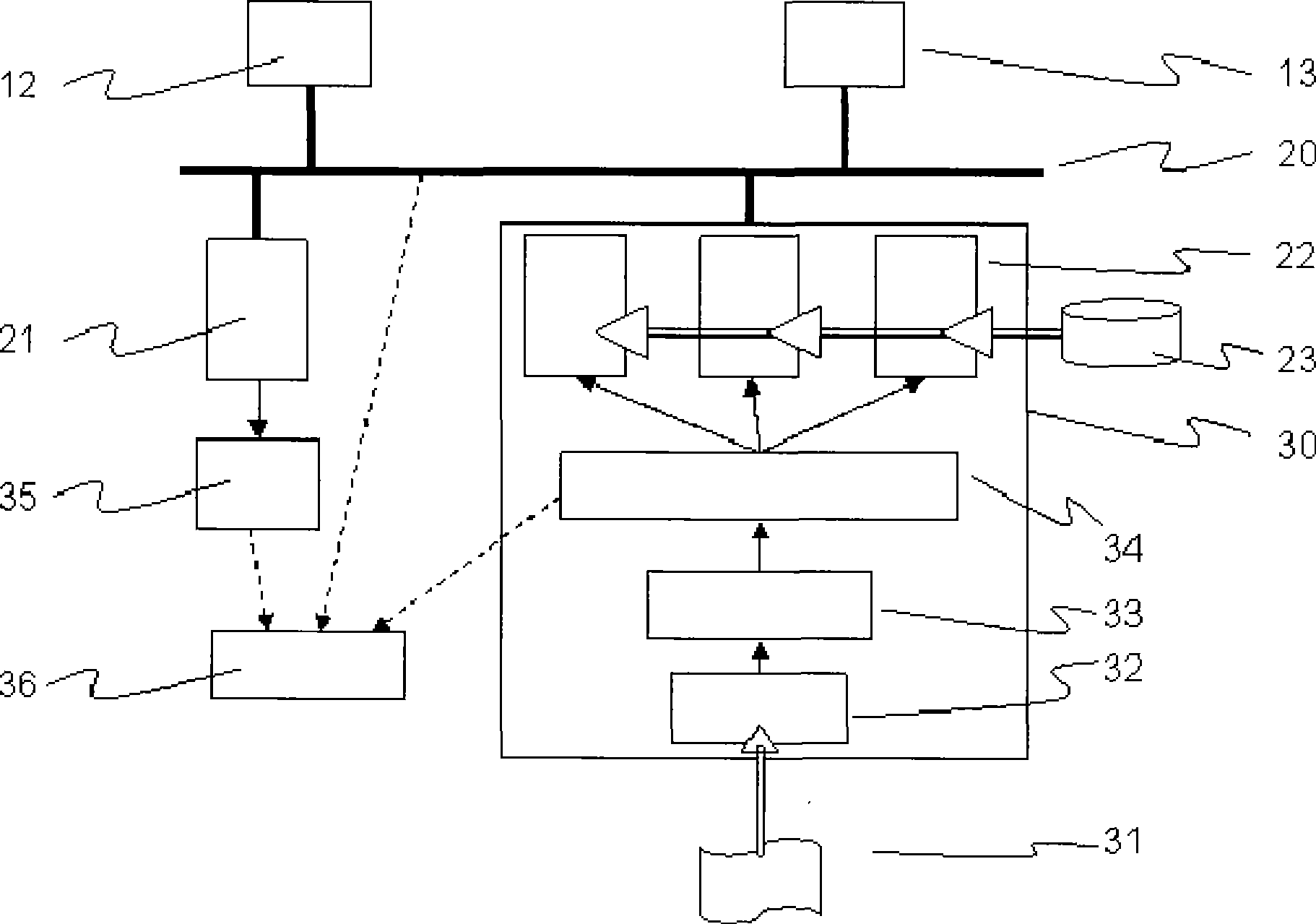

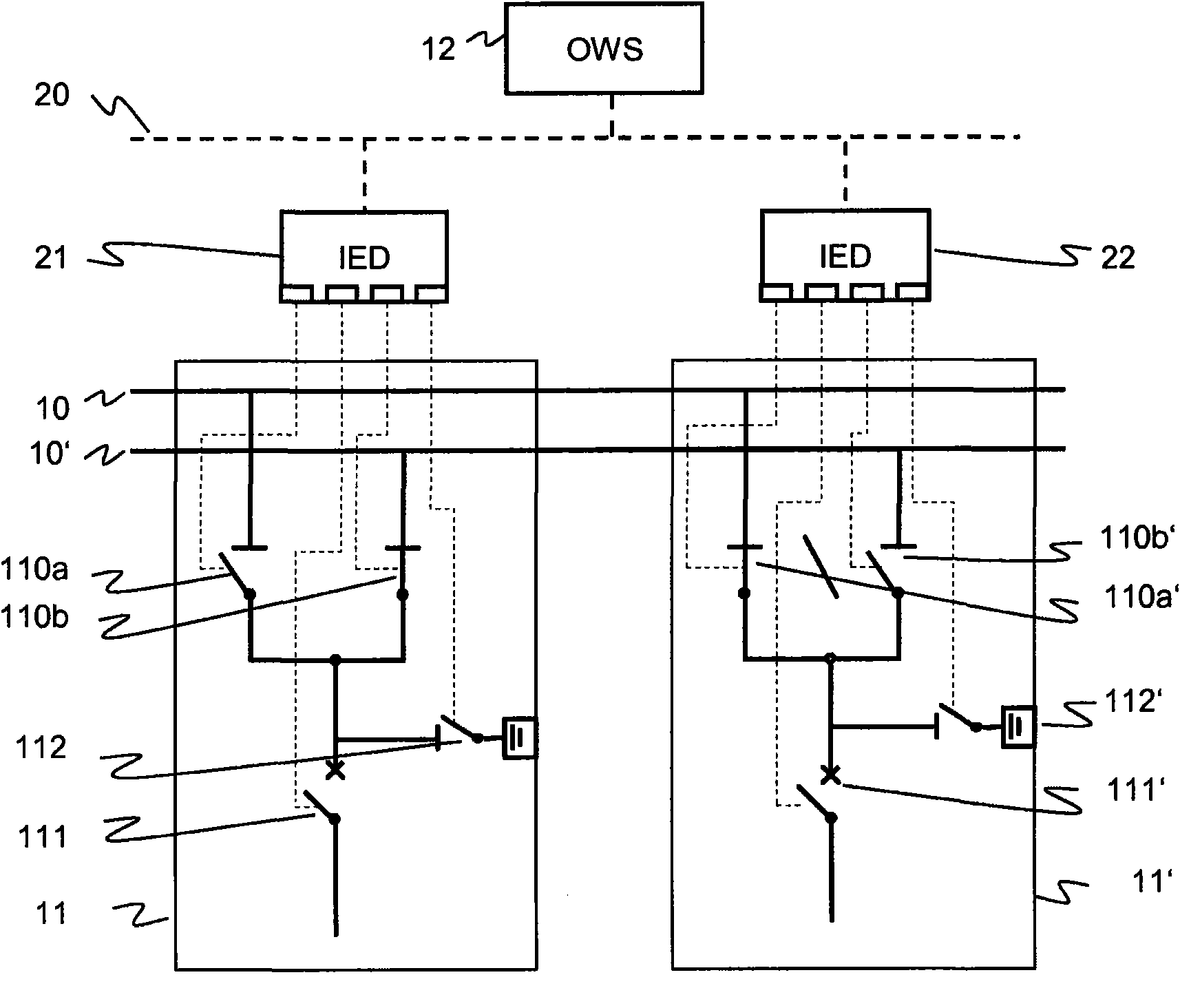

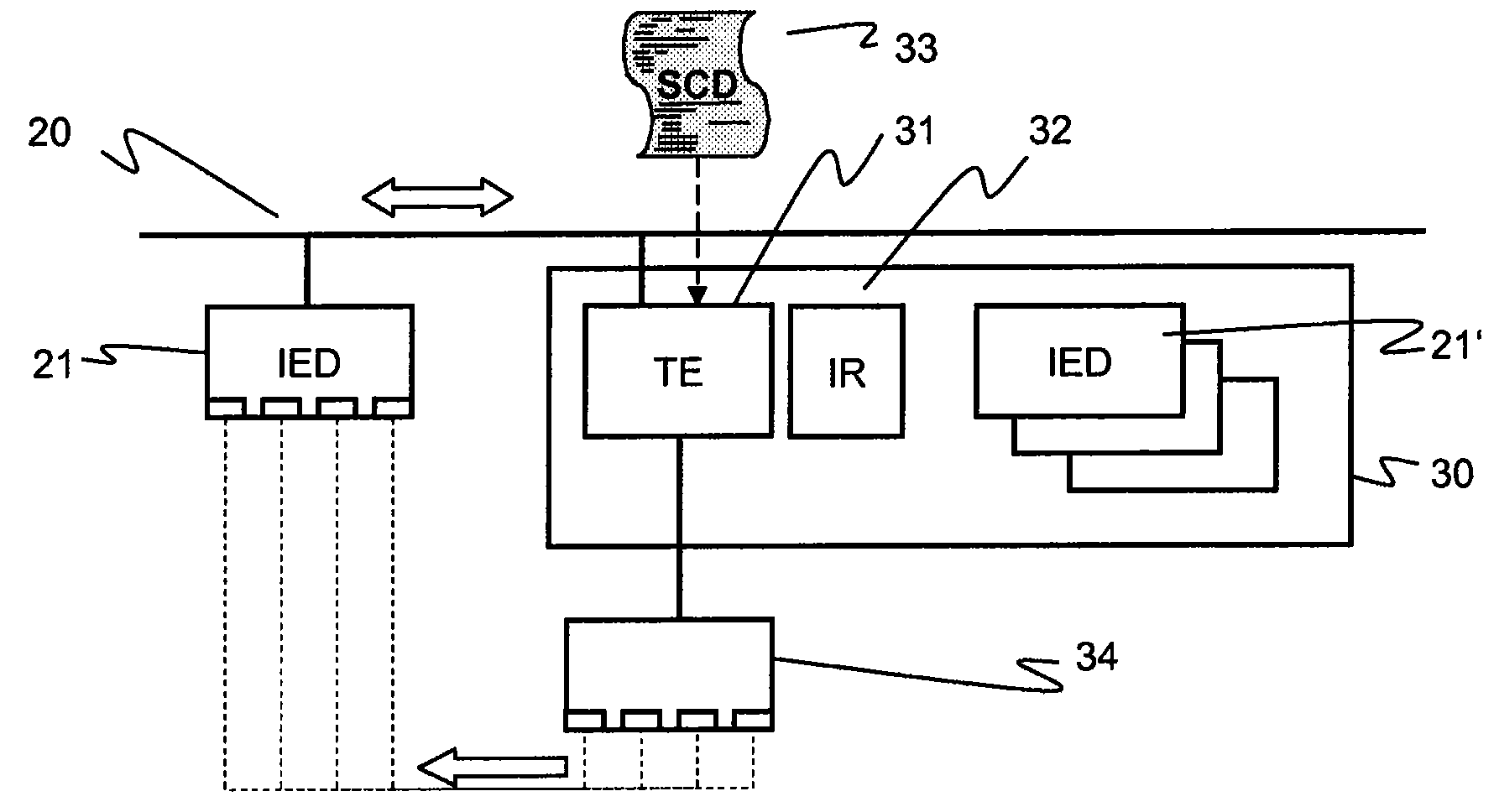

System level testing for substation automation systems

ActiveUS20100204948A1Resistance/reactance/impedenceError detection/correctionTime informationSystem testing

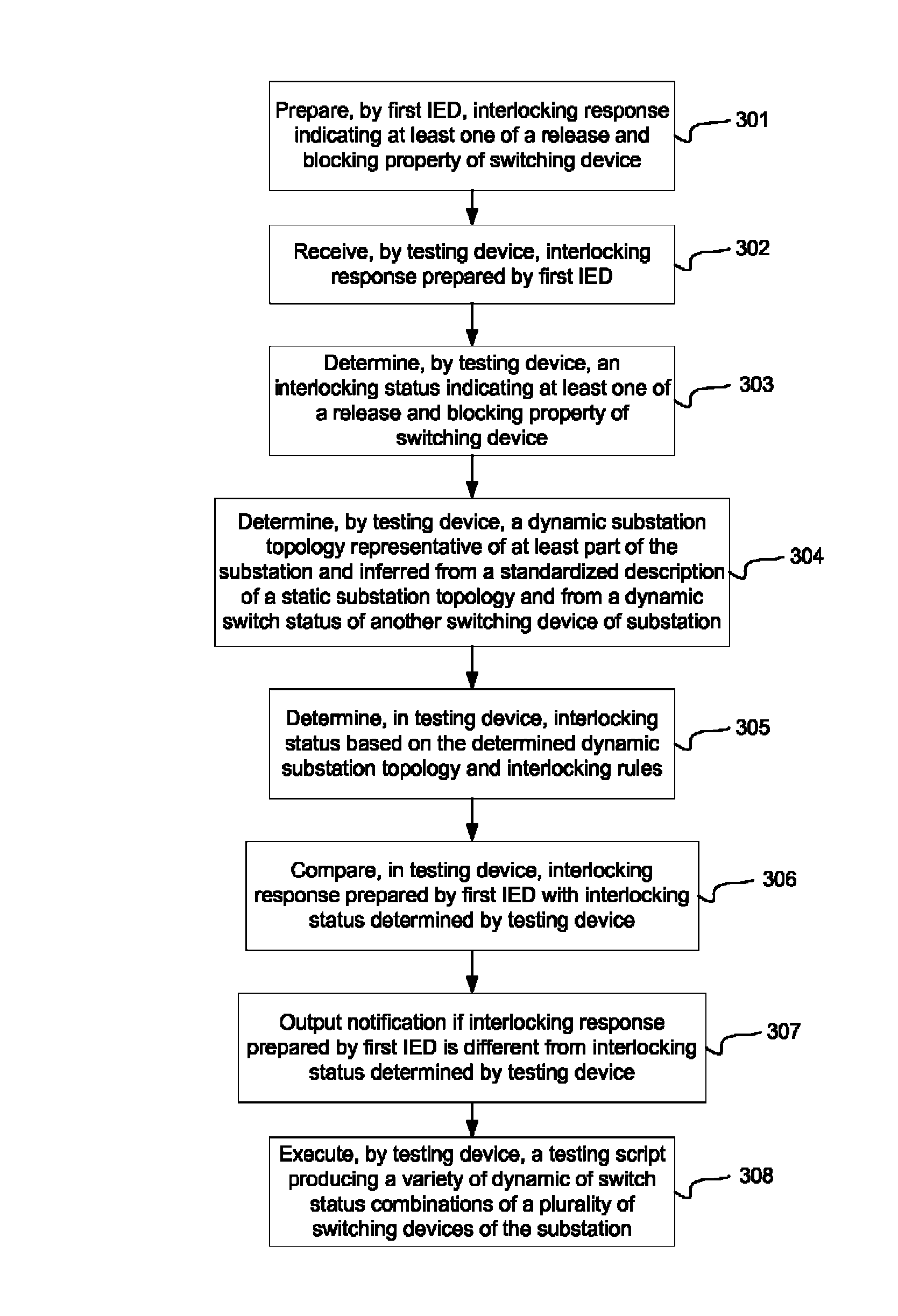

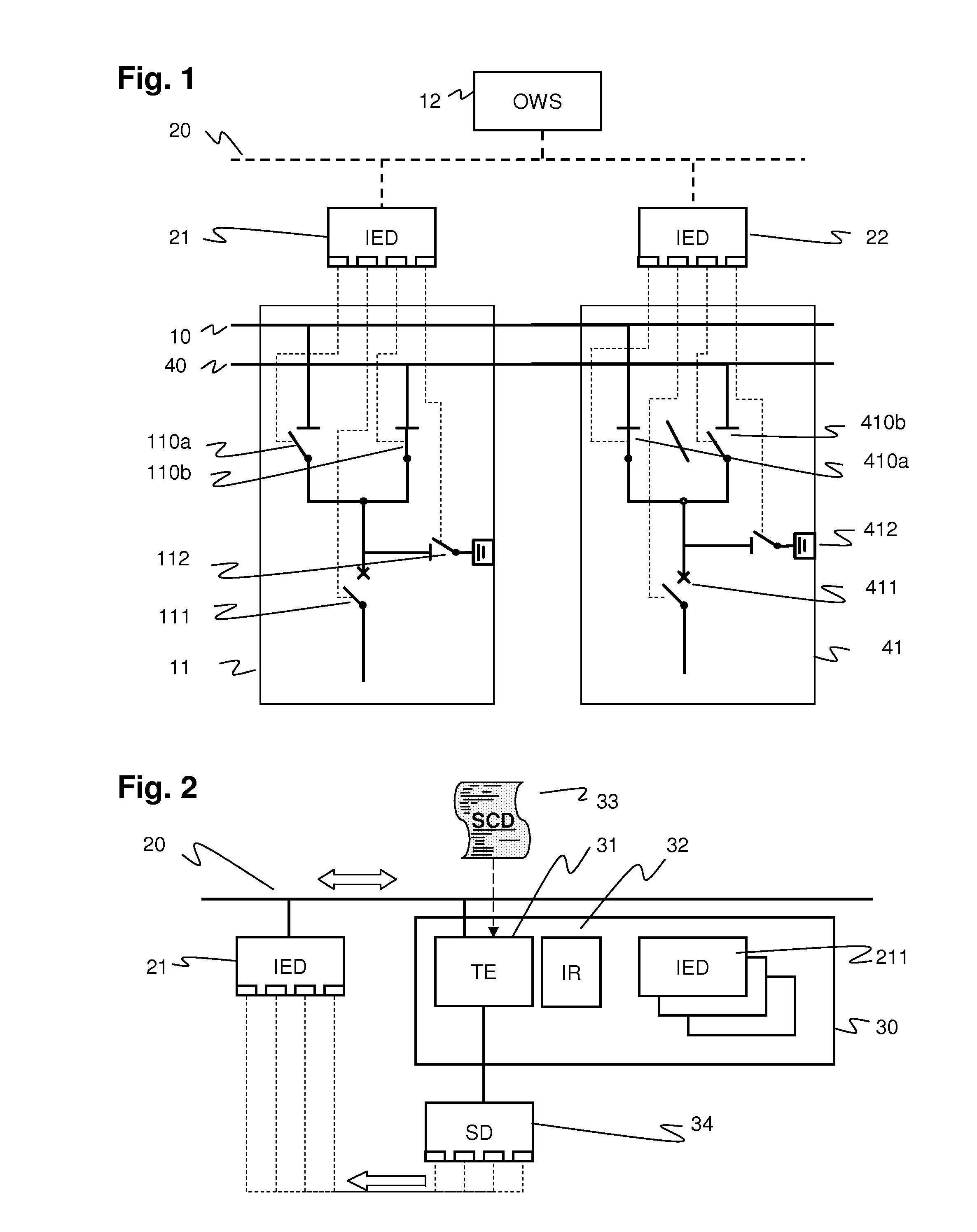

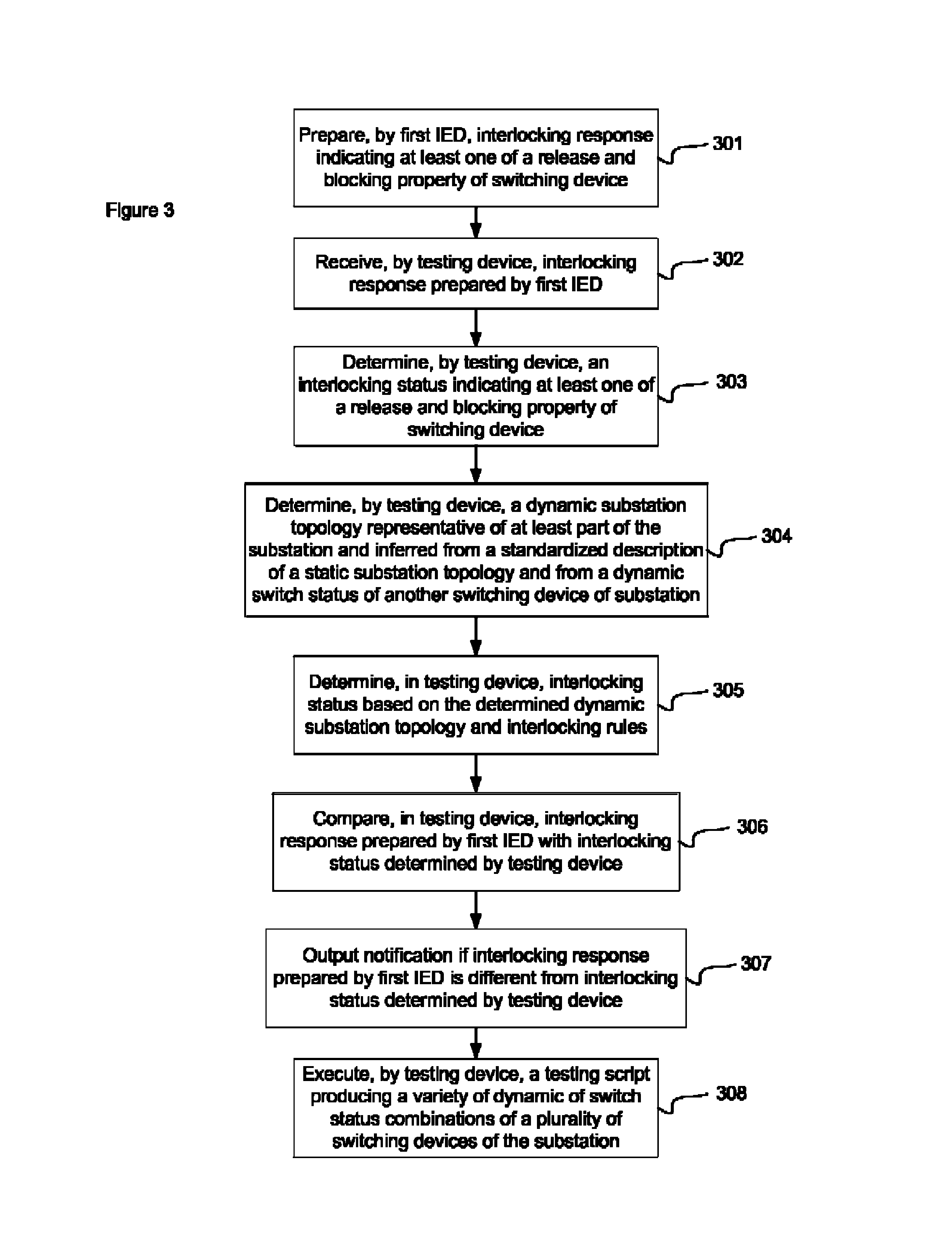

Protection, measurement and control IEDs in a substation compute if switches they control may be operated safely, according to interlocking rules or physical principles as well as the dynamic topology of the substation. The IEDs have access to the substation electrical topology, to real-time information generated by other IEDs, and to the rules for interlocking. A standardized Substation Configuration Description (SCD) of the substation for which a Substation Automation system is intended, and a standardized description of the implemented device functions or capabilities of an individual IED are utilized. The substation topology is available from SCD file, real time information about the position of switches and line voltage / current can be obtained via an appropriate protocol, and the interlocking rules are available in script form. These features apply both to simulated and real devices, and increase system testing possibilities by supporting an efficient configuration of a simulation.

Owner:HITACHI ENERGY SWITZERLAND AG

System level testing for substation automation systems

InactiveUS20090070062A1Easy to testData switching networksCircuit interrupters testingSystem testingEngineering

Owner:ABB RES LTD +1

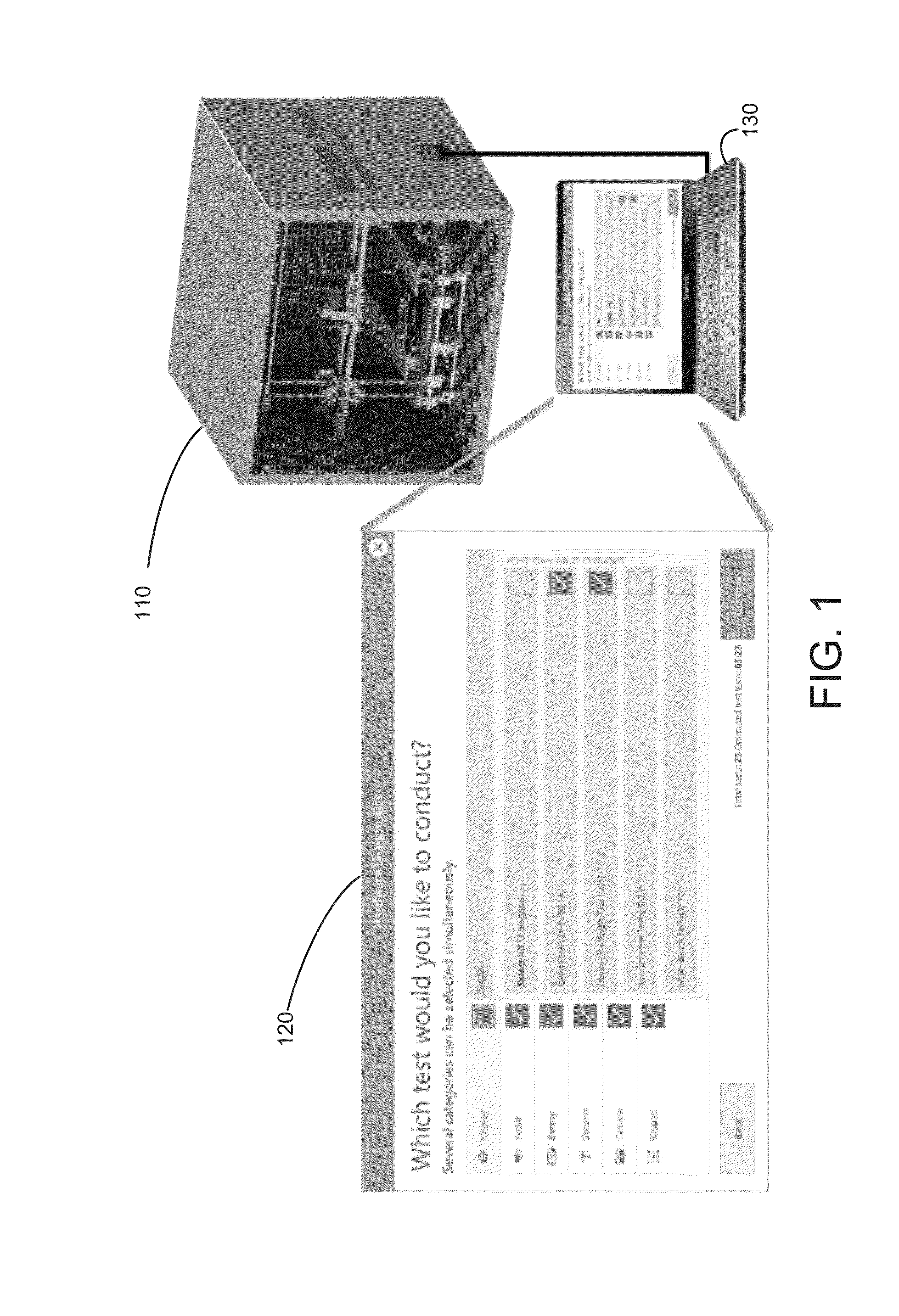

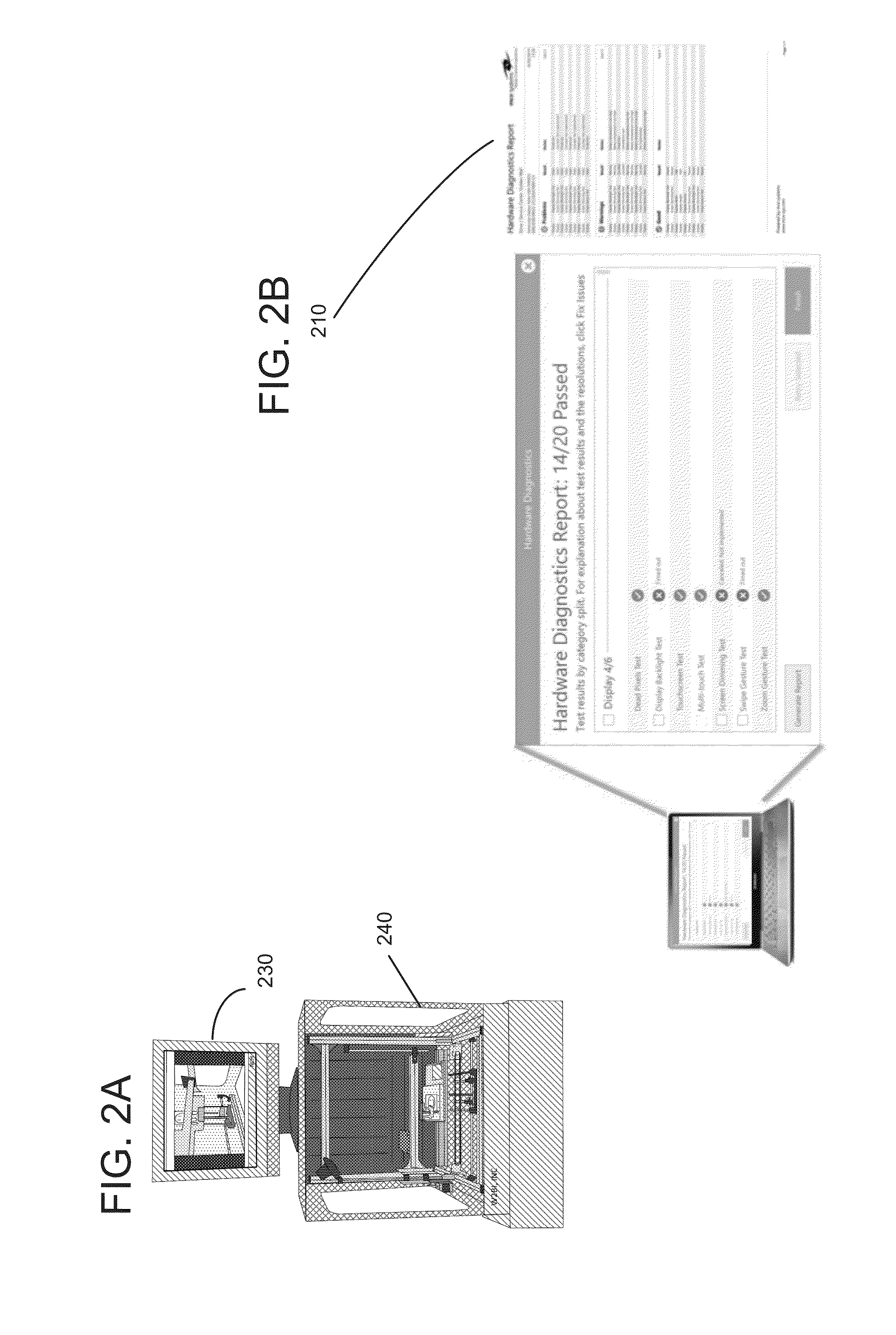

Smart box for automatic feature testing of smart phones and other devices

ActiveUS20160337053A1Reduce subjectivityShort durationProgramme controlProgramme-controlled manipulatorHuman interactionAutomatic control

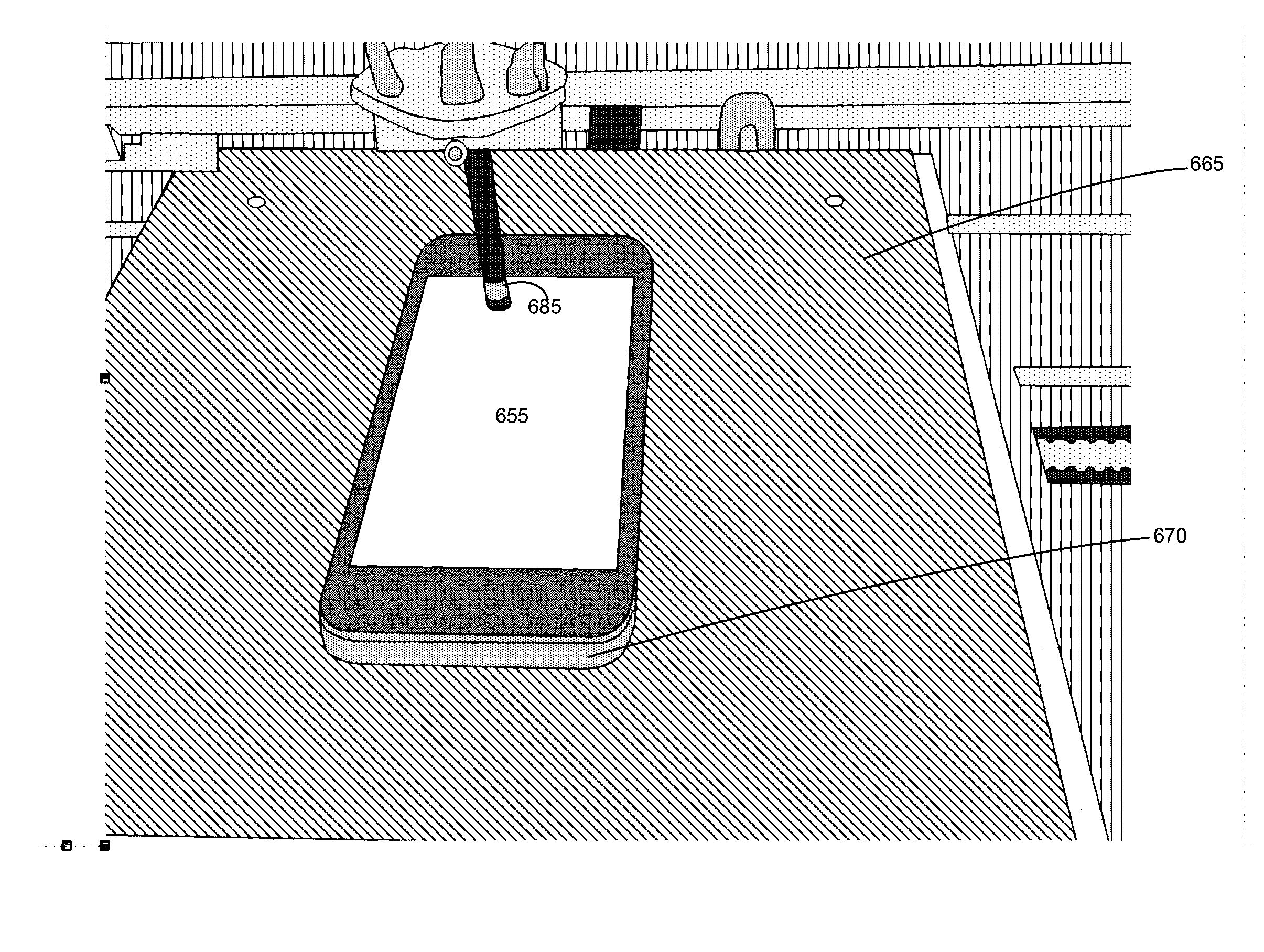

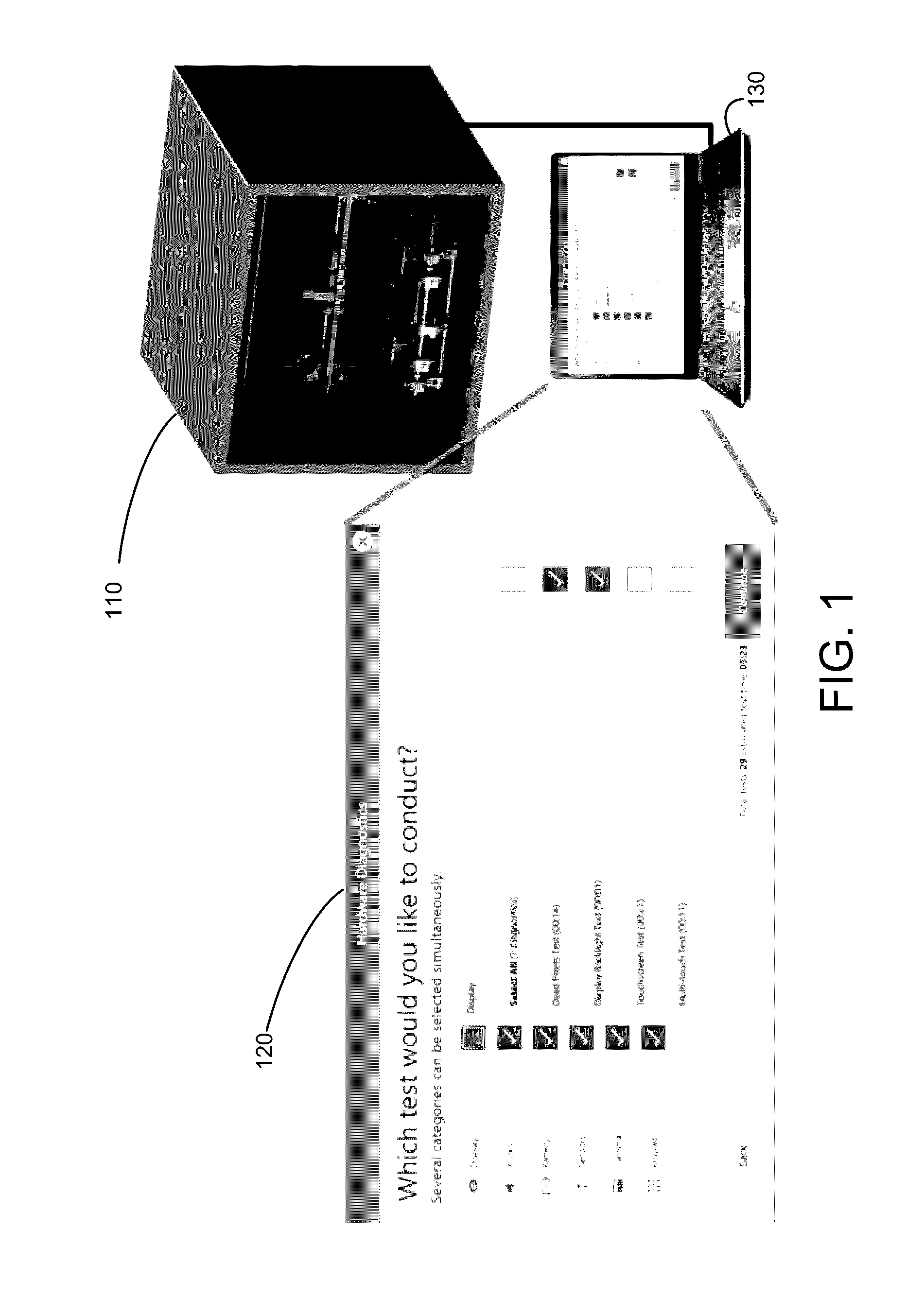

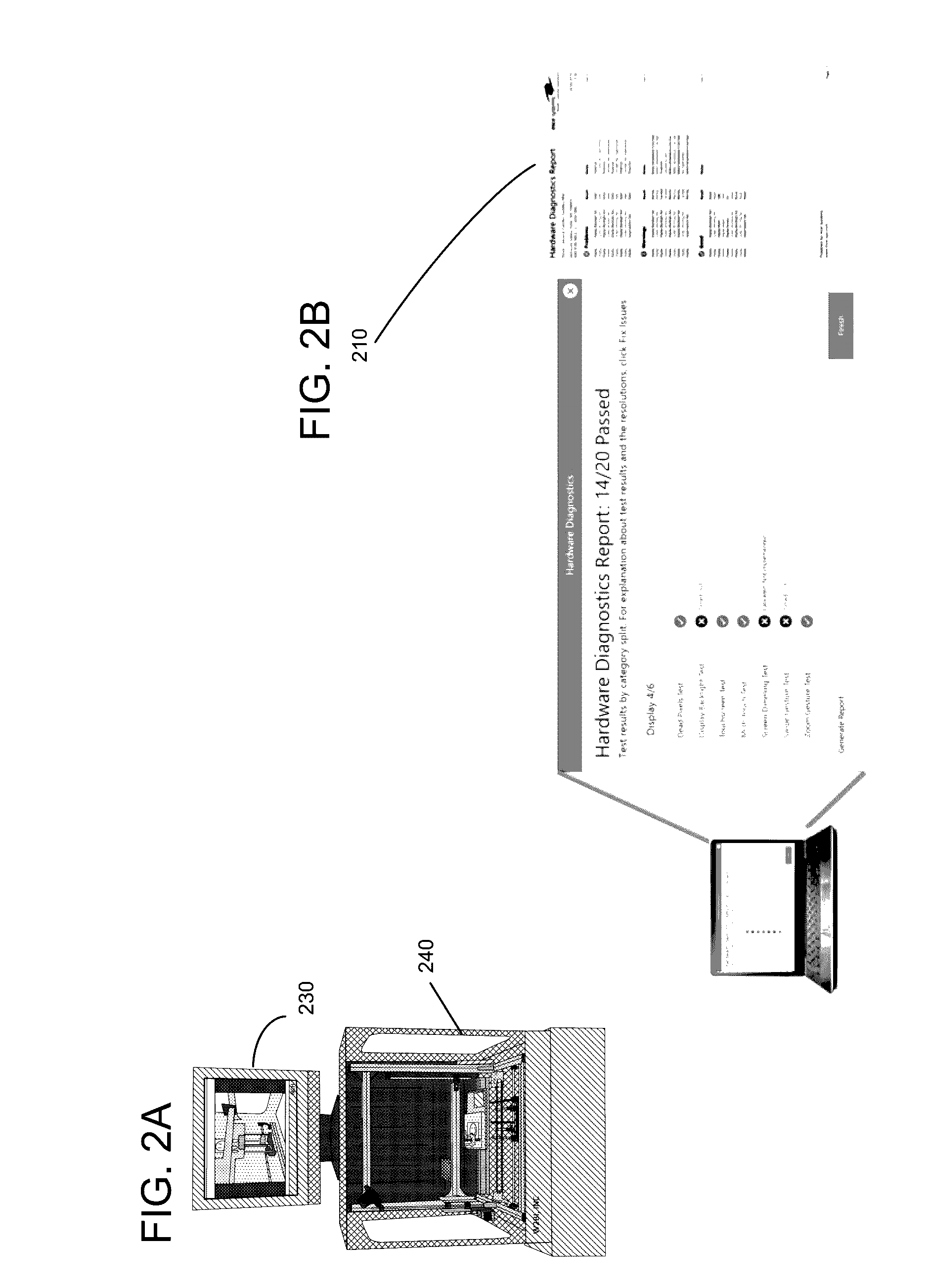

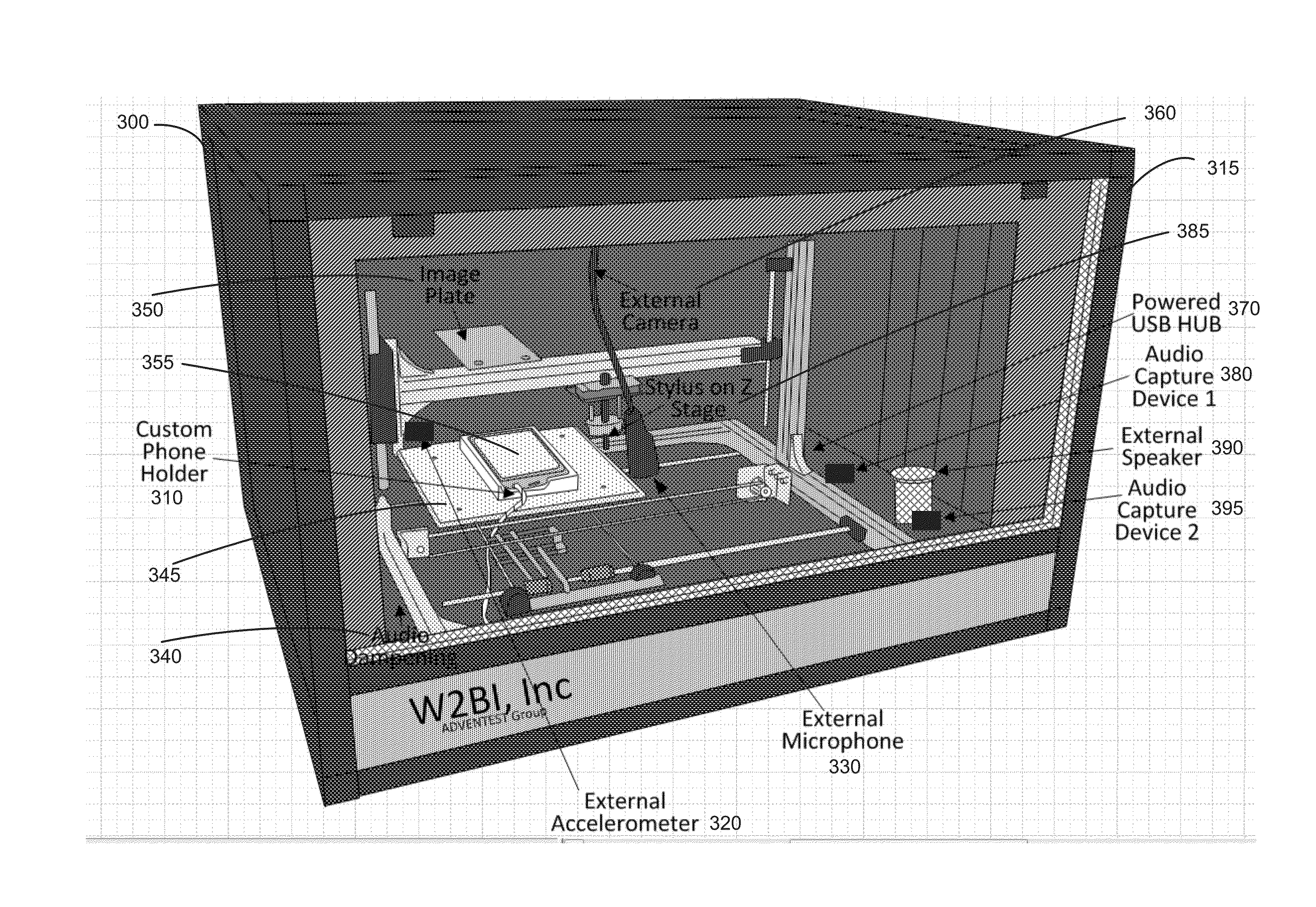

An automatic system level testing (ASLT) system for testing smart devices is disclosed. The system comprises a system controller operable to be coupled with a smart device in an enclosure, wherein the system controller comprises a memory comprising test logic and a processor. The system also comprises the enclosure, wherein the enclosure comprises a plurality of components, the plurality of components comprising: (i) a robotic arm comprising a stylus, wherein the stylus is operable to manipulate the smart device to simulate human interaction therewith; and (ii) a platform comprising a device holder, wherein the device holder is operable to receive a smart device inserted there into. The processor is configured to automatically control the smart device and the plurality of components in accordance with the test logic.

Owner:ADVANTEST AMERICA

Methodology of using the various capabilities of the smart box to perform testing of other functionality of the smart device

ActiveUS20160192213A1Reduce subjectivityShort durationTransmitters monitoringProgramme-controlled manipulatorAutomatic controlRobotic arm

An automatic system level testing (ASLT) system for testing smart devices is disclosed. The system comprises a system controller coupled to a smart device in an enclosure, wherein the system controller comprises a memory comprising test logic and a processor. The enclosure comprises a plurality of components, wherein the processor is configured to automatically control the smart device and the plurality of components in accordance with the test logic. The plurality of components comprises: (a) a robotic arm comprising a stylus affixed thereto; and (b) a platform comprising a device holder affixed thereto, wherein the smart device is inserted into the device holder; and (c) a wireless access point. The processor is further configured to: (a) control the smart device to activate wireless mode; (b) receive wireless signals from the wireless access point using the smart device; (c) retrieve wireless scan results from the smart device; and (d) analyze the wireless scan results.

Owner:ADVANTEST AMERICA

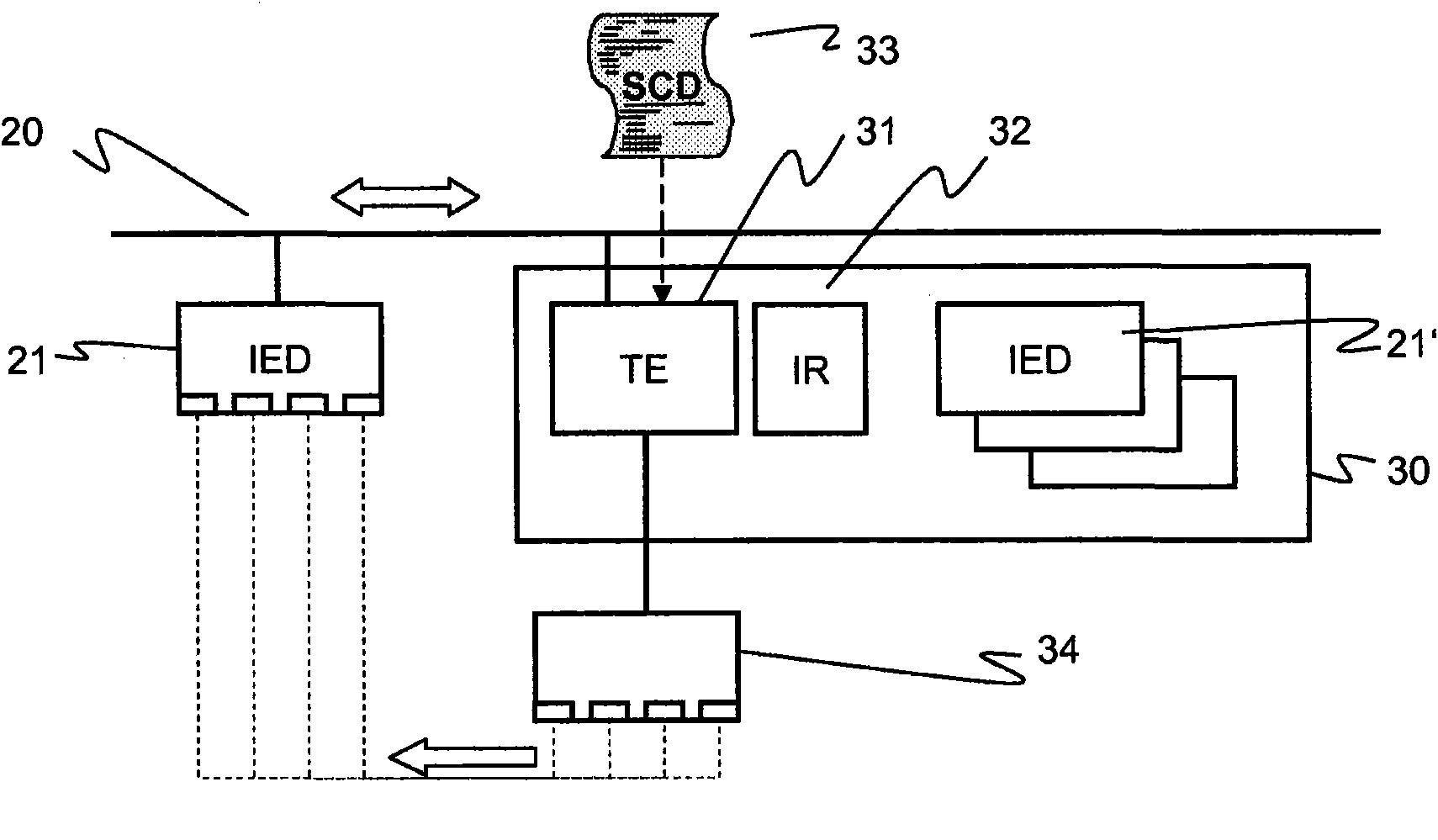

System level testing for substation automation systems

ActiveCN101432633AData switching networksCircuit interrupters testingSystem testingEquipment under test

The invention is concerned with the testing of system level functionality involving several Protection. Control and Measurement (PCM) Intelligent Electronic Devices (IEDs) of a Substation Automation (SA) system for IEC 61850 compliant substations. An extensive testing of all conceivable control or protection functions / applications of an extended SA system comprising a large number of IEDs with a multitude of configurations is facilitated by simulating at least one of the IEDs in a testing device. Hence, only a limited number of IEDs are physically present as individual devices in a test environment, the behaviour of at least one further IED being simulated by a dedicated testing device with appropriate data processing means. The testing device sends network messages indicative of the behaviour of the simulated IED according to its communication and device configuration over a substation communication network to the physically present IED to be tested. The proper working of the configured IED functions, i.e. the expected correct action as triggered by the testing device, are then verified by analyzing the device's response over its analogue and digital outputs, as well as its response over the communication network. Preferably, the set-up for SA system testing is automatically detected and configured.

Owner:HITACHI ENERGY SWITZERLAND AG

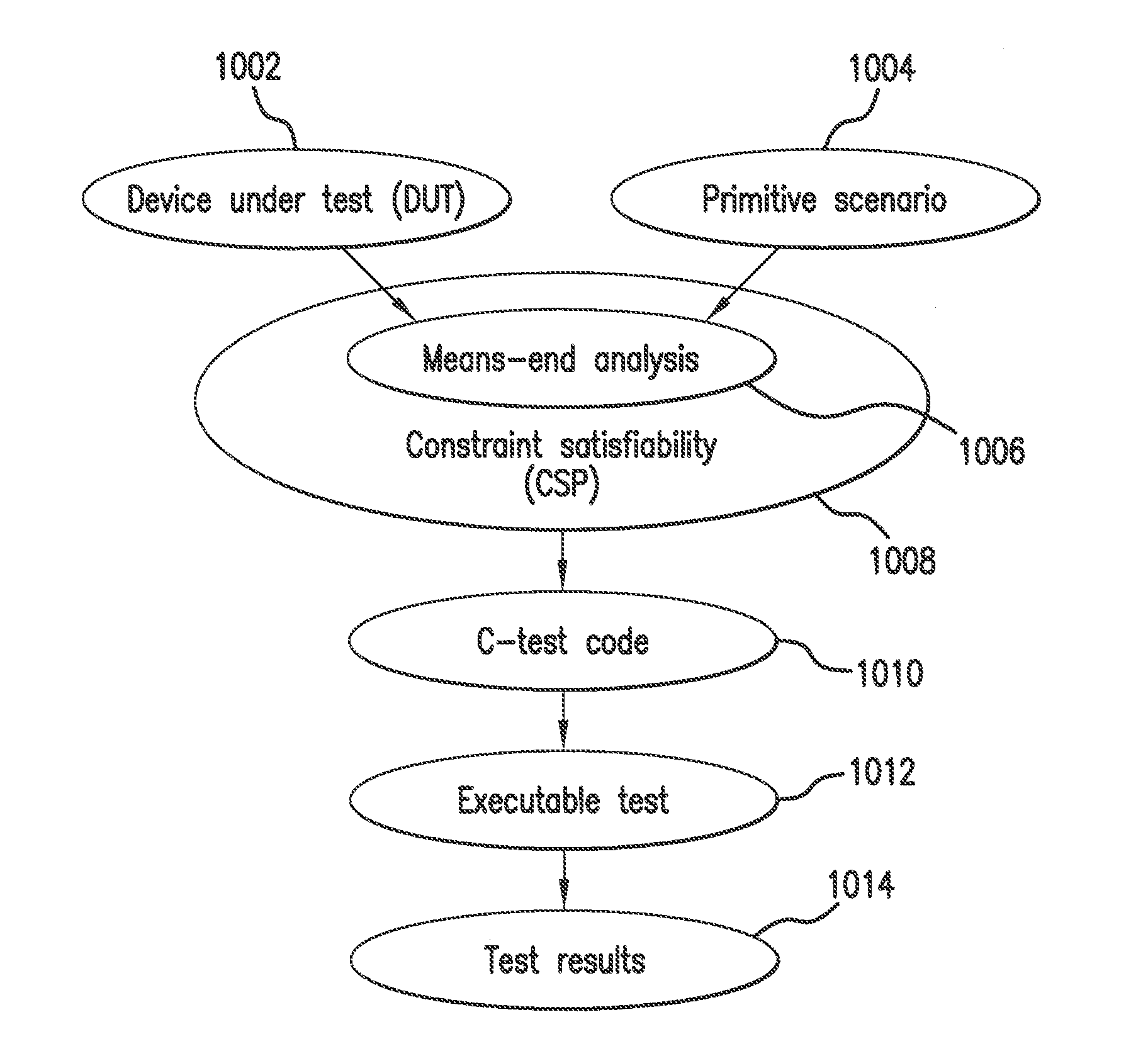

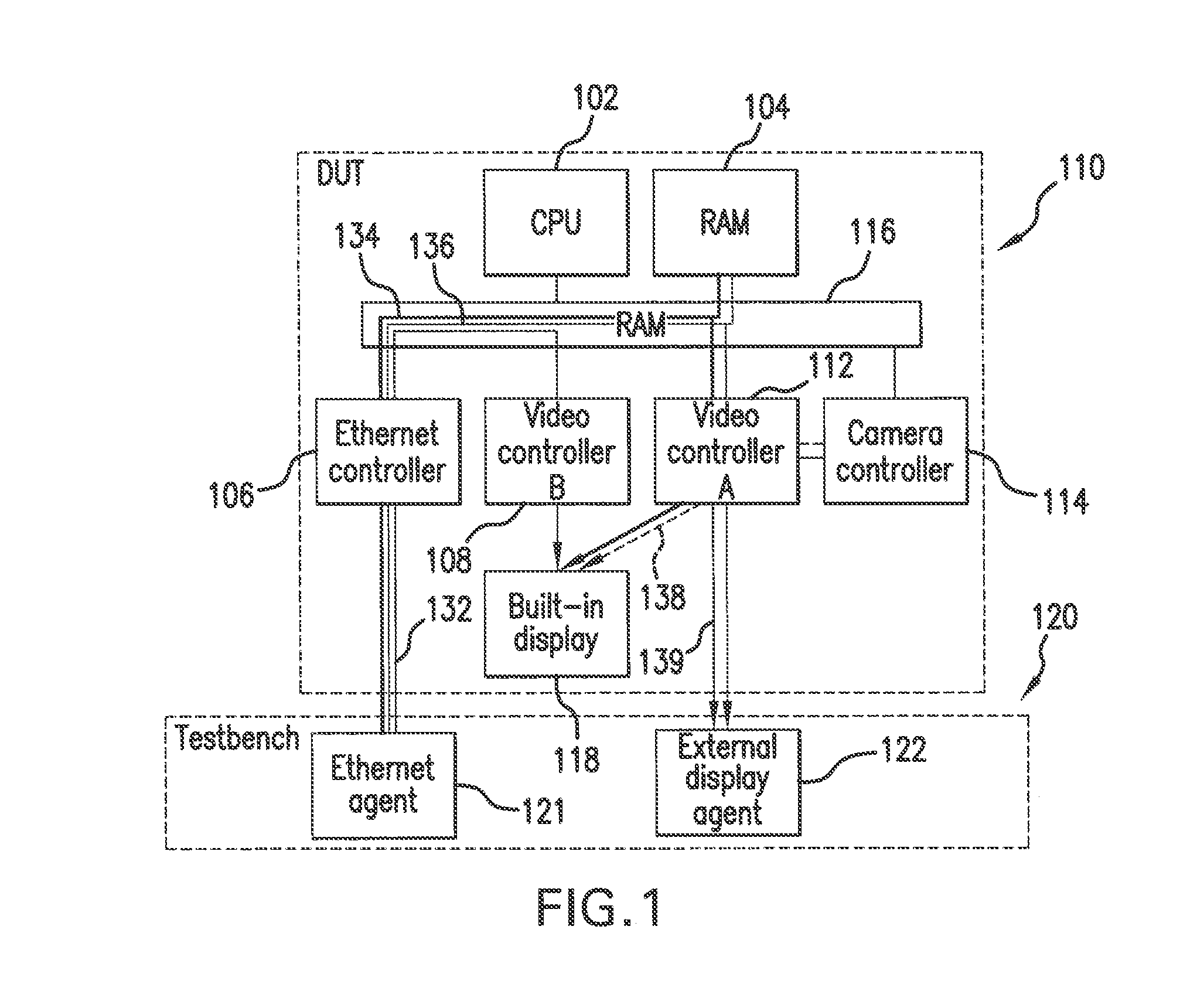

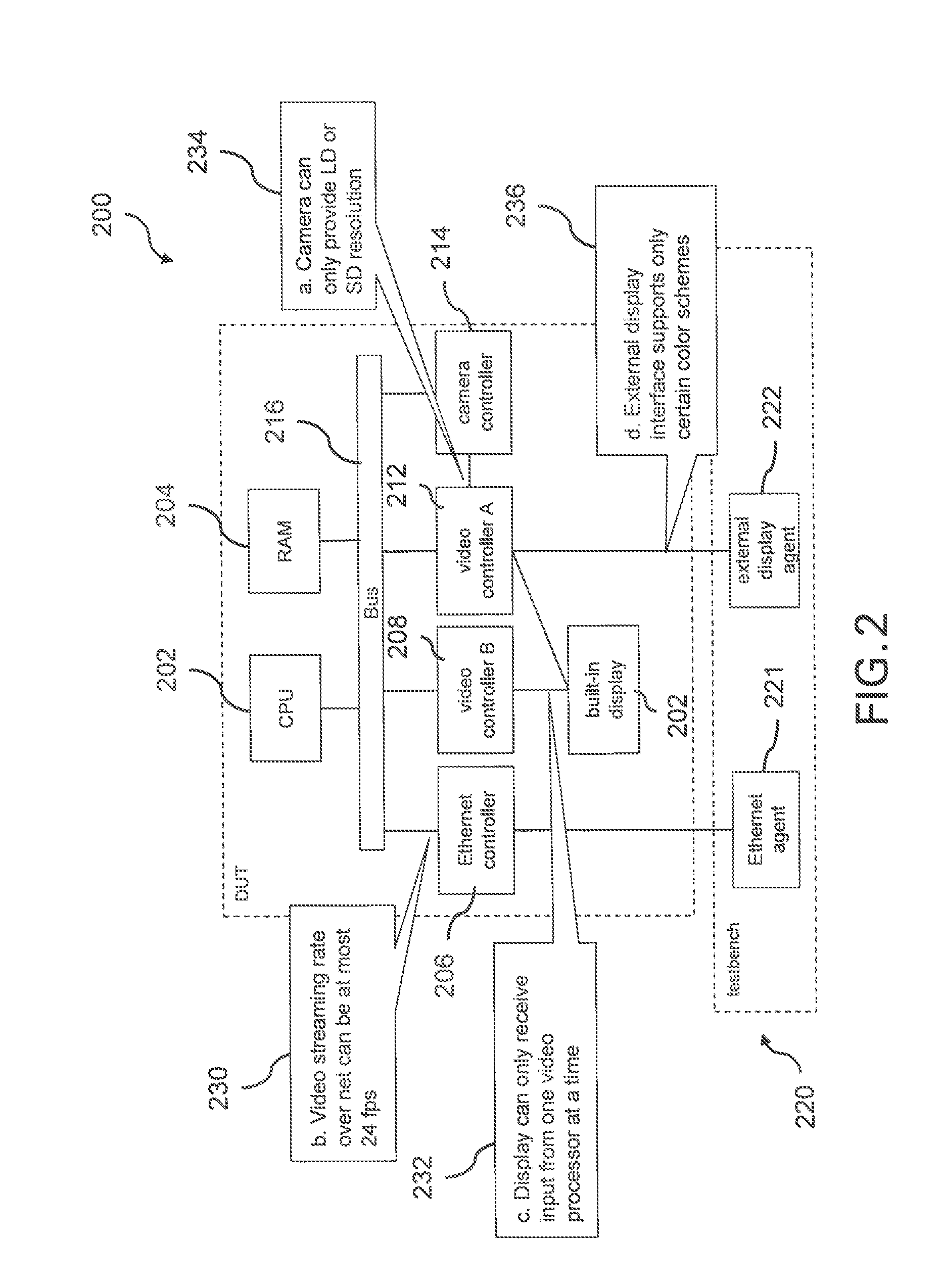

Systems and methods for automatically generating executable system level-tests from a partially specified scenario

ActiveUS8560893B1Improve the level ofElectronic circuit testingError detection/correctionProgramming languageSystem level testing

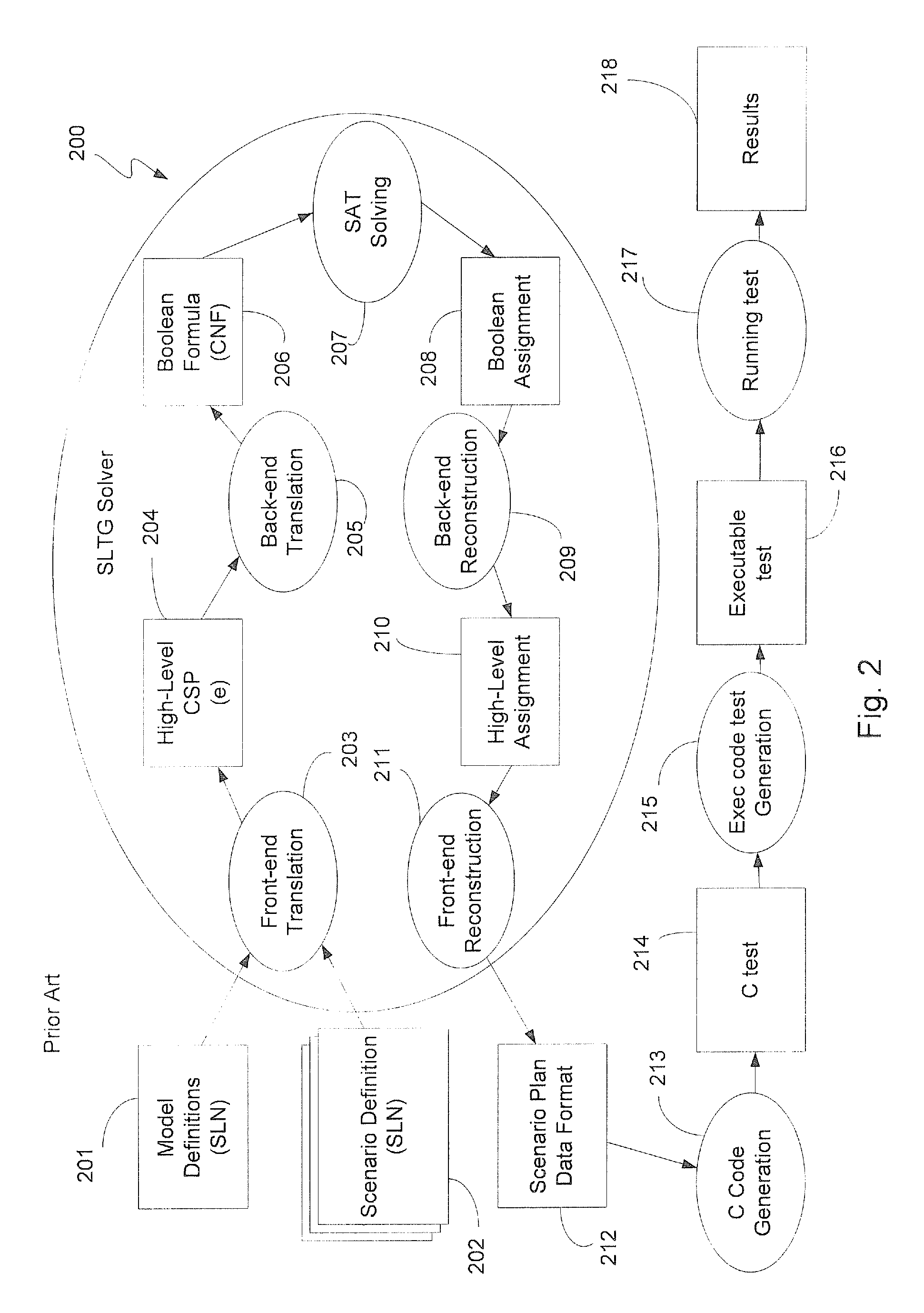

A method and system are provided for automatically generating executable system-level tests from an initial action or partially specified scenario by accumulating necessary complement actions and forming a set of constraints required by the initial action and the necessary complement actions. The set of constraints is solved by a constraint solving engine to provide an at least partial sequence of the actions and parameters thereto that satisfies the set of constraints. The sequence of actions that comply with the set of constraints are used to generate an executable system-level test code.

Owner:CADENCE DESIGN SYST INC

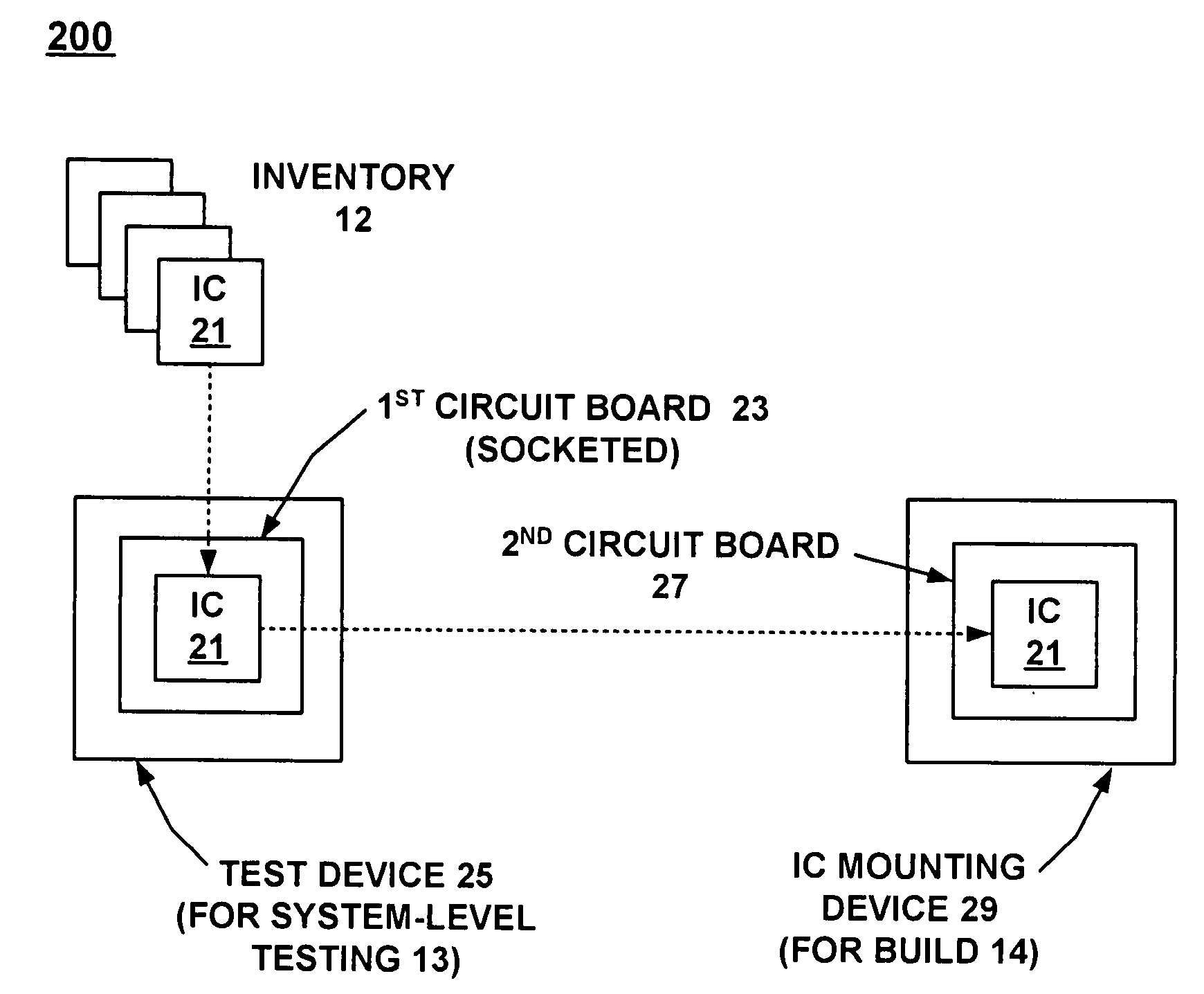

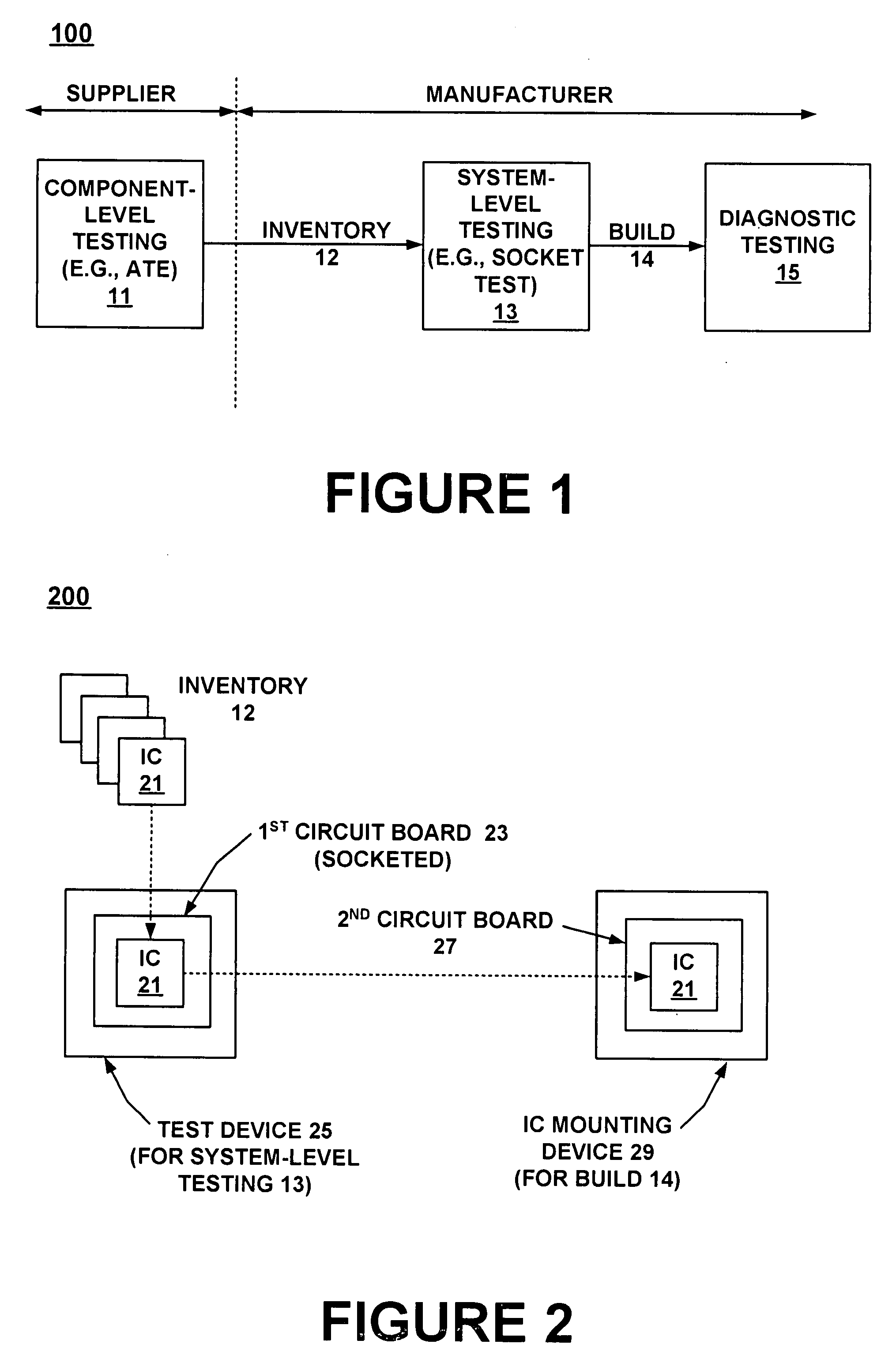

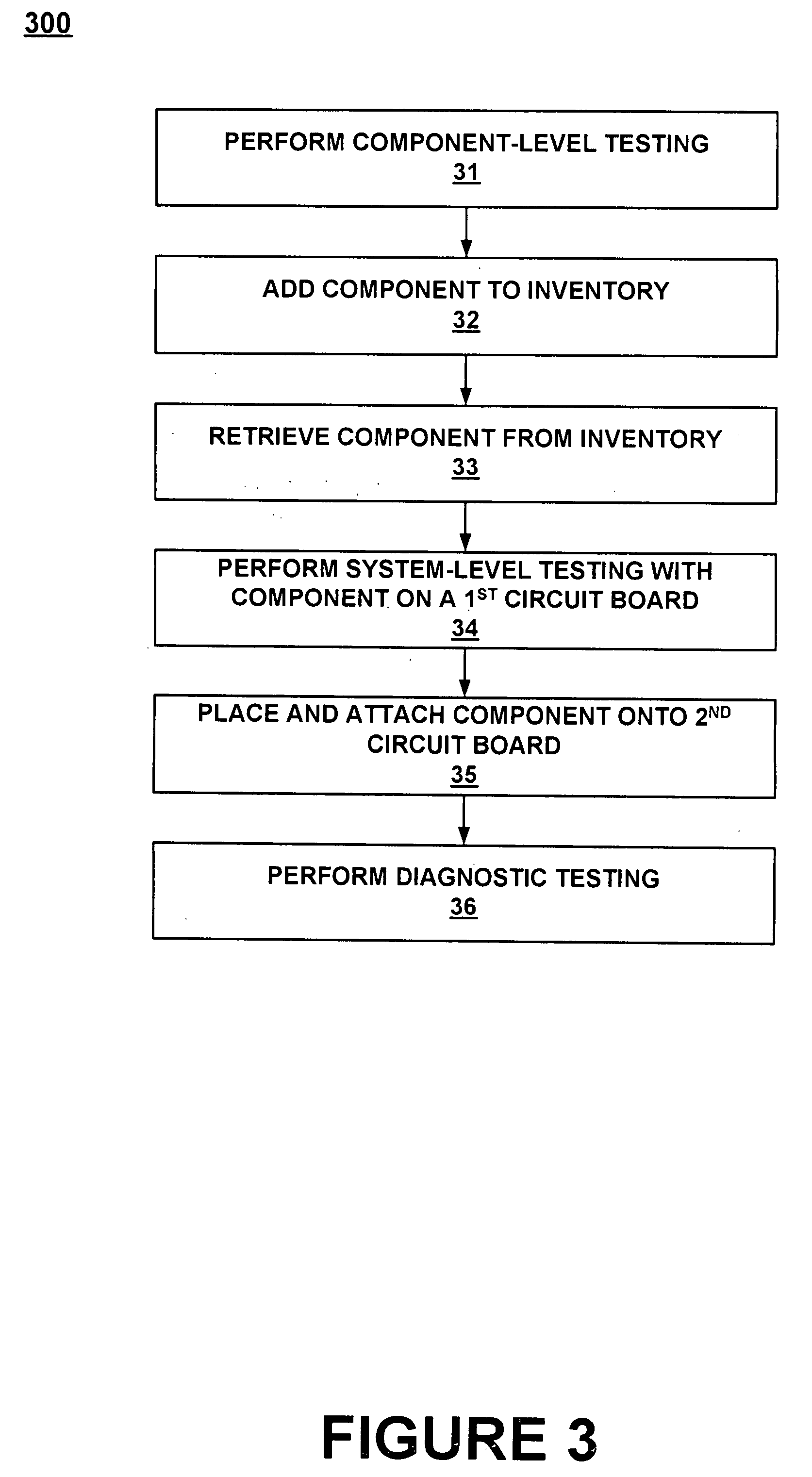

In-process system level test before surface mount

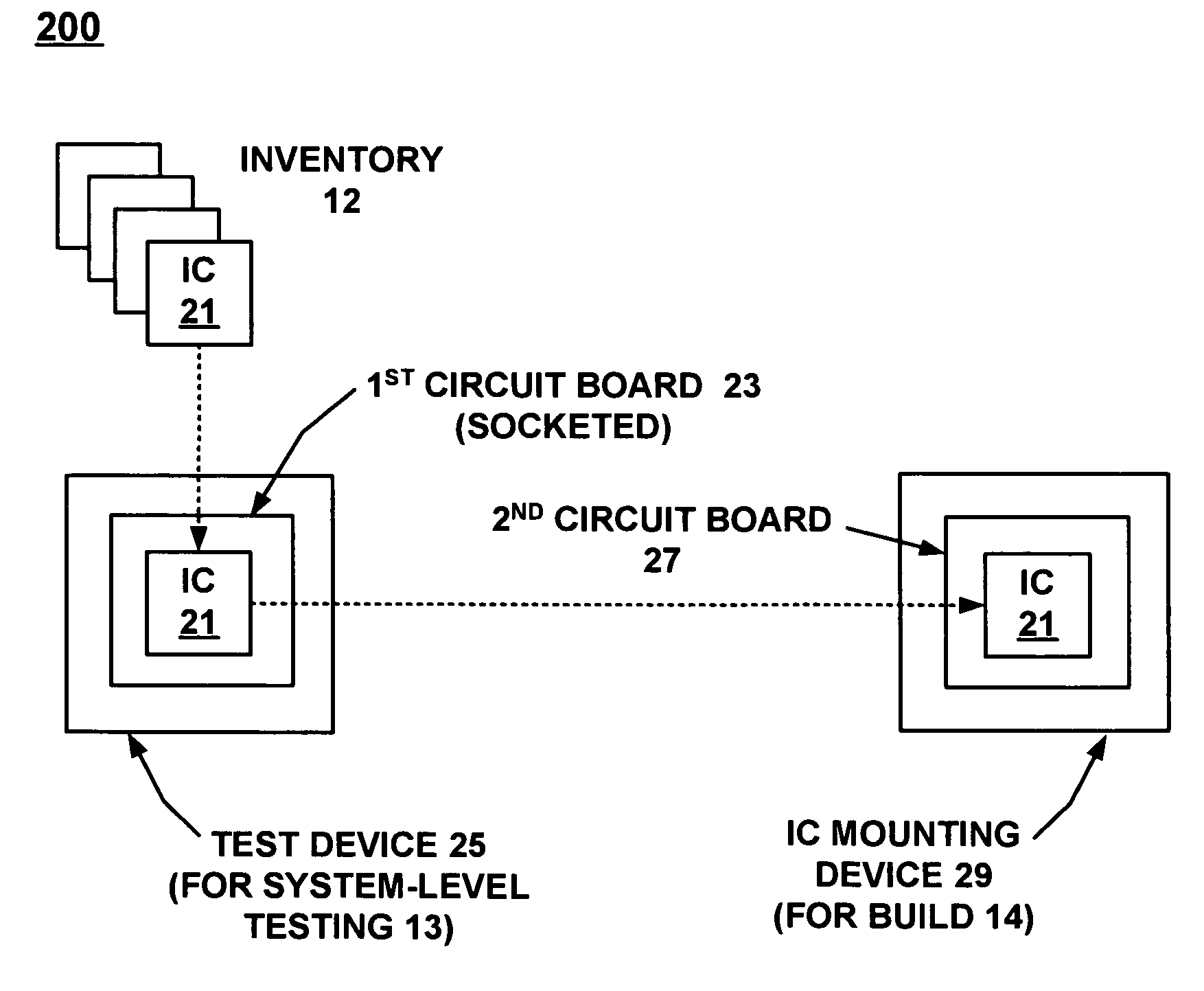

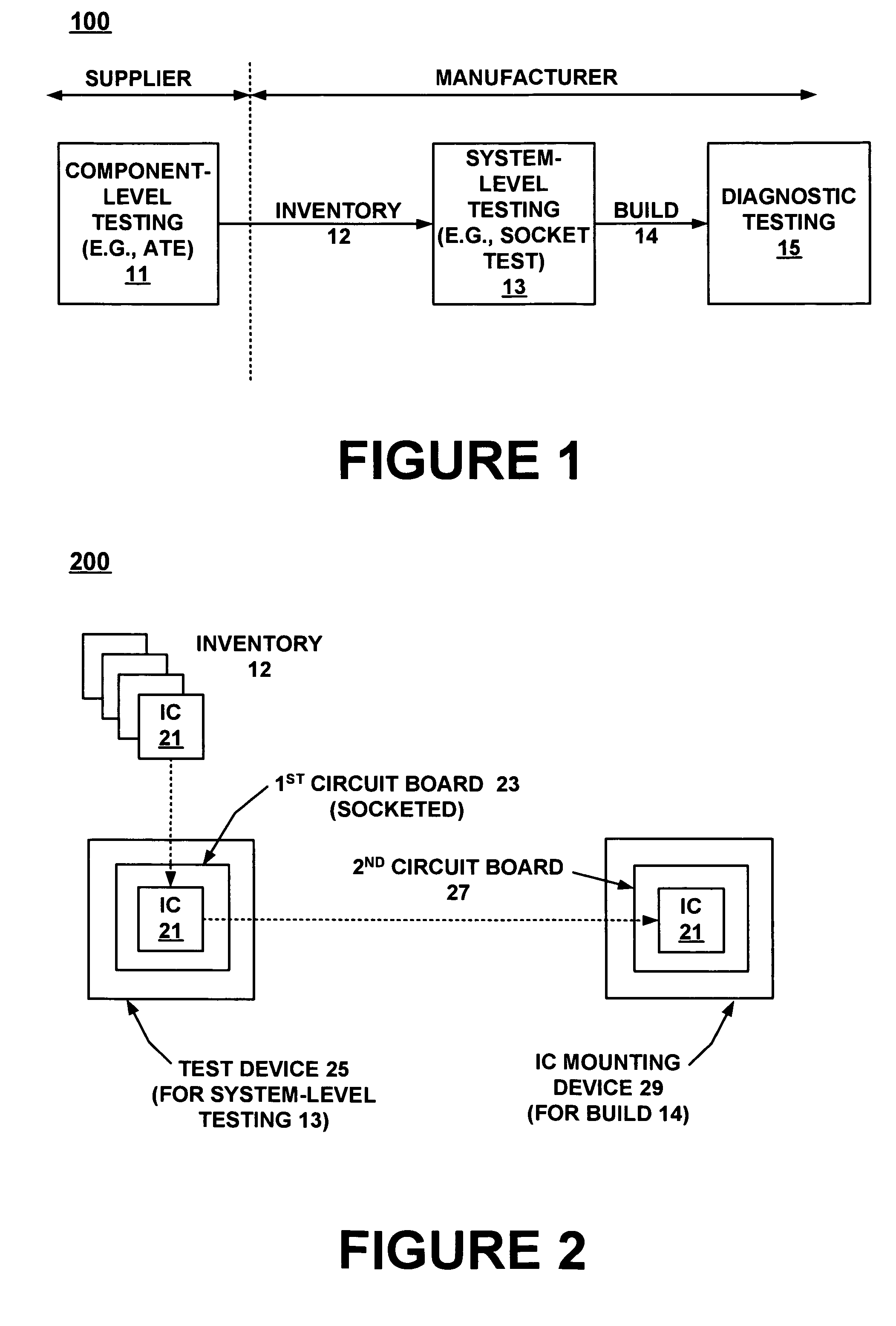

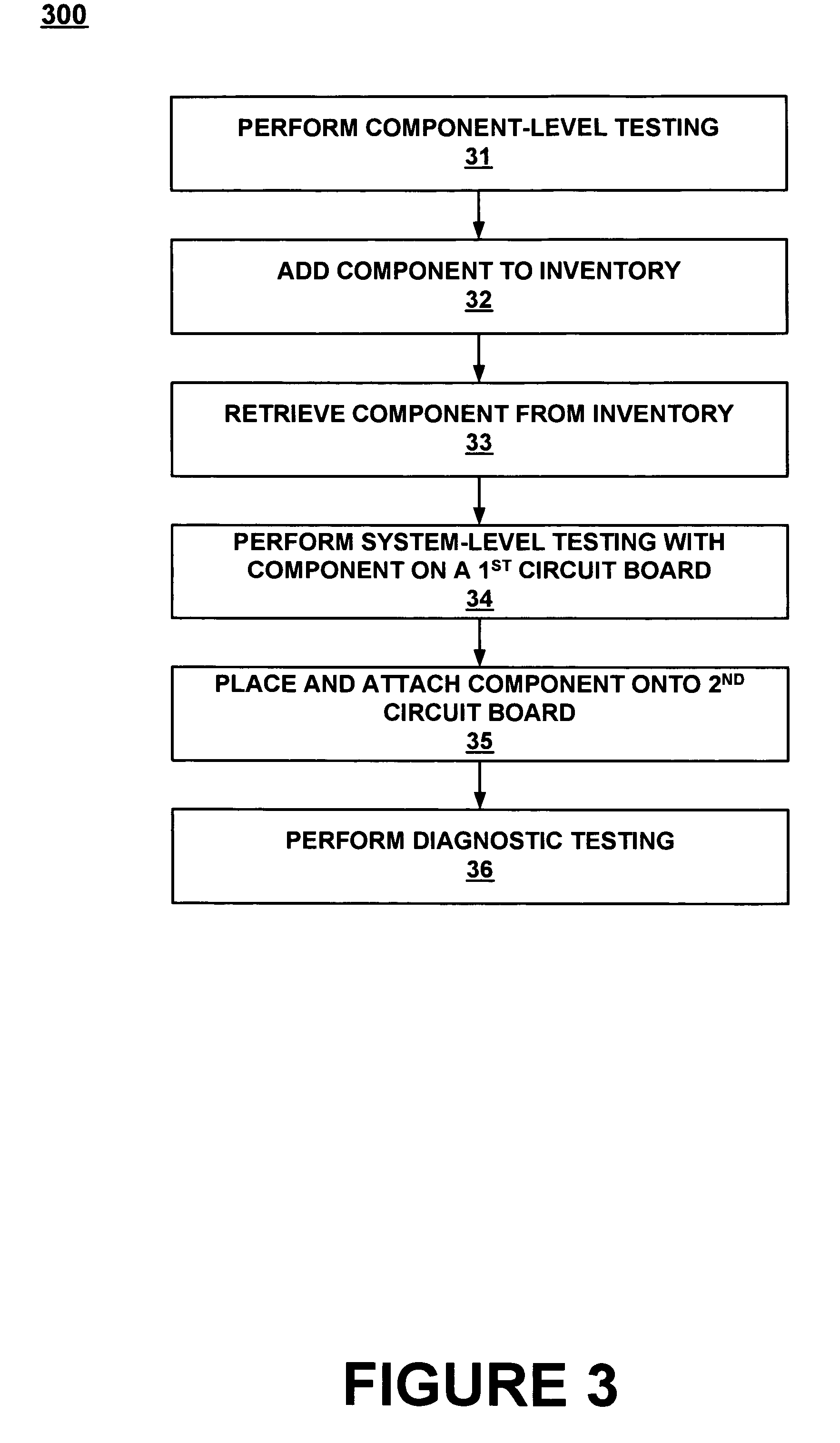

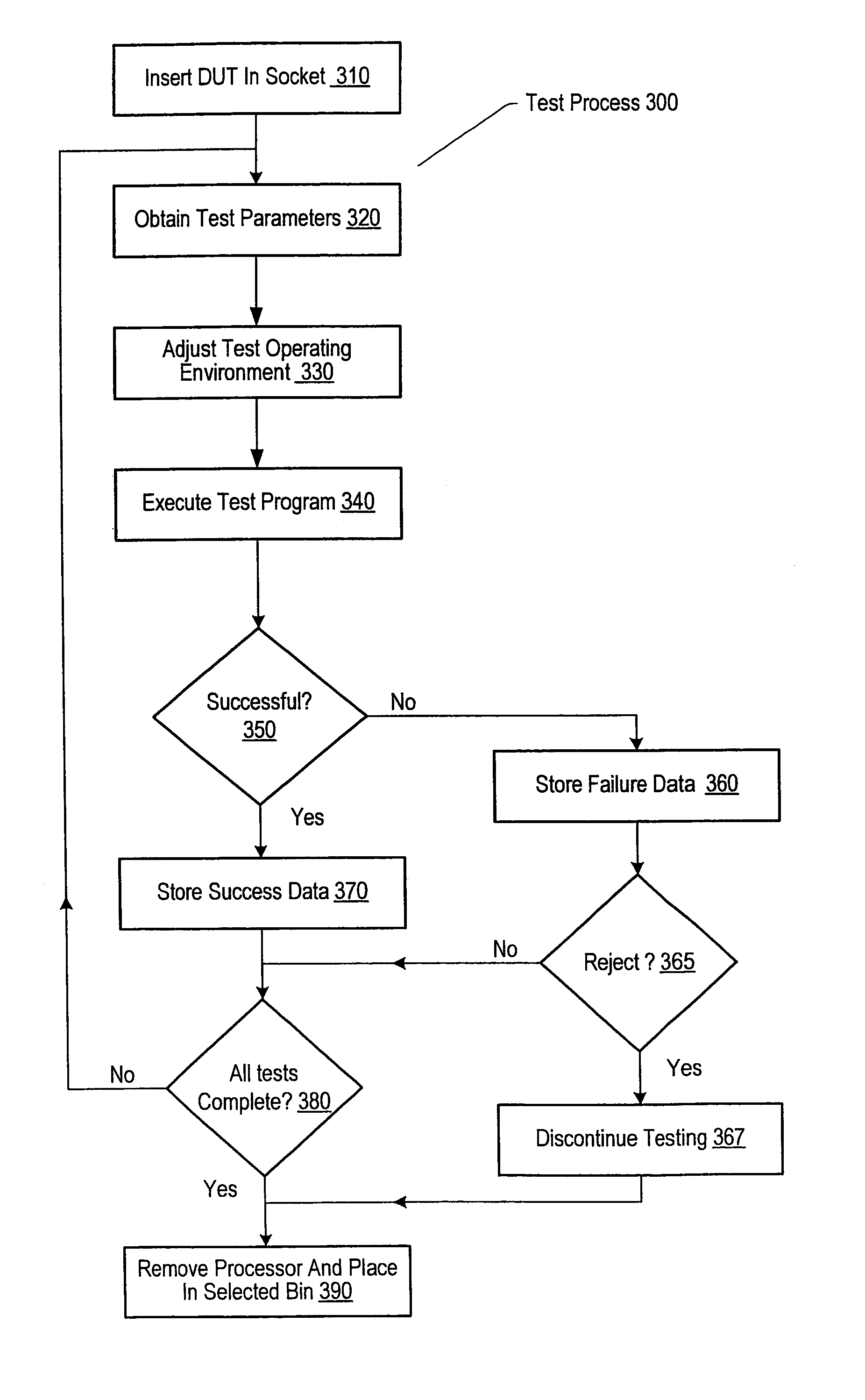

InactiveUS7279887B1Reduce wasteLow costElectronic circuit testingIndividual semiconductor device testingProcess systemsSurface mounting

Methods and systems for testing an integrated circuit during an assembly process are described. The integrated circuit is received from inventory. The integrated circuit is placed in a socket on a first circuit board for system-level testing. The system-level testing is performed prior to placement and permanent attachment of the integrated circuit onto a second circuit board. Provided the integrated circuit passes the system-level testing, the placement and permanent attachment of the integrated circuit to the second circuit board is the next step following the system-level testing in the assembly process.

Owner:NVIDIA CORP

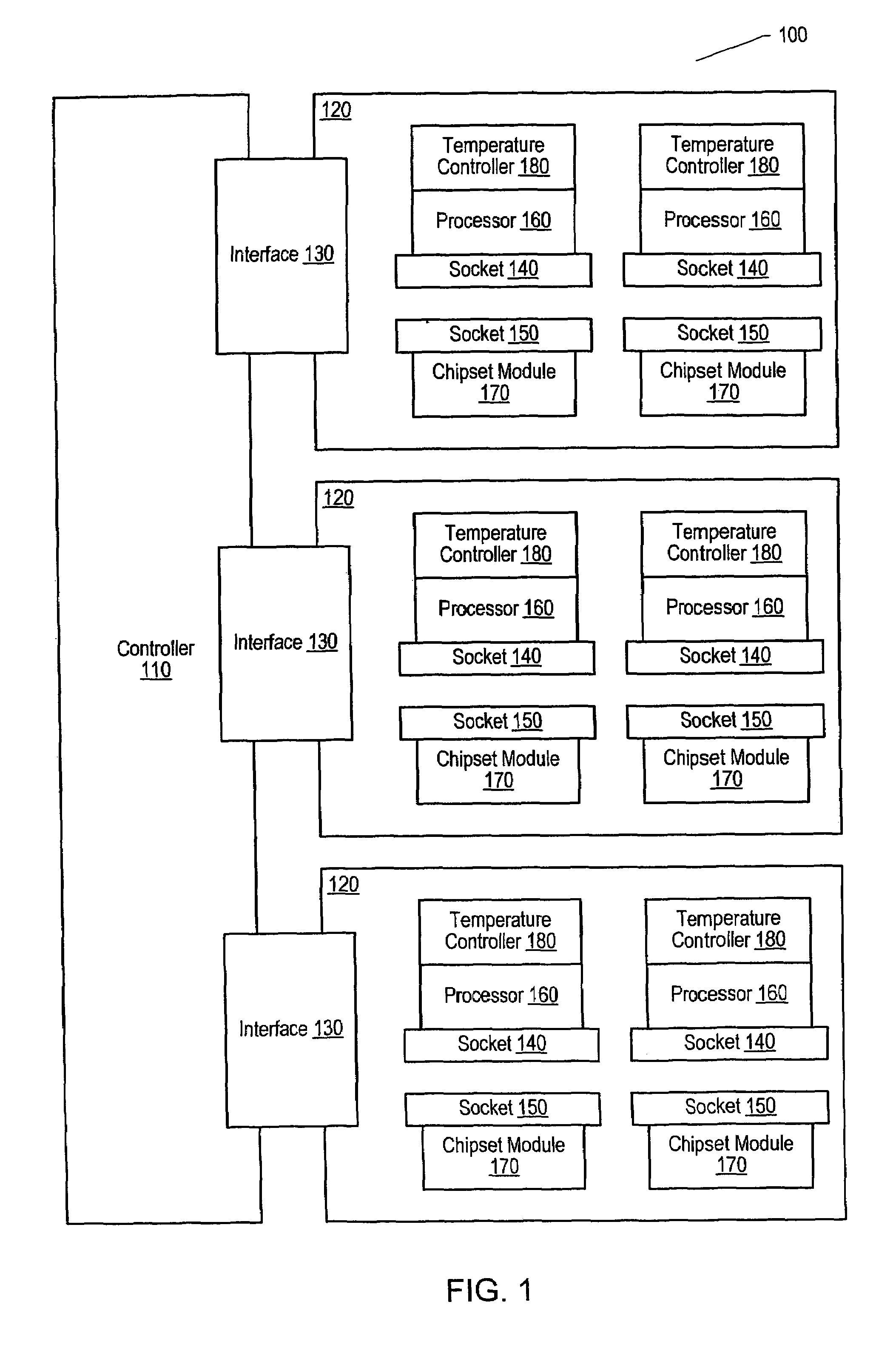

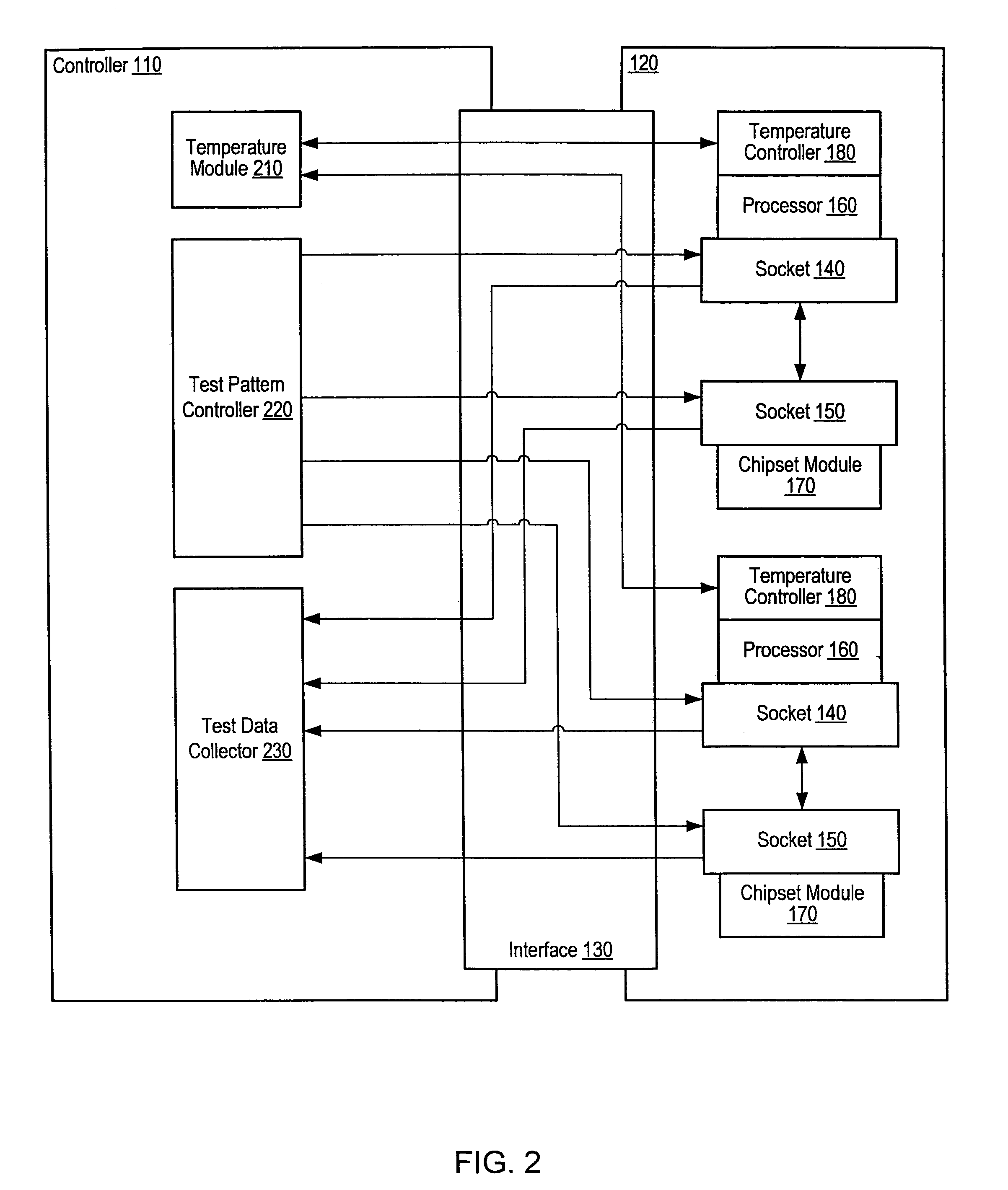

Burn-in using system-level test hardware

InactiveUS7519880B1Electronic circuit testingError detection/correctionTemperature controlEngineering

A burn-in test system. A burn-in test system includes a device under test (DUT), a temperature controller coupled to the DUT, and a test controller. During testing, the test controller: (a) sets a parameter of the DUT to a first value and applies a test stimulus to the DUT, and (b) sets the parameter of the DUT to a second value and applies the test stimulus to the DUT. A change in the value of the parameter results in a change in the amount of heat dissipated by the DUT. The temperature controller maintains the DUT at a pre-determined temperature during testing with the parameter set to both the first and the second values. The DUT may be further coupled to a module that comprises circuitry employed in a product-level application environment. The module is configured by the test controller to simulate a product-level application.

Owner:GLOBALFOUNDRIES INC

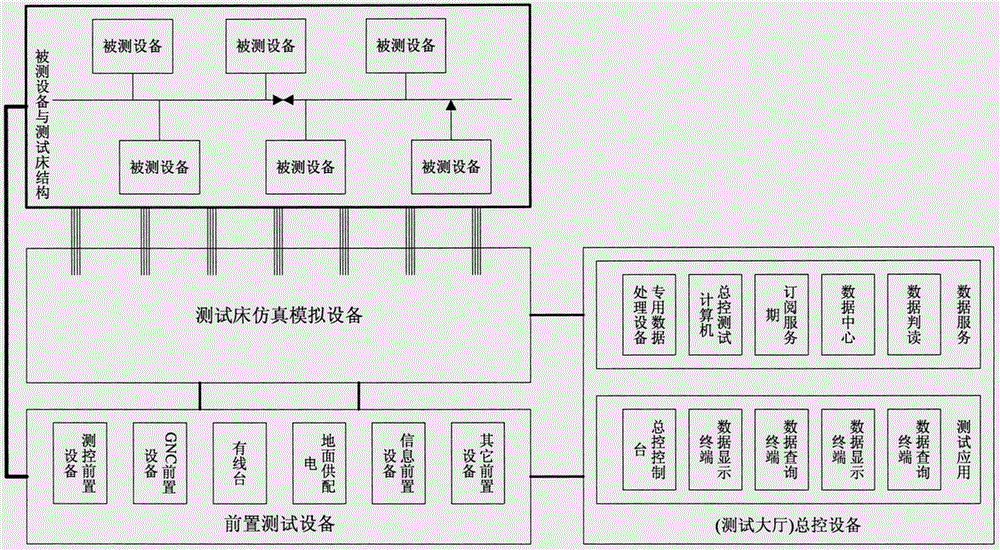

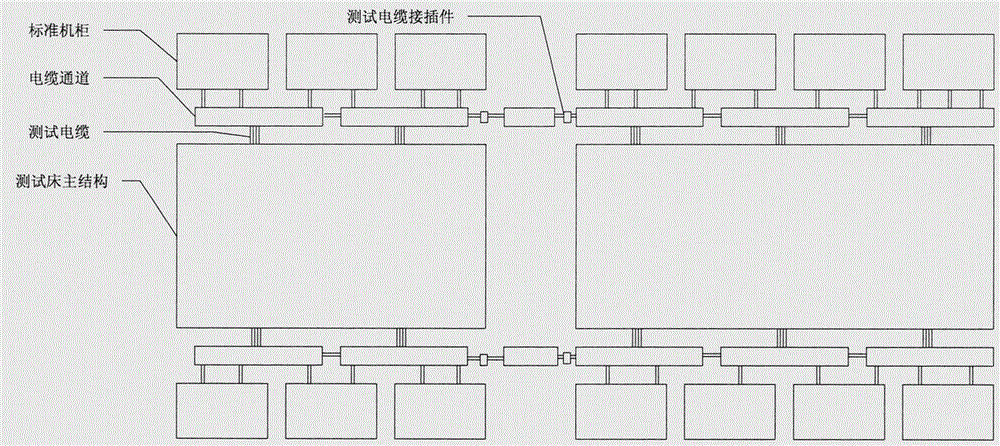

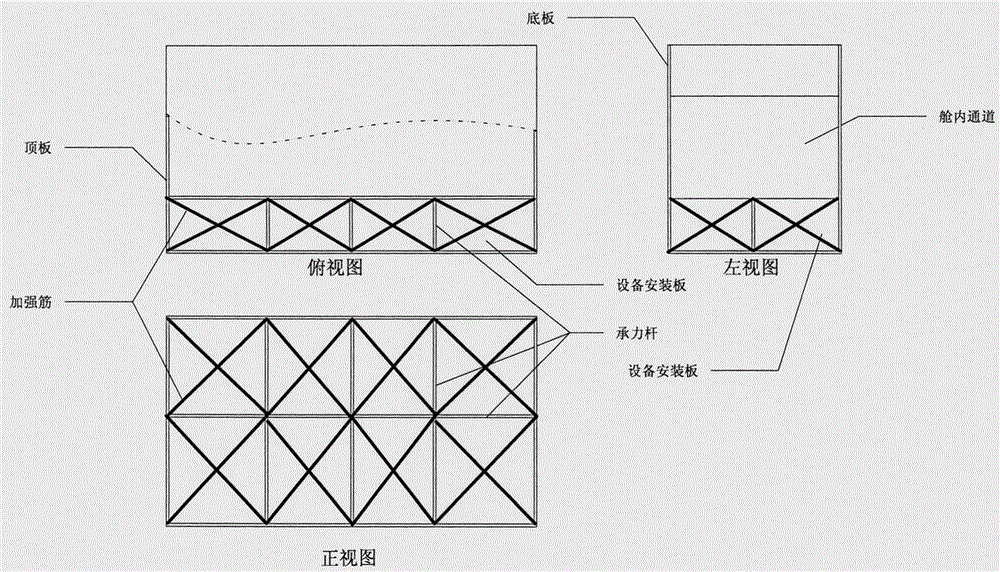

General spacecraft ground test bed system

ActiveCN105892305AImprove test effectivenessEasy to assemble and disassembleSimulator controlElectricityResource consumption

The present invention provides a general spacecraft ground test bed system. The system comprises a test bed structure; a test bed simulation device configured to realize the general simulation of electric interfaces, electrical property equivalence of a dynamo-electric device, onboard flight environment simulation and the electrical interface simulation of an external system; a preposition test device; and a general control device located at a testing hall. The test bed structure employs freely splitting and combining open-type framework rack, and the open-type framework rack employs a bearing rod, an installing plate and a bearing rod joint. The test bed simulation device comprises a 1553B bus simulator, a power supply and distribution simulator, an Ethernet communication simulator and a simulation service and controller. The general spacecraft ground test bed system is able to develop a system-grade test prior to the completion of single unit equipment so as to conveniently and effectively discover abnormal single units having dismounting problems and process the low hierarchy problem of the single unit and the subsystem, cover various normal and fault flight modes, and reduce manpower resource consumption.

Owner:BEIJING SPACE TECH RES & TEST CENT

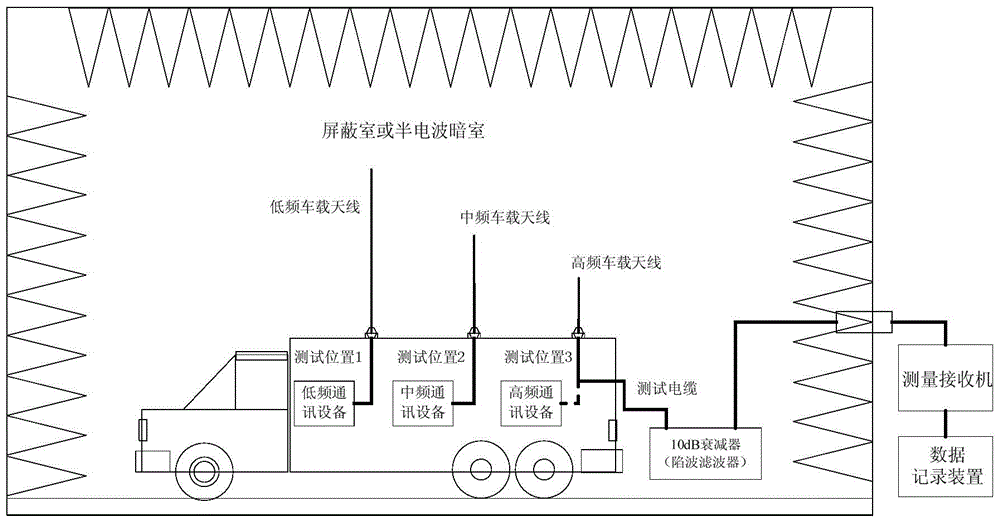

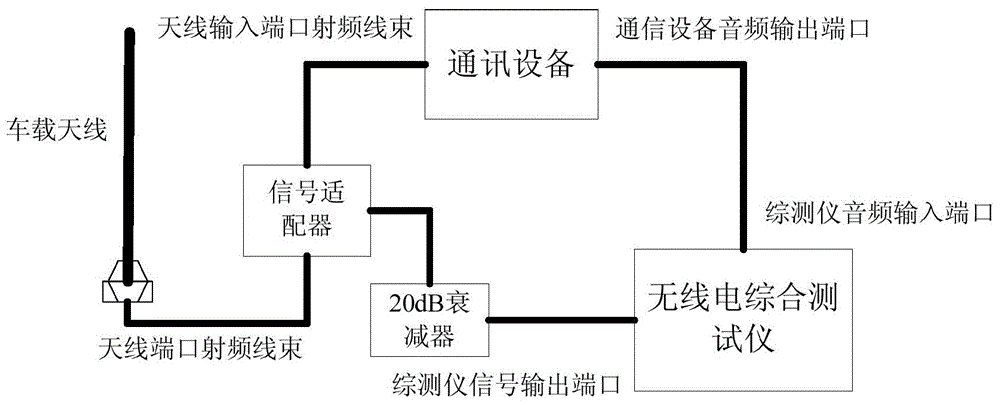

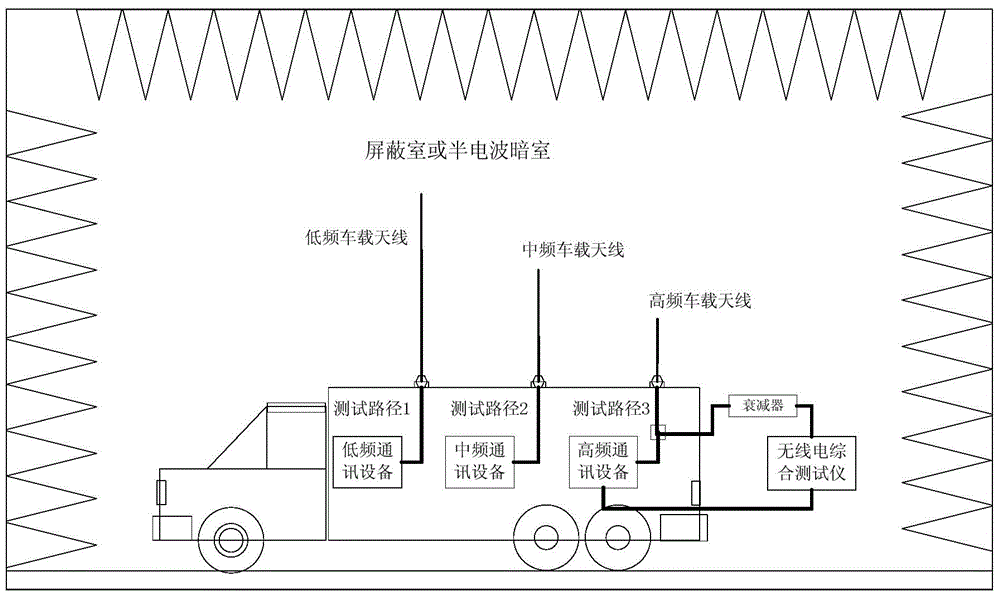

Multi-machine mutual-interference test method for vehicle-mounted communication systems in the same car

ActiveCN104601258AMake up for operabilityMake up for shortcomings in executionTransmitters monitoringMulti machineCommunications system

The invention belongs to the field of system-level electromagnetic compatibility test and relates to a multi-machine mutual-interference test method for vehicle-mounted communication systems in the same car. The multi-machine mutual-interference test method for the vehicle-mounted communication systems in the same car builds the multi-machine mutual-interference test method for the same car to carry out multi-machine mutual-interference test for the same car on several communication systems with different communication frequency bands to inspect the interference situations of bottom noise, adjacent channel, co-frequency, harmonic wave and the like interference of a communication device in a power emitting state to the other communication systems in receiving states. The test method makes up the disadvantages that a system communication system compatibility test method does not have pertinence and is not good for operation and execution. The test method is correct in theory, quick and convenient to finish test, intuitive in result, capable of quantifying the signal decreasing situation of the communication system under the multi-machine mutual-interference state in the same car, and suitable for testing the compatibility between different types of vehicle communication systems.

Owner:CHINA NORTH VEHICLE RES INST

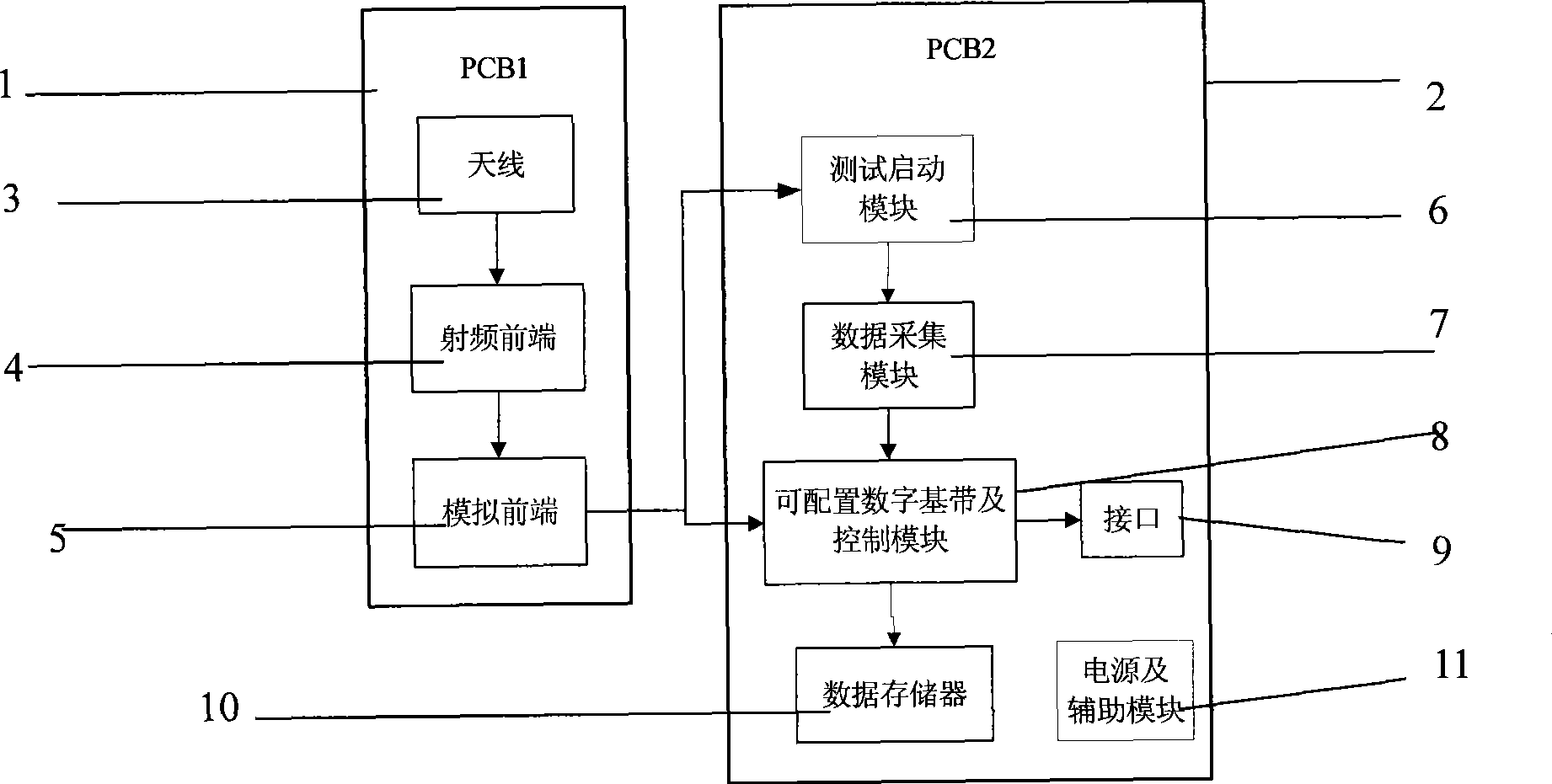

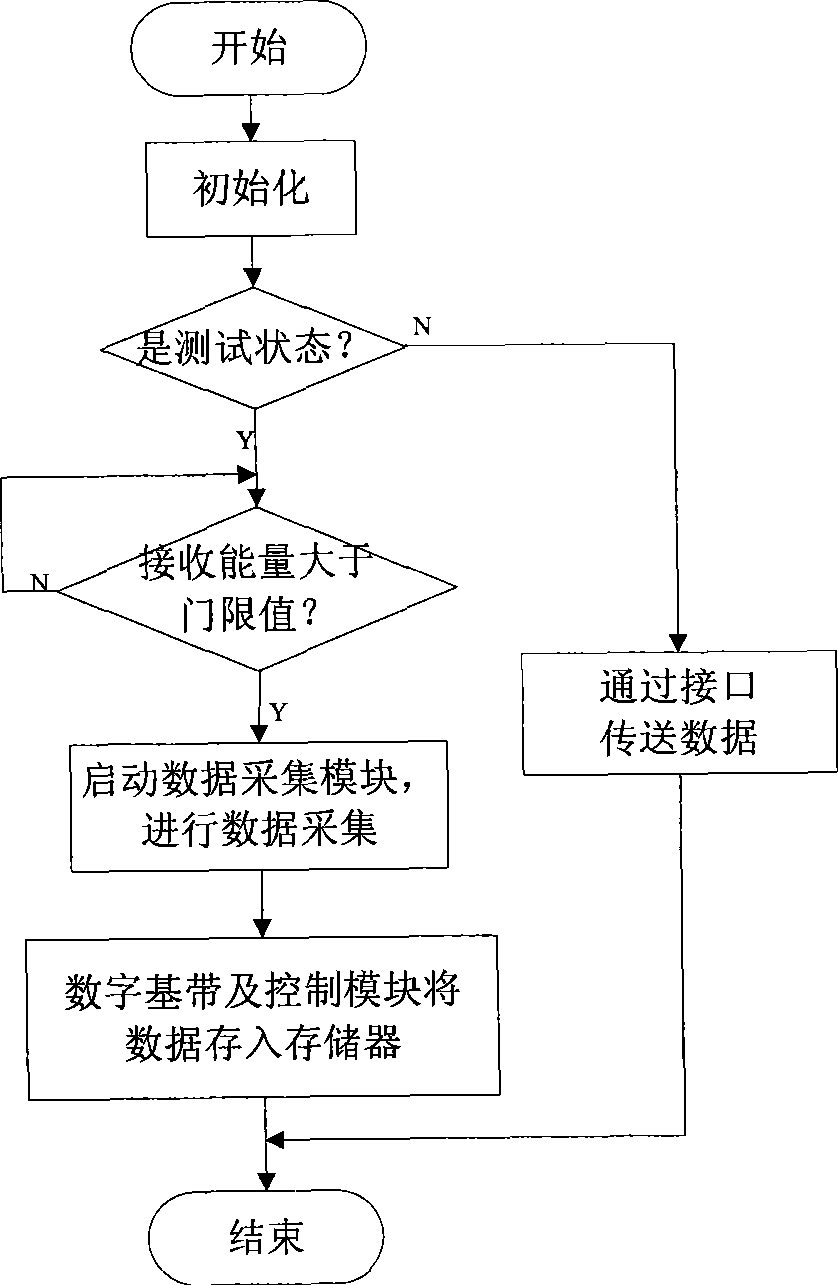

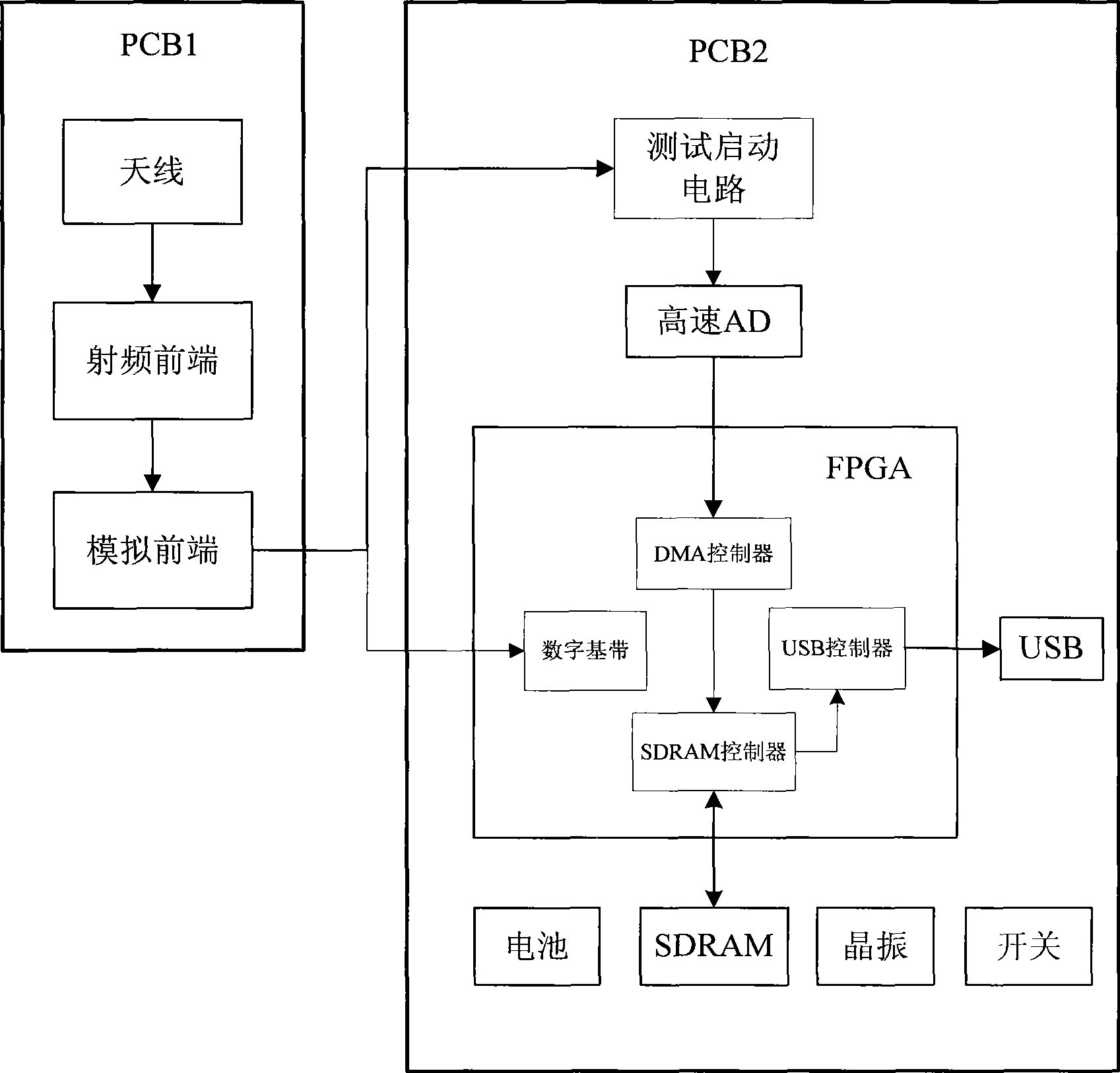

Electronic label test system and test method thereof

InactiveCN101363899AImprove the recognition rateLow costElectronic circuit testingSensing record carriersData memorySystem level testing

The invention specifically provides an electronic tag test system and a test method thereof, and belongs to the technical field of radio frequency recognition. The test system comprises an antenna, a radio frequency front end, an analog front end, a data collecting module, a configurable digital baseband and control module, a power supply, an auxiliary module, a data storage device and an interface thereof. The data collecting module collects the output data of the analog front end, the output data is transmitted to the digital baseband and control module, and temporarily stored in the data storage device, and the interface is connected to a PC after the testing process is completed. The interface controller of the digital baseband and control module controls the interface, and the data temporarily stored in the data storage device is transmitted to the terminal of the PC. The electronic tag test system and test method thereof can real-time record the electromagnetic characteristics of the electronic tag in application environment and variation condition thereof via a system level testing tag, perform theoretical analysis by guiding into a computer via a standard interface, search the reason that the electronic tag is not recognized, provide basis for selecting appropriate optimistic method, and improve the recognition rate of an RFID system.

Owner:FUDAN UNIV

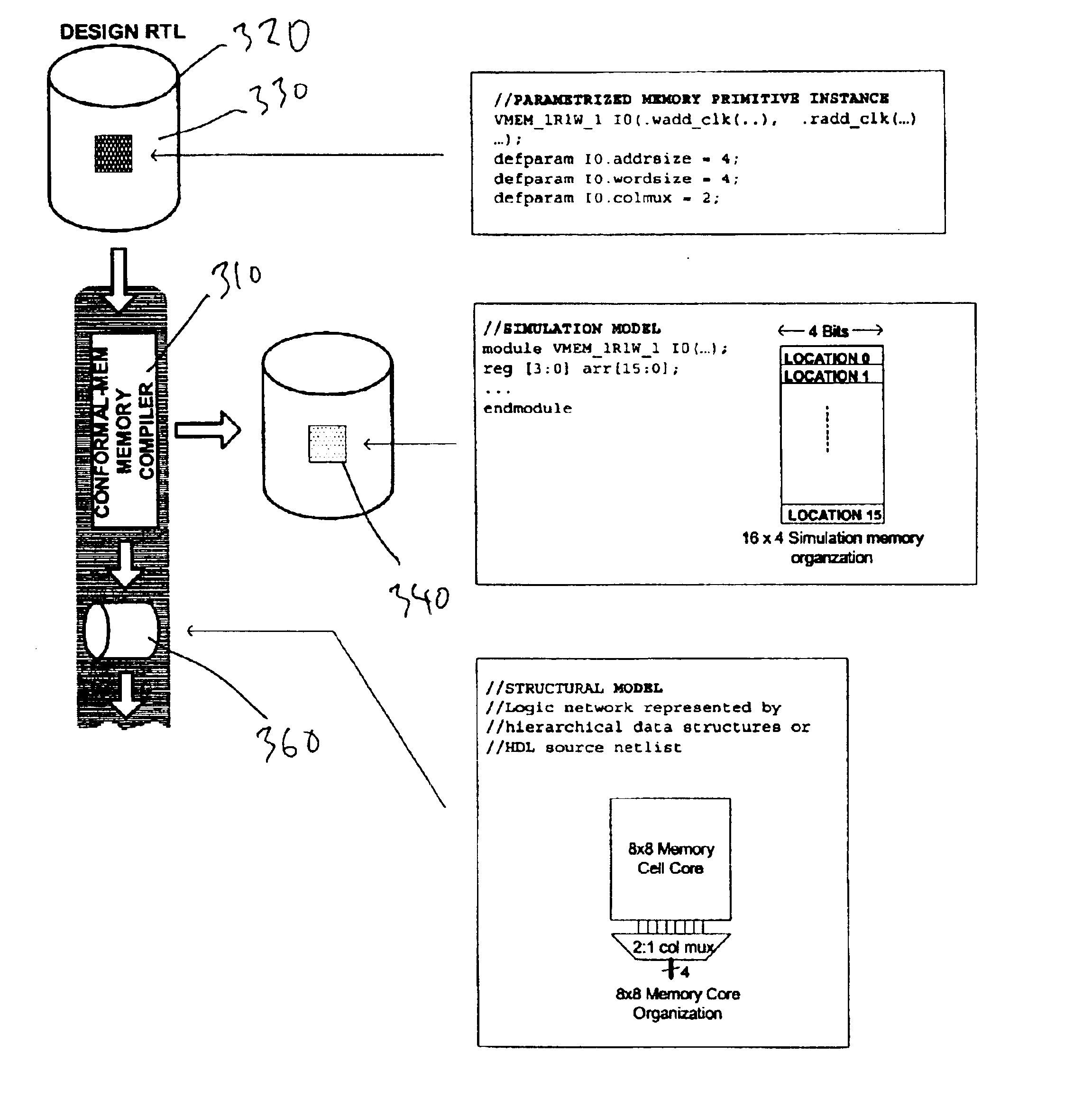

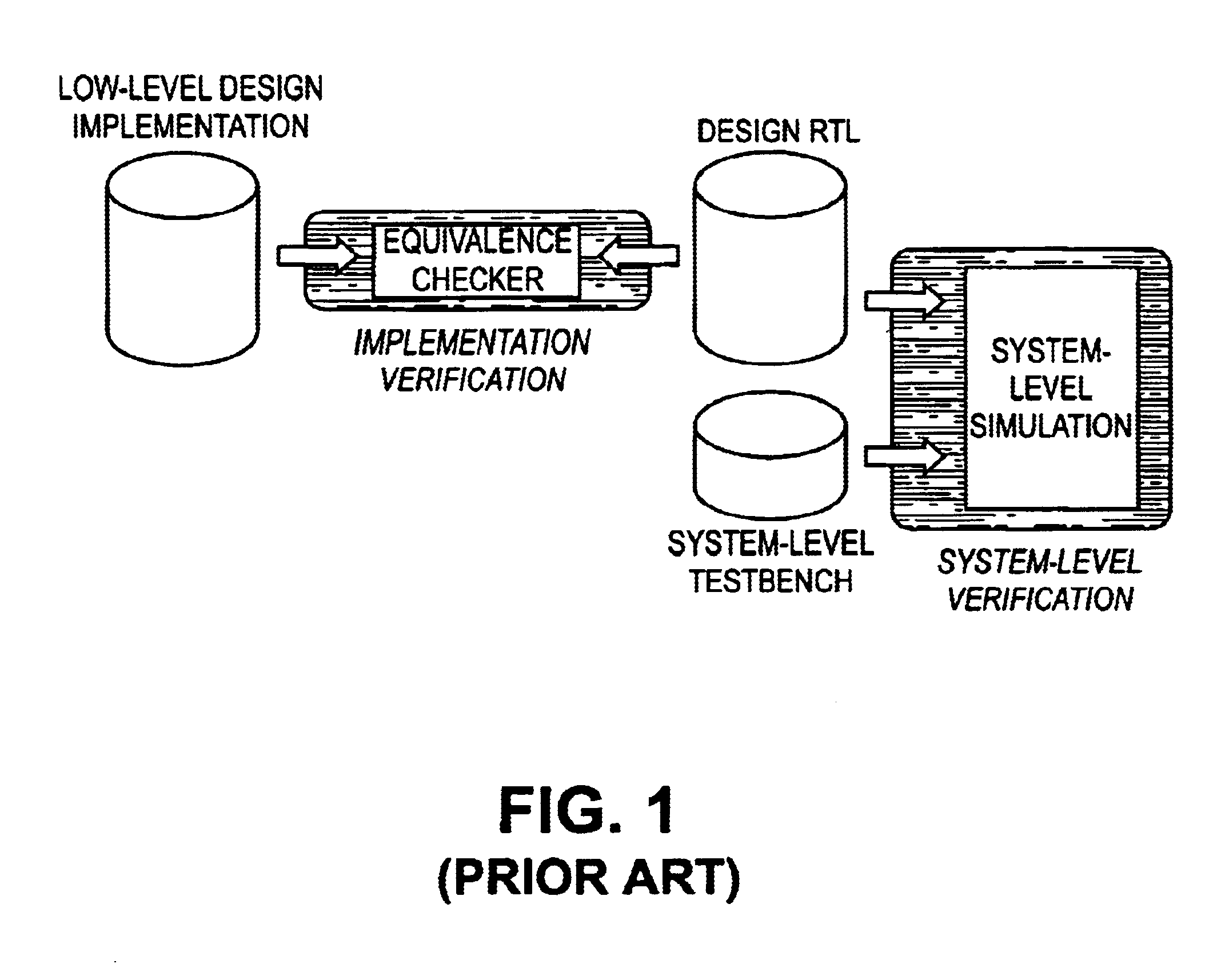

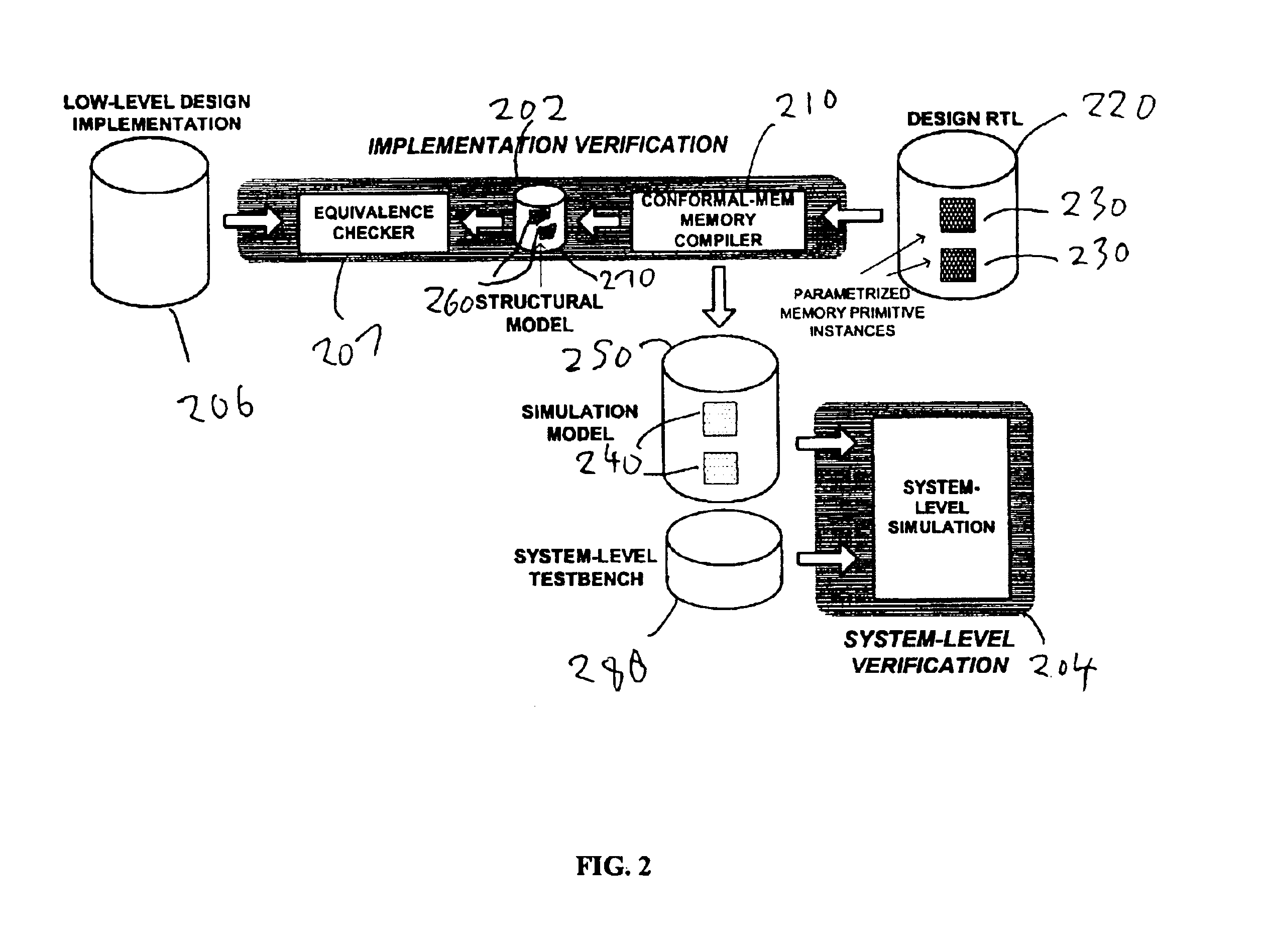

Method and apparatus for verification of memories at multiple abstraction levels

InactiveUS6848084B1Efficient verificationSimulated more efficientlyCAD circuit designSoftware simulation/interpretation/emulationComputer architectureProcessor register

This invention relates to method and apparatus for verification of circuit designs containing memories. At a register transfer abstraction level, verification of a circuit design requires showing that the register transfer language (RTL) abstraction of the design is logically equivalent to the design implementation represented at the logic (e.g., gate and / or flip-flop) and / or the transistor (e.g. implementation verification) abstraction levels, as well as logic simulation of the design RTL embedded in a system-level test bench for verification at the system-abstraction level.

Owner:CADENCE DESIGN SYST INC

System level testing for substation automation systems

ActiveCN101842713AEmergency protective circuit arrangementsCircuit interrupters testingTime informationElectricity

The present invention proposes that protection, measurement and control IEDs in a substation compute, according to interlocking rules or physical principles as well as a knowledge of the dynamic topology of the substation, for every switch they control if that switch may be operated safely, in contrast to a conventional and separate programming of the interlocking logic for each IED. To this purpose, the IEDs have access to the substation electrical topology, to the real-time information generated by other IEDs, and to the rules for interlocking. The invention takes advantage of a standardized Substation Configuration Description (SCD) of the substation for which the SA system is intended, as well as of a standardized description of the implemented device functions or capabilities of an individual IED. In particular, the substation topology is available from the substation configuration description (SCD file in IEC 61850 format), the real time information about the position of switches and line voltage / current can be read over the IEC 61850 protocol and the rules are available in script form. This concept applies both to simulated and real devices, and greatly increases system testing possibilities by supporting an efficient configuration of a simulation.

Owner:HITACHI ENERGY LTD

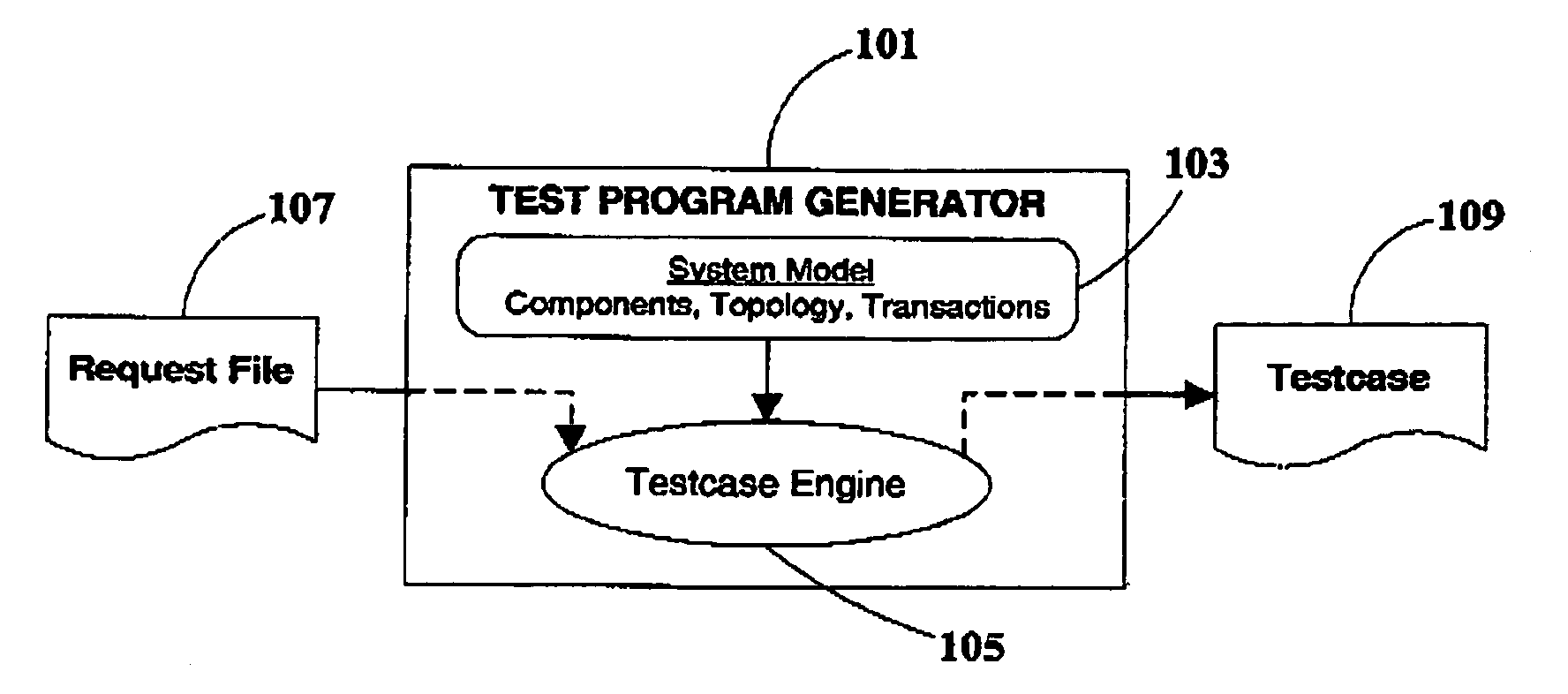

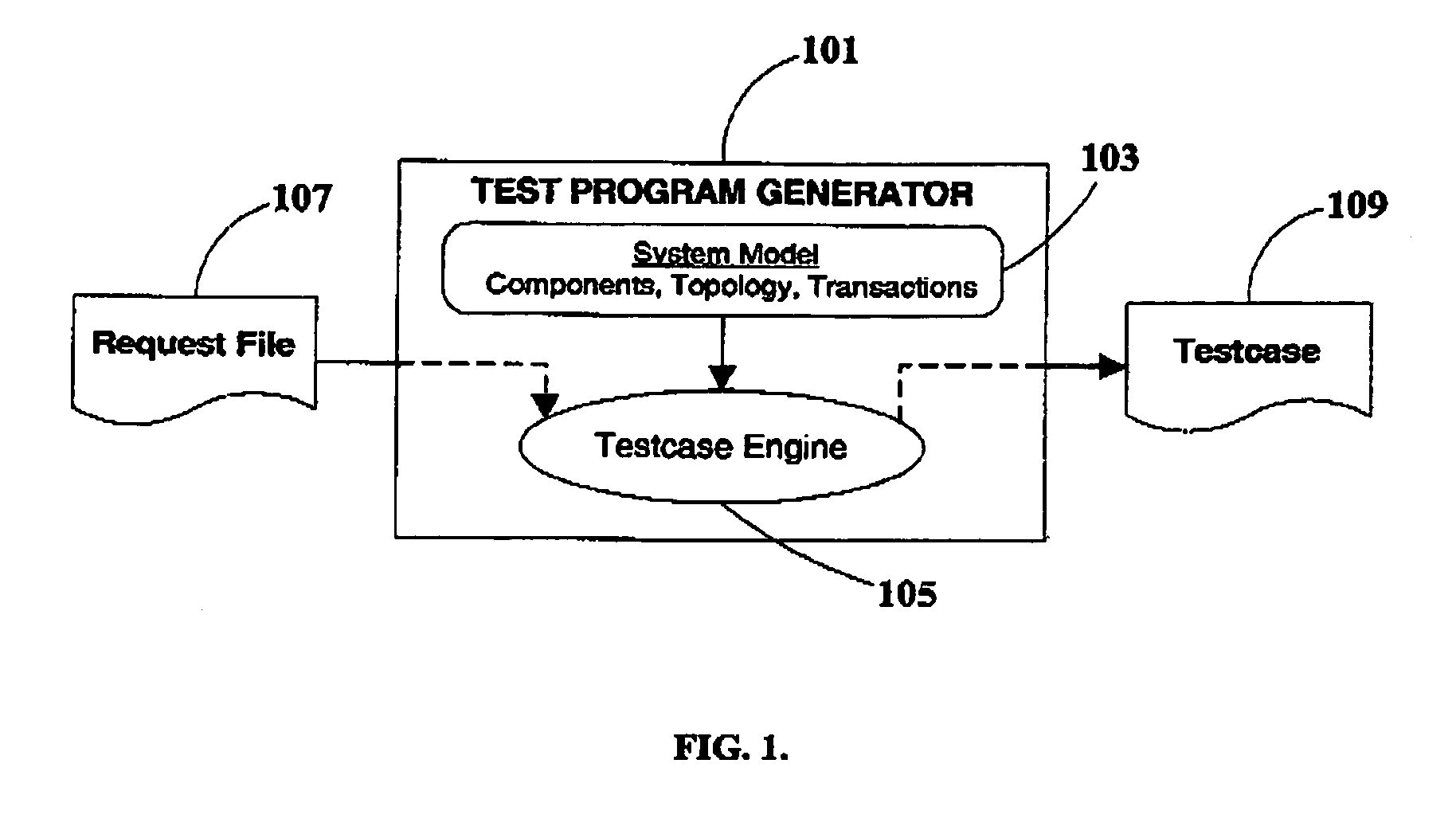

Scheduling of transactions in system-level test program generation

ActiveUS7007207B2More randomnessElectronic circuit testingError detection/correctionTheoretical computer scienceSystem level testing

A test-program generator capable of implementing a methodology, based on a formal language, for scheduling system-level transactions in generated test programs. A system to be tested may be composed of multiple processors, busses, bus-bridges, shared memories, etc. The scheduling methodology is based on an exploration of scheduling abilities in a hardware system and features a Hierarchical Scheduling Language for specifying transactions and their ordering. Through a grouping hierarchy, which may also be expressed in the form of an equivalent tree, the Hierarchical Scheduling Language combines the ability to stress related logical areas of the system with the possibility of applying high-level scheduling requests. A method for generating testcases based on request-files written in the Hierarchical Scheduling Language is also presented.

Owner:TWITTER INC

System level testing for substation automation systems

ActiveUS8265908B2Resistance/reactance/impedenceEmergency protective circuit arrangementsTime informationSystem testing

Owner:HITACHI ENERGY LTD

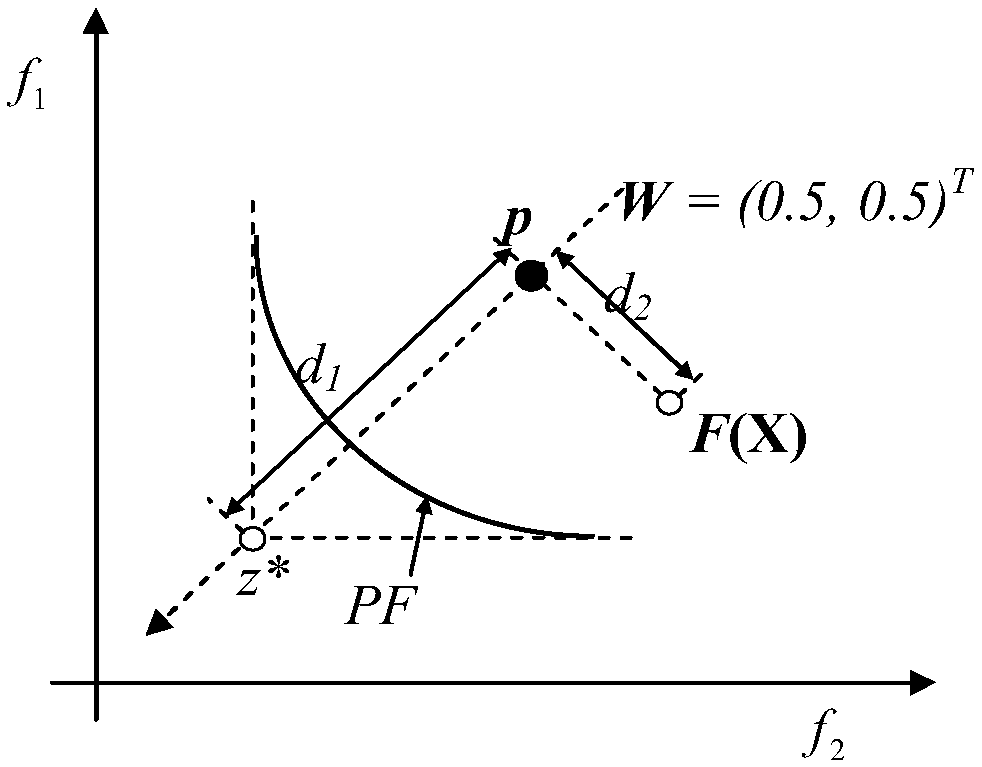

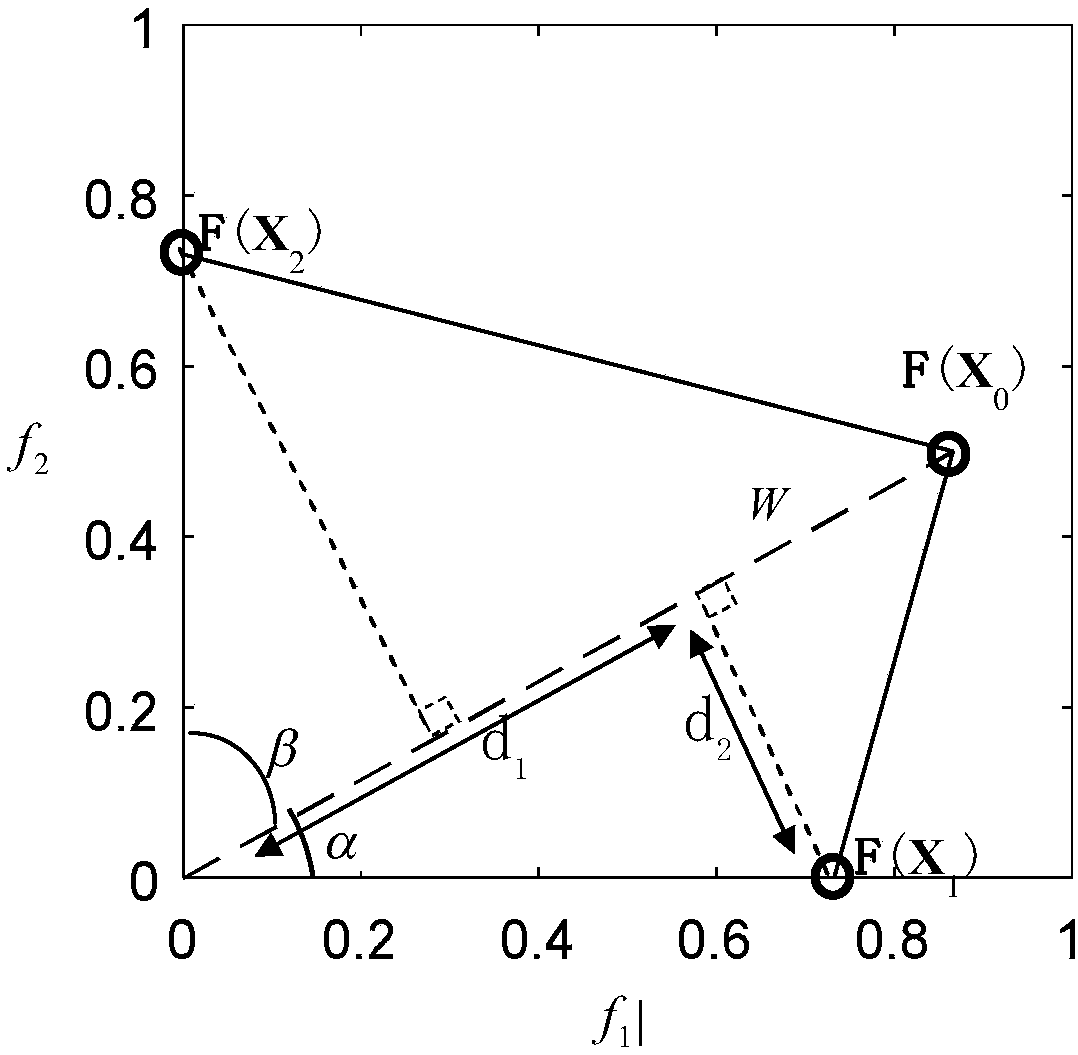

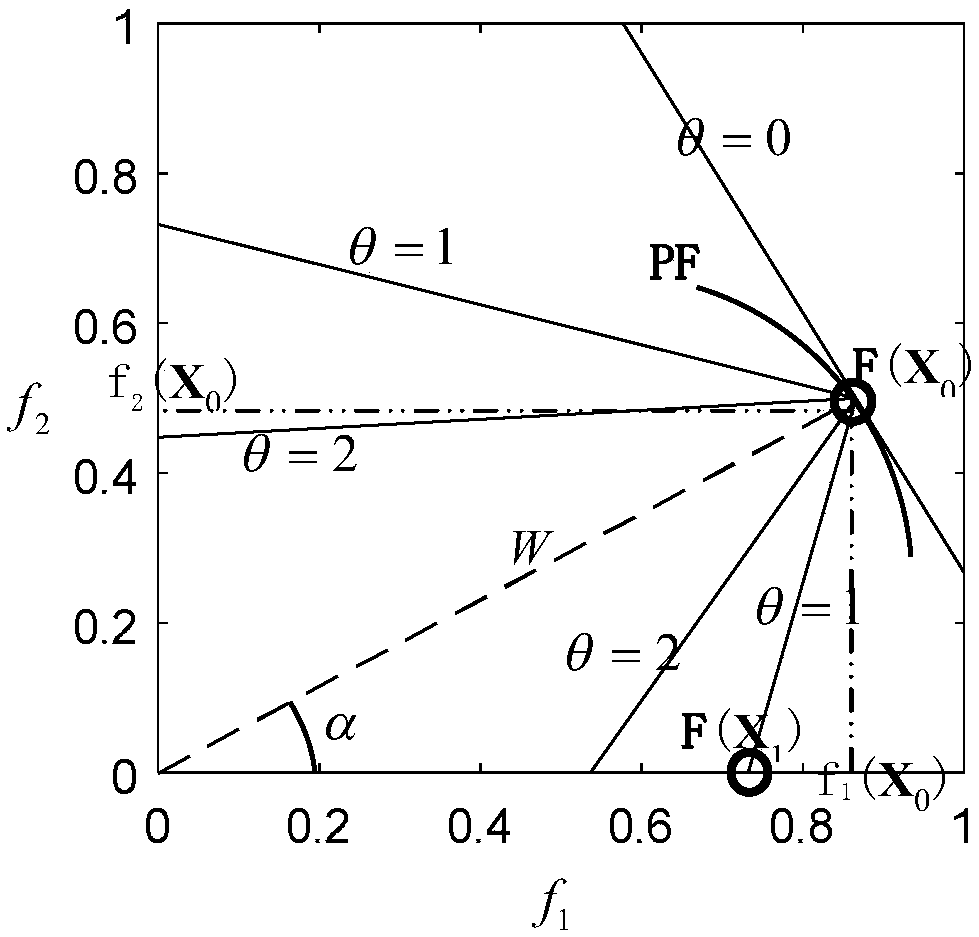

A PBI-based system-level testability design optimization method

The invention discloses a system-level testability design optimization method based on PBI. The method includes: firstly, setting a weight vector based on a PBI method; calculating the lower limit ofthe penalty factor corresponding to each weight vector; and then iteratively searching an optimal influence factor vector based on a genetic algorithm, carrying out optimization by combining an objective function value and a PBI function value in a searching process to obtain a new population, and deleting a dominated solution in a final generation population to obtain a Pareto optimal solution set of the influence factor vector. With the adoption of the method, the convergence speed of the algorithm can be increased while the optimal solution is ensured to be obtained.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

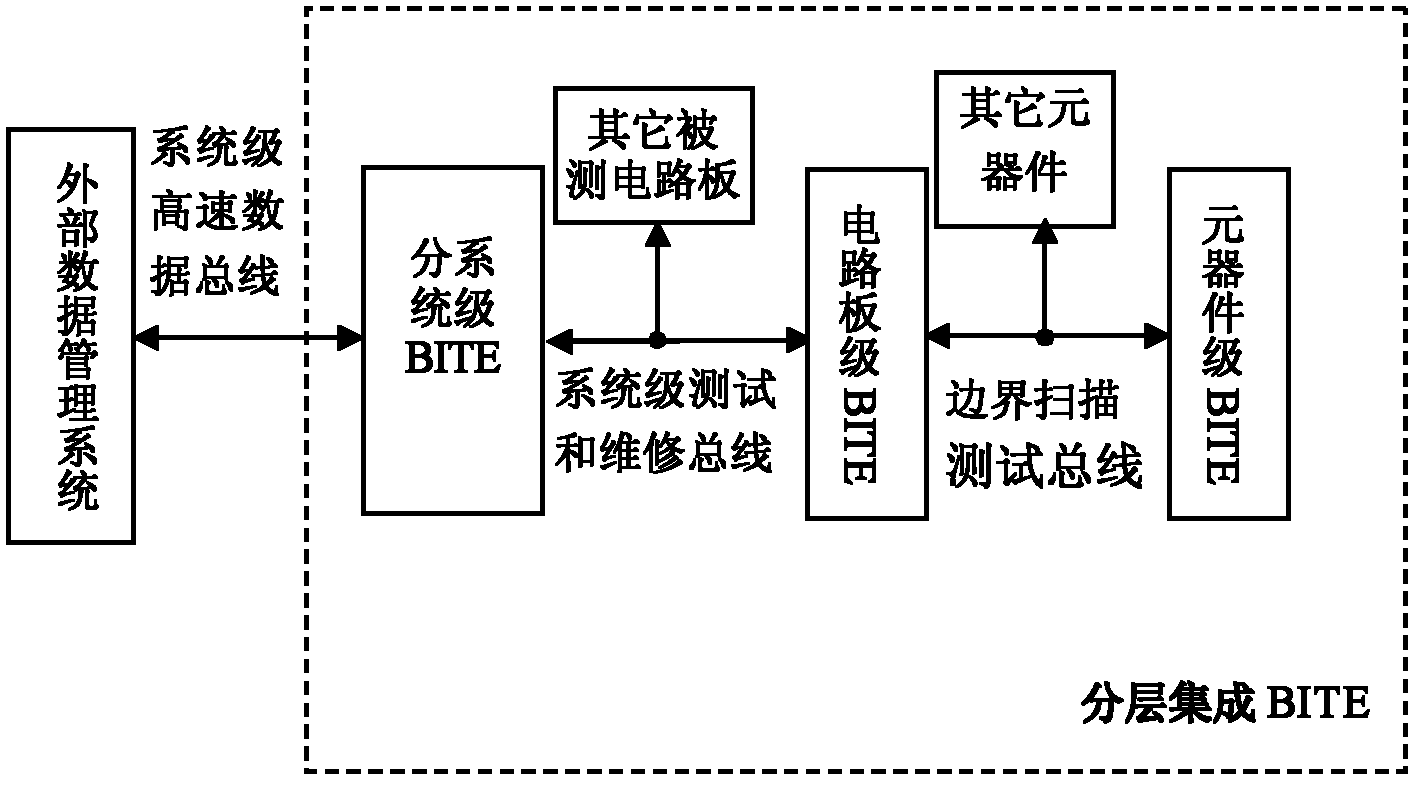

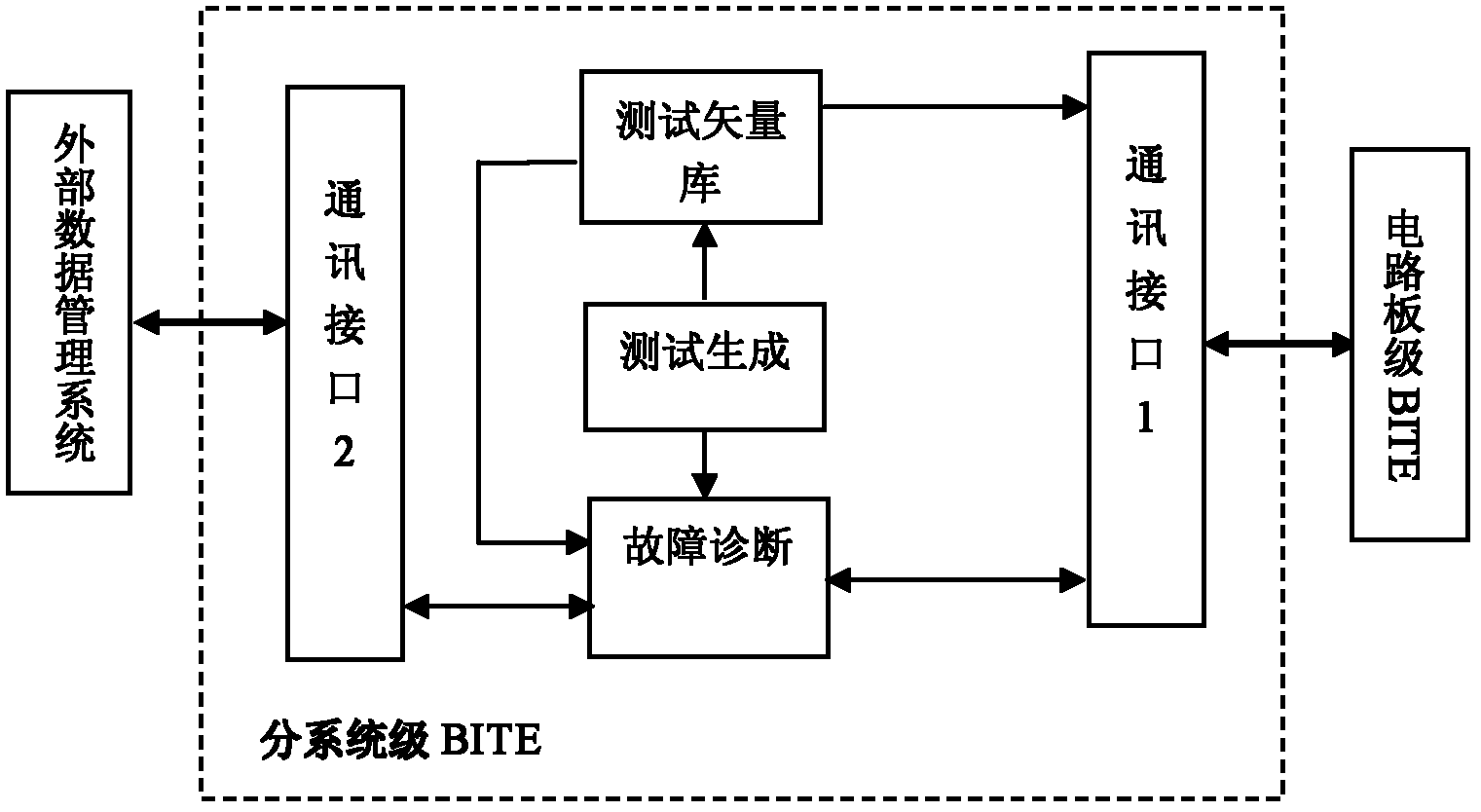

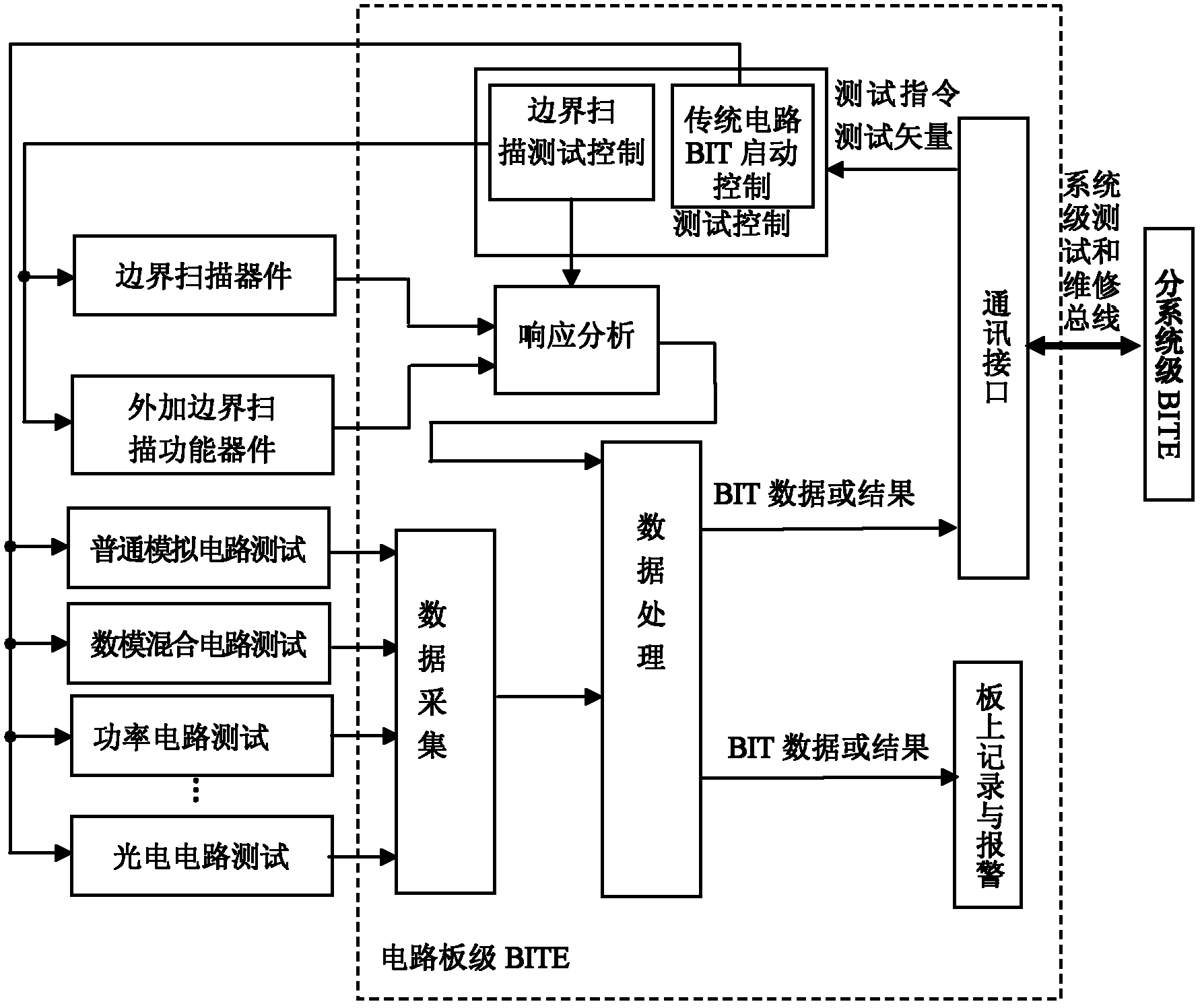

Circuitry built-in test device based on boundary scanning mechanism

InactiveCN102590733AFacilitate test reuseImprove test resultsElectronic circuit testingExternal dataSystem level testing

The invention discloses a circuitry built-in test device based on a boundary scanning mechanism, which includes a subsystem-level BITE, a circuit board-level BITE and a component-level BITE, wherein the subsystem-level BITE is mutually connected with an external data management system through a system-level high-speed data bus, and is mutually connected with the circuit board-level BITE and other to-be-tested circuit boards in other subsystems through a system test and maintenance bus in the lower level; and the circuit board-level BITE is mutually connected with the component-level BITE and other components in the circuit board through a boundary scanning test bus. The device can realize different-level fault layered diagnosis and positioning of the complicated circuitries of aero spacecrafts as satellites, and provides reference for design of the circuitry built-in test devices of other aerospace products.

Owner:NAT UNIV OF DEFENSE TECH

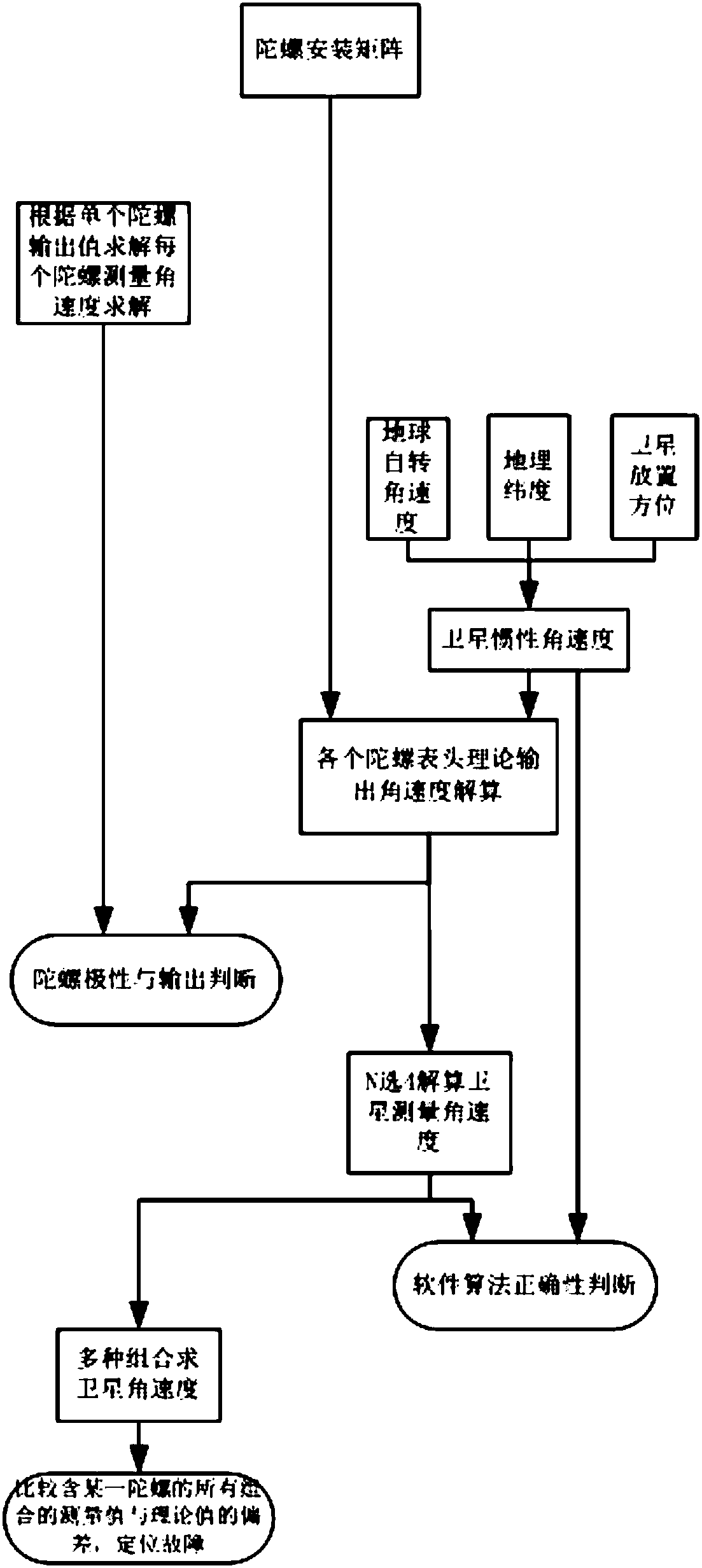

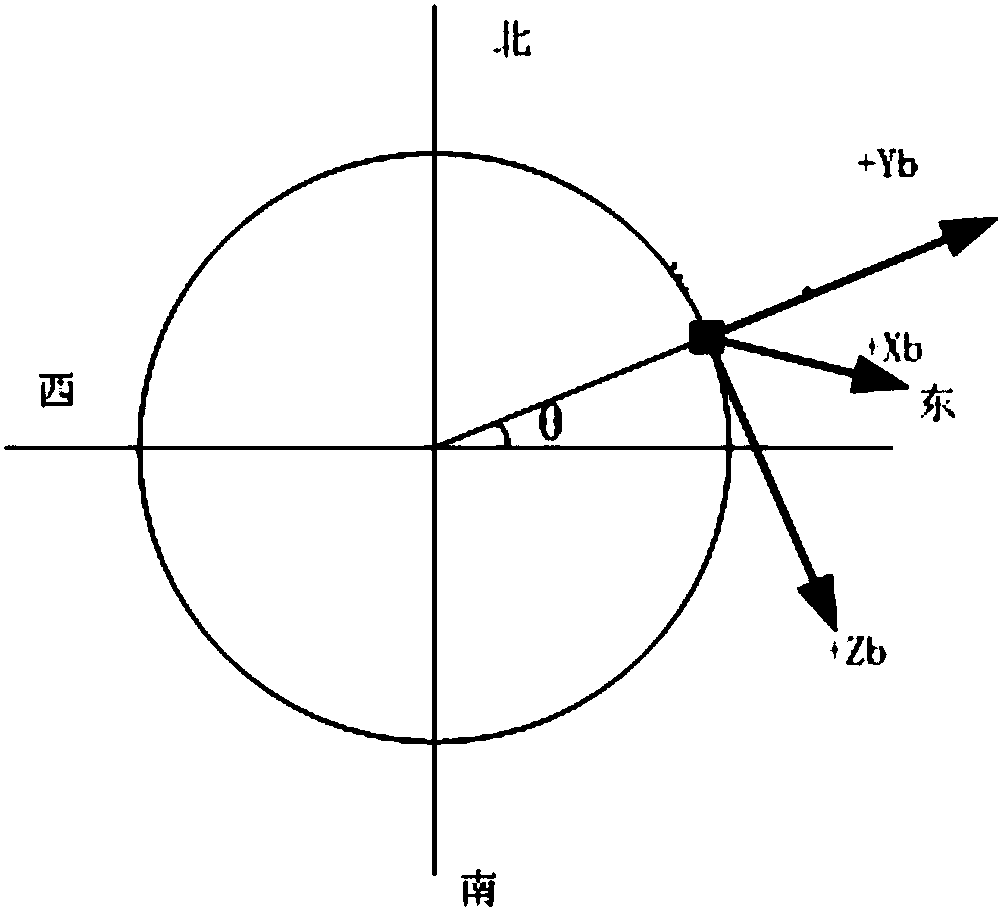

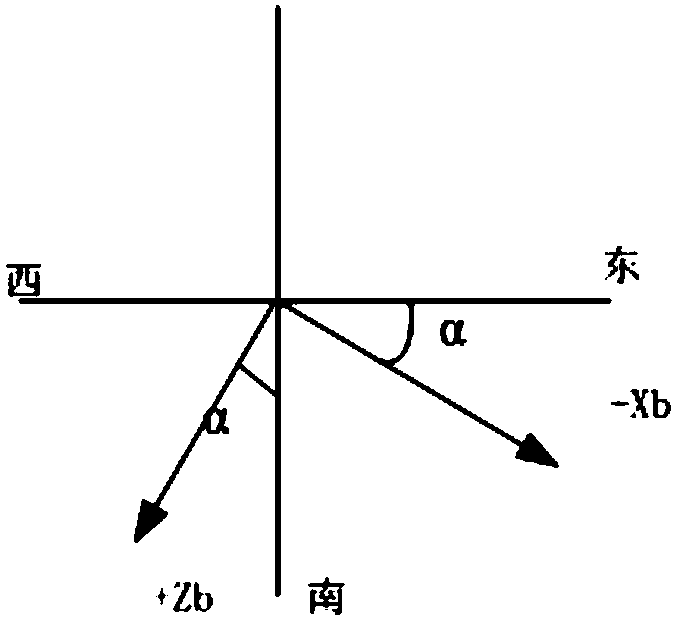

Top polarity testing and output value fault detection method

ActiveCN107817004AEasy fault detectionConvenient and accurate fault detectionMeasurement devicesEarth's rotationAngular velocity

The invention discloses a top polarity testing and output value fault detection method. The method comprises the following steps: firstly, describing a top mounting matrix; secondly, solving top measurement angular velocity; thirdly, resolving satellite inertial angle speed and top output theoretical value by utilizing rotational angular velocity of the earth; fourthly, solving satellite inertialmeasurement angular velocity; and fifthly, locating a top in a fault state by utilizing multiple combinations of top headers. The method disclosed by the invention has the advantages that top polarityand output value can be conveniently and accurately tested, mutual fault monitoring among tops can be realized, a top whole satellite state testing process can be simplified, requirement on test equipment is lowered, workload is reduced, and the method disclosed by the invention not only can be applied to a top whole satellite testing process but also can be applied to a one machine level and system level testing process.

Owner:SHANGHAI SATELLITE ENG INST

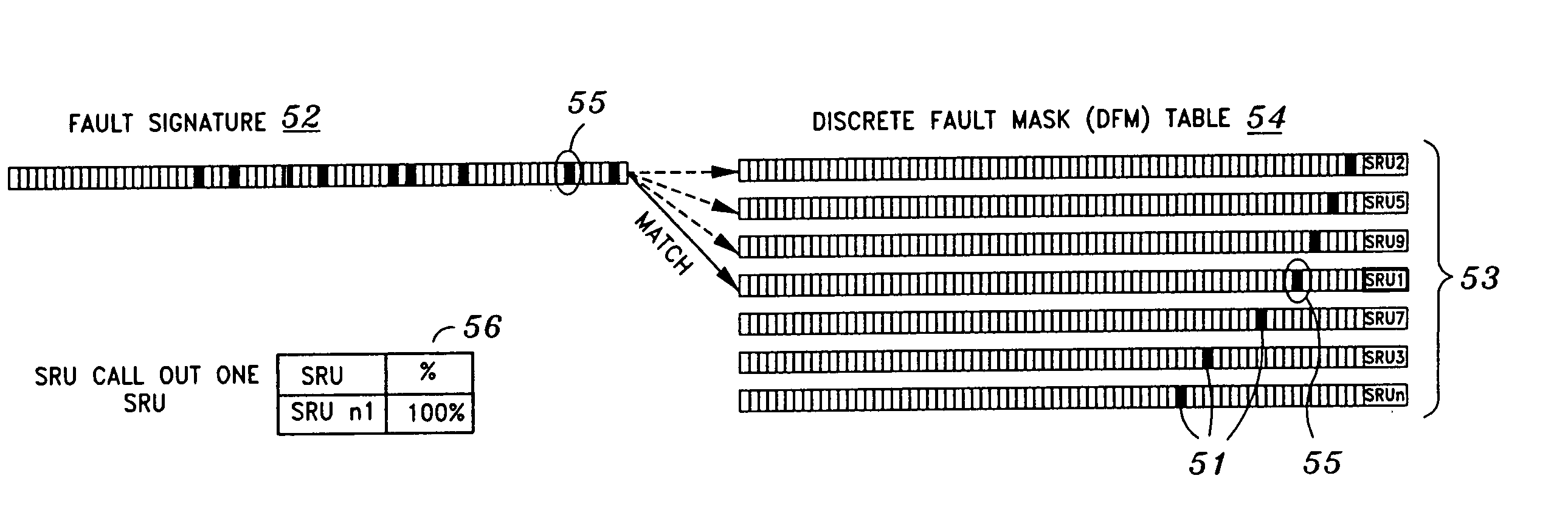

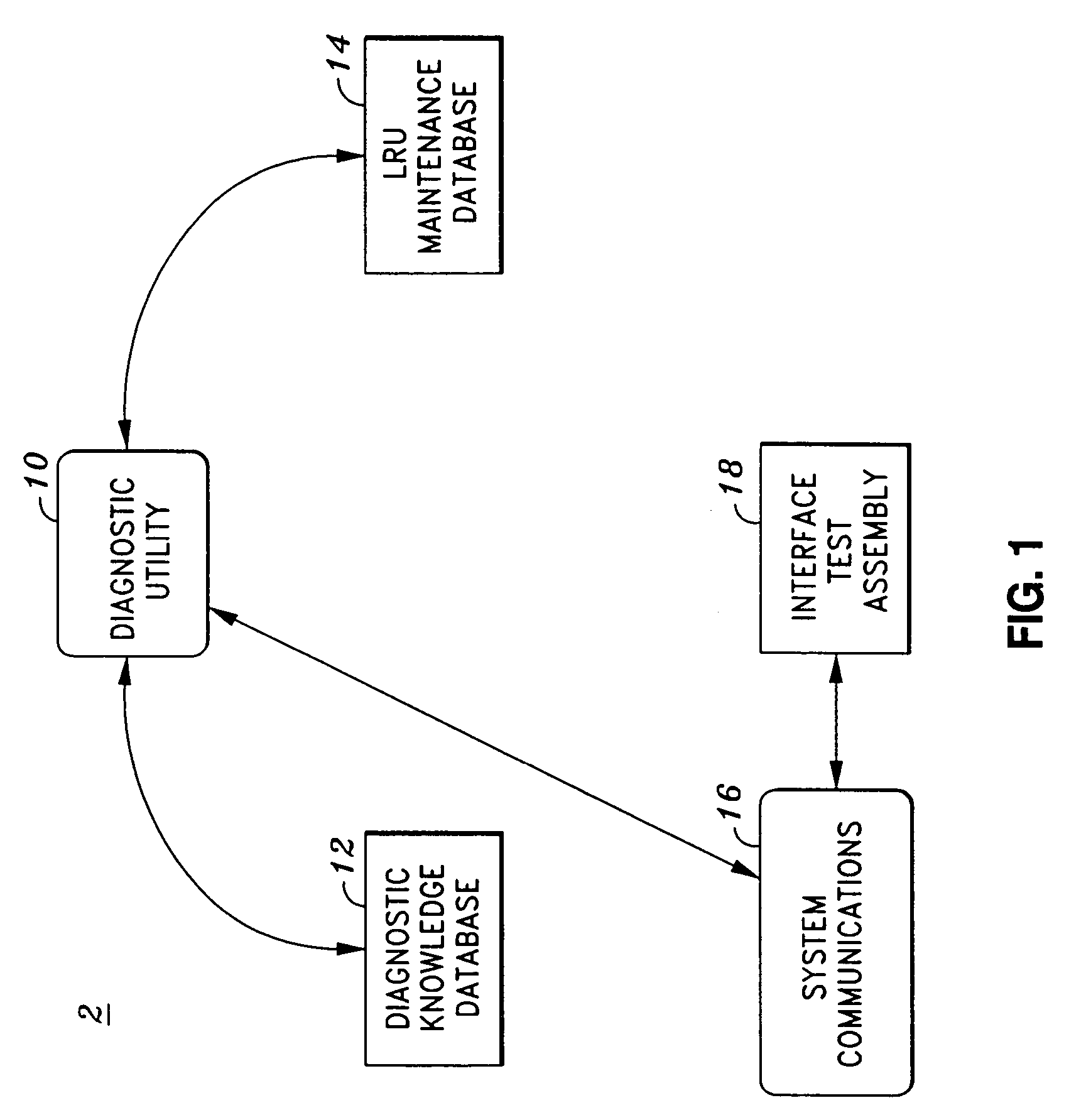

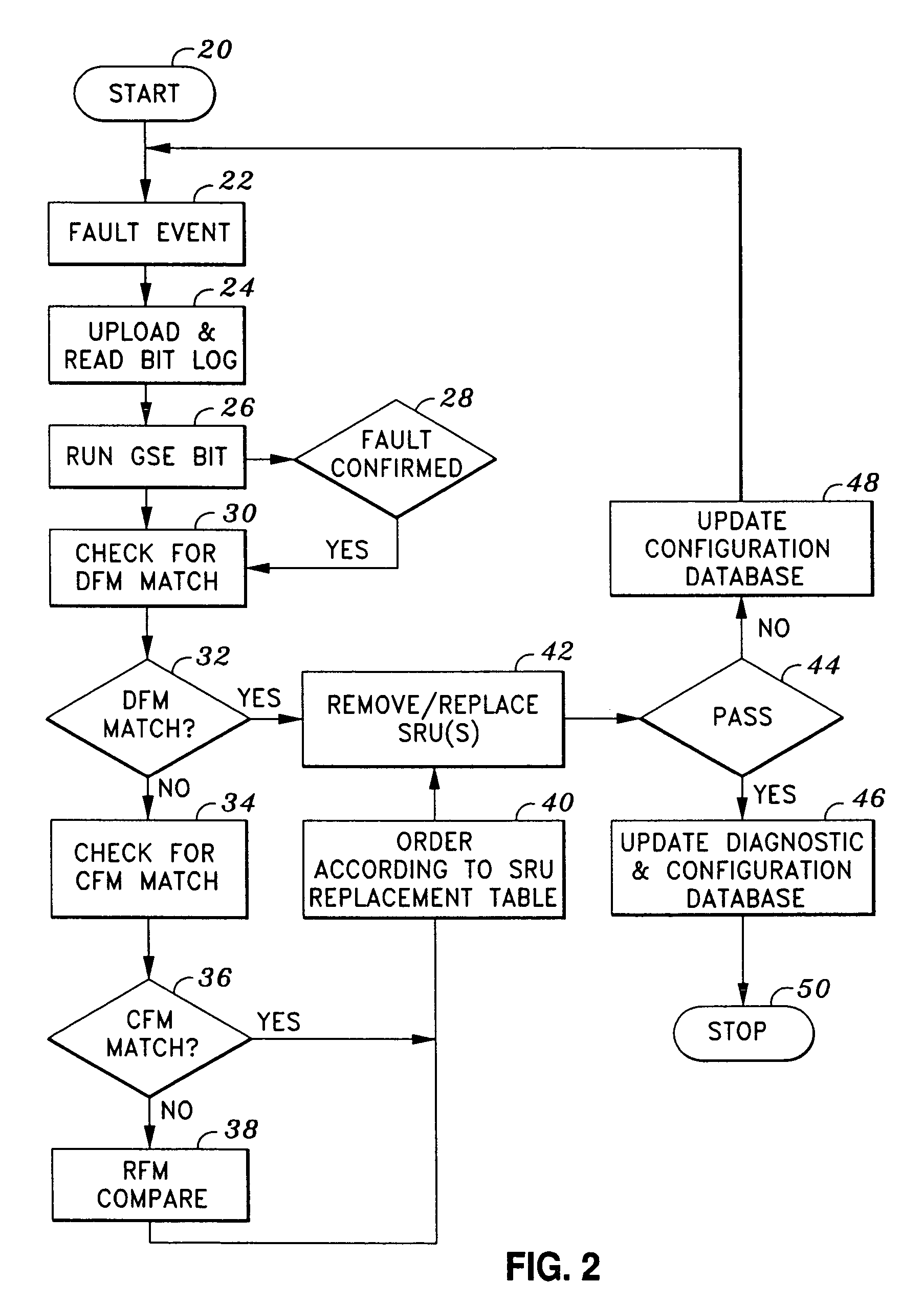

Built-in-test diagnostic and maintenance support system and process

ActiveUS7203879B2Lower potentialMany timesElectronic circuit testingSupporting systemSystem under test

A diagnostic and maintenance support system and process are provided for performing tests, collecting Built-In-Test (BIT) log data from systems, analyzing fault data, and recommending Shop Replaceable Units (SRU's). The system and process include uploading and reading a retrieved fault signature from a BIT log retrieved from a subject system under test. The retrieved fault signature is a serial word composed of a plurality of consecutive bits indicating either a pass or fail. Each bit is assigned to a specific SRU, system level test, or an event. The system and process further include a source code segment for performing a Discrete Fault Mask (DFM) algorithm, a Combinational Fault Mask (CFM) algorithm, and a source code segment for performing a Reserved Fault Mask (RFM) algorithm to identify a list of potentially problematic SRU's if matching bits are not found between the retrieved fault signature and the list of CFM serial words.

Owner:NORTHROP GRUMMAN SYST CORP

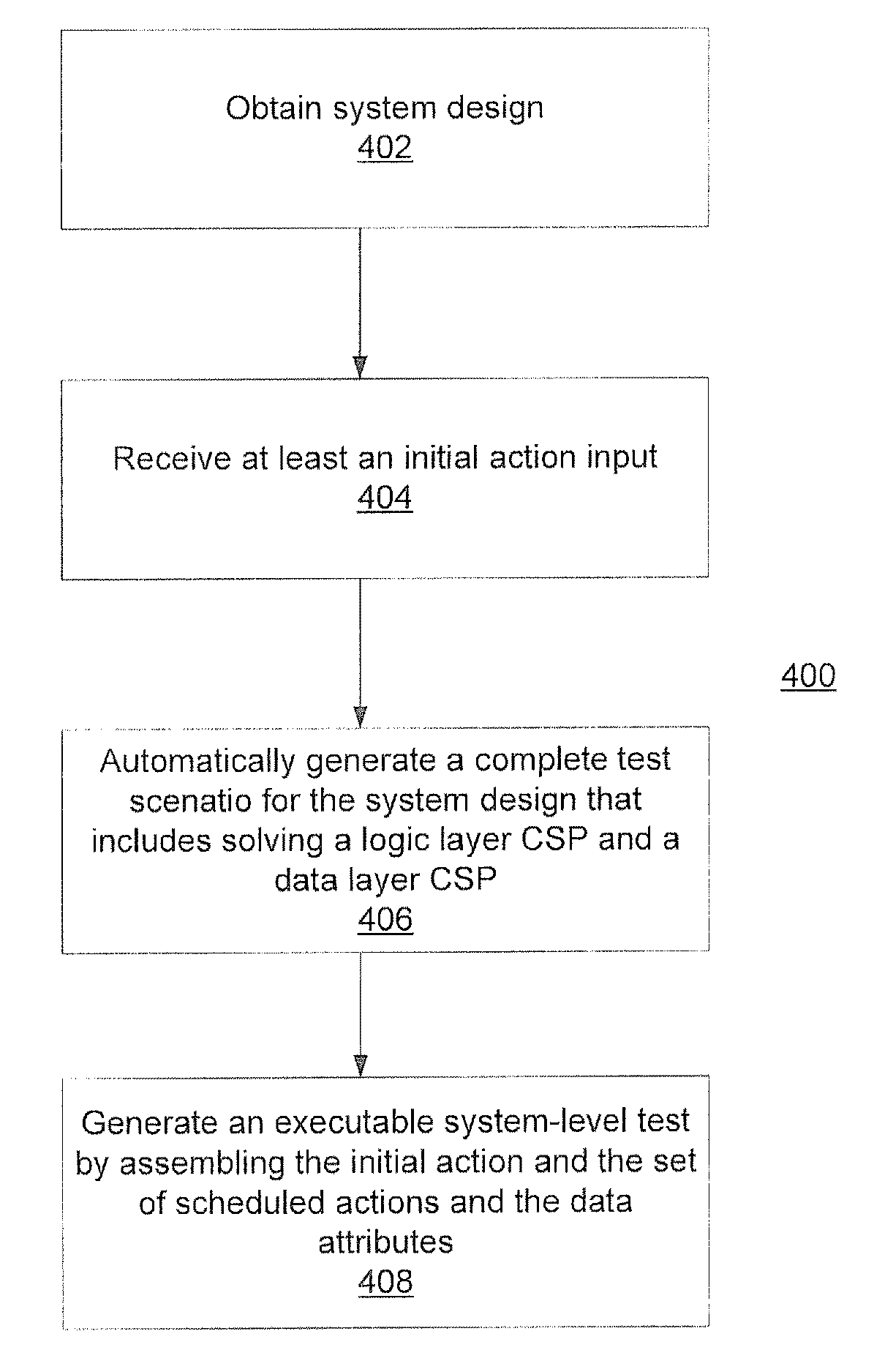

Method and system for automatically generating executable system-level tests

ActiveUS9582406B1Satisfy constraintsSoftware testing/debuggingSpecial data processing applicationsSystems designDatapath

Method and system for automatically generating executable system-level tests. The method includes obtaining a system design including interrelation between components of the system design, actions the components are operable to perform, and constraints relating to the performance of the actions; receiving at least an initial action input to be tested; automatically generating a complete test scenario including: solving a logic layer CSP, including automatically scheduling actions and data paths of the test scenario, and assigning values to logic attributes of the actions and data, satisfying constraints relating to the logic layer, and solving a data layer CSP, satisfying constraints relating to data attributes taking into account the constraints relating to the logic layer; and generating the executable system-level test by assembling the initial action and the set of scheduled actions and data paths and the data attributes.

Owner:CADENCE DESIGN SYST INC

SIP (system in package) chip testing platform and method

ActiveCN103969572ASimple structureEasy to operateElectronic circuit testingSimple modeCommunication control

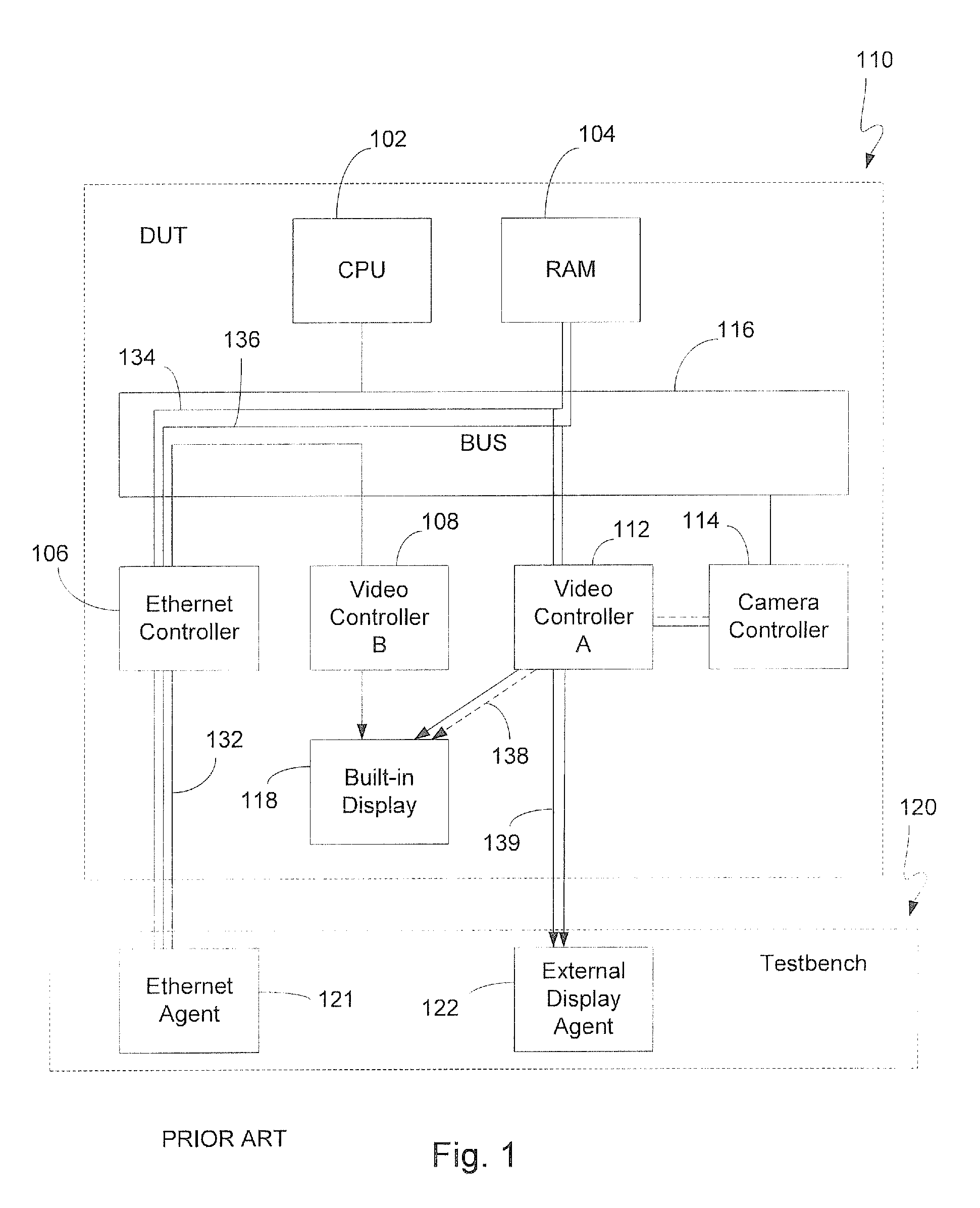

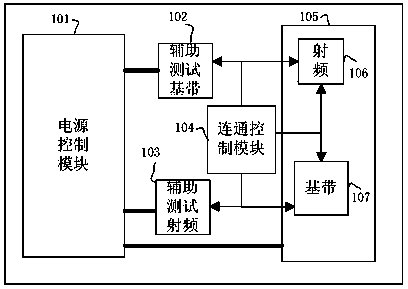

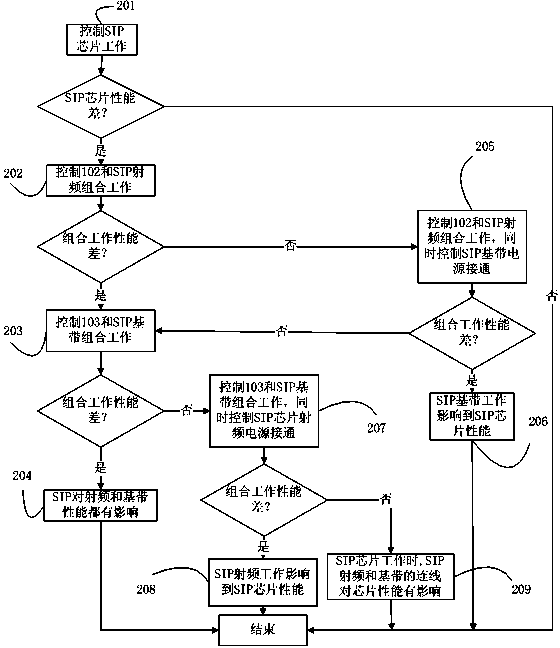

The invention aims to provide an SIP (system in package) chip testing platform which at least comprises a power control module, an auxiliary testing base band, an auxiliary test radio frequency, a to-be-tested SIP chip and a communication control module. The to-be-tested SIP chip at least comprises a radio frequency and a base band, the power control module supplies power to the auxiliary testing base band, the auxiliary test radio frequency and the to-be-tested SIP chip, and the communication control module controls communication among the radio frequency and the base band of the to-be-tested SIP chip, the auxiliary testing base band and the auxiliary test radio frequency. By the aid of the platform, test problems about system-level tests on performance of the chip and checking of reasons causing reduction of the performance of the chip are solved, chip-level tests complicated in operation and high in cost can be omitted, and specific reasons causing the problems inside the SIP chip are determined via a simple mode; furthermore, the testing platform has the advantages of simple structure, easiness in operation, low development cost, flexibility in operation and the like.

Owner:TECHTOTOP MICROELECTRONICS

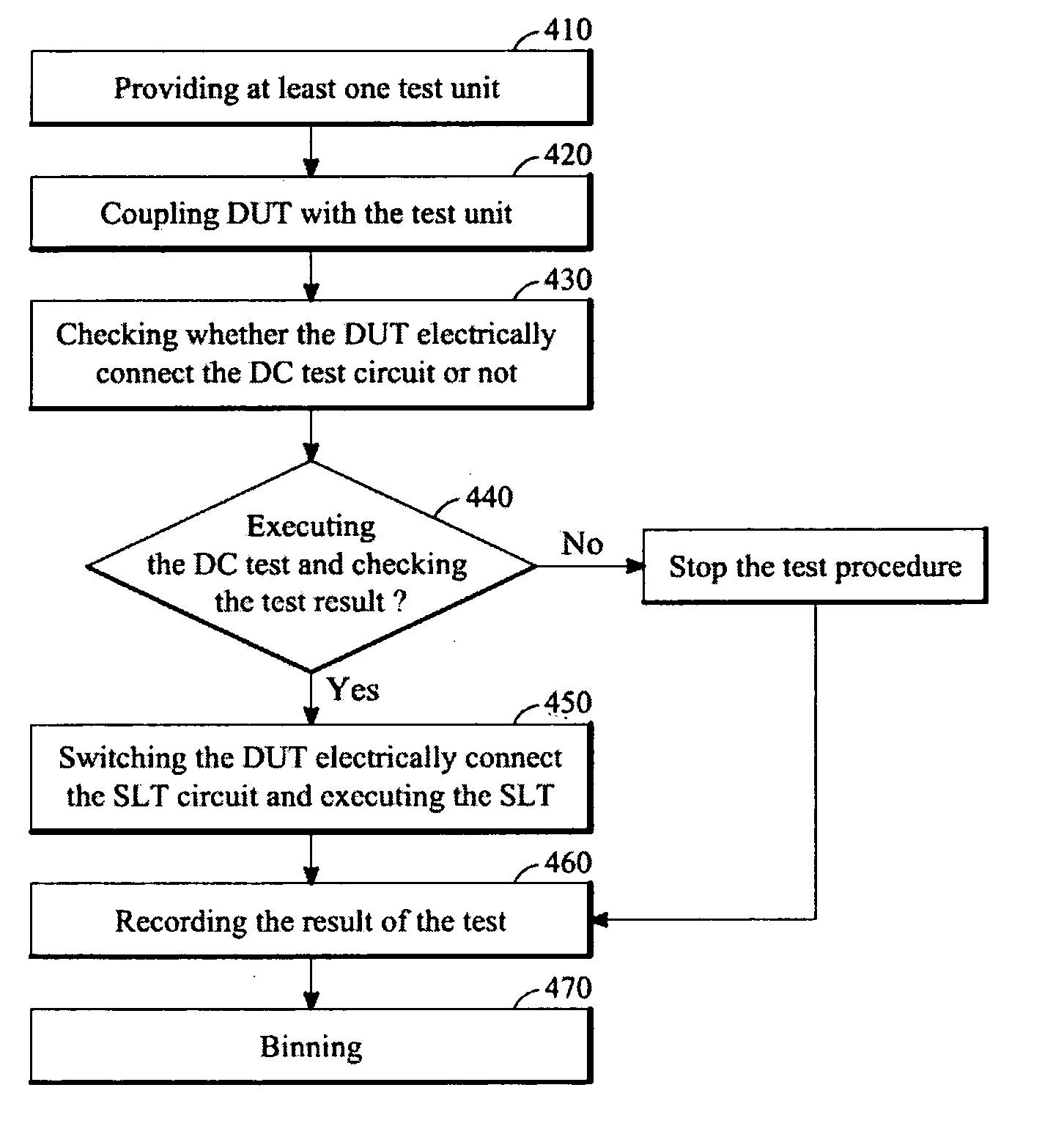

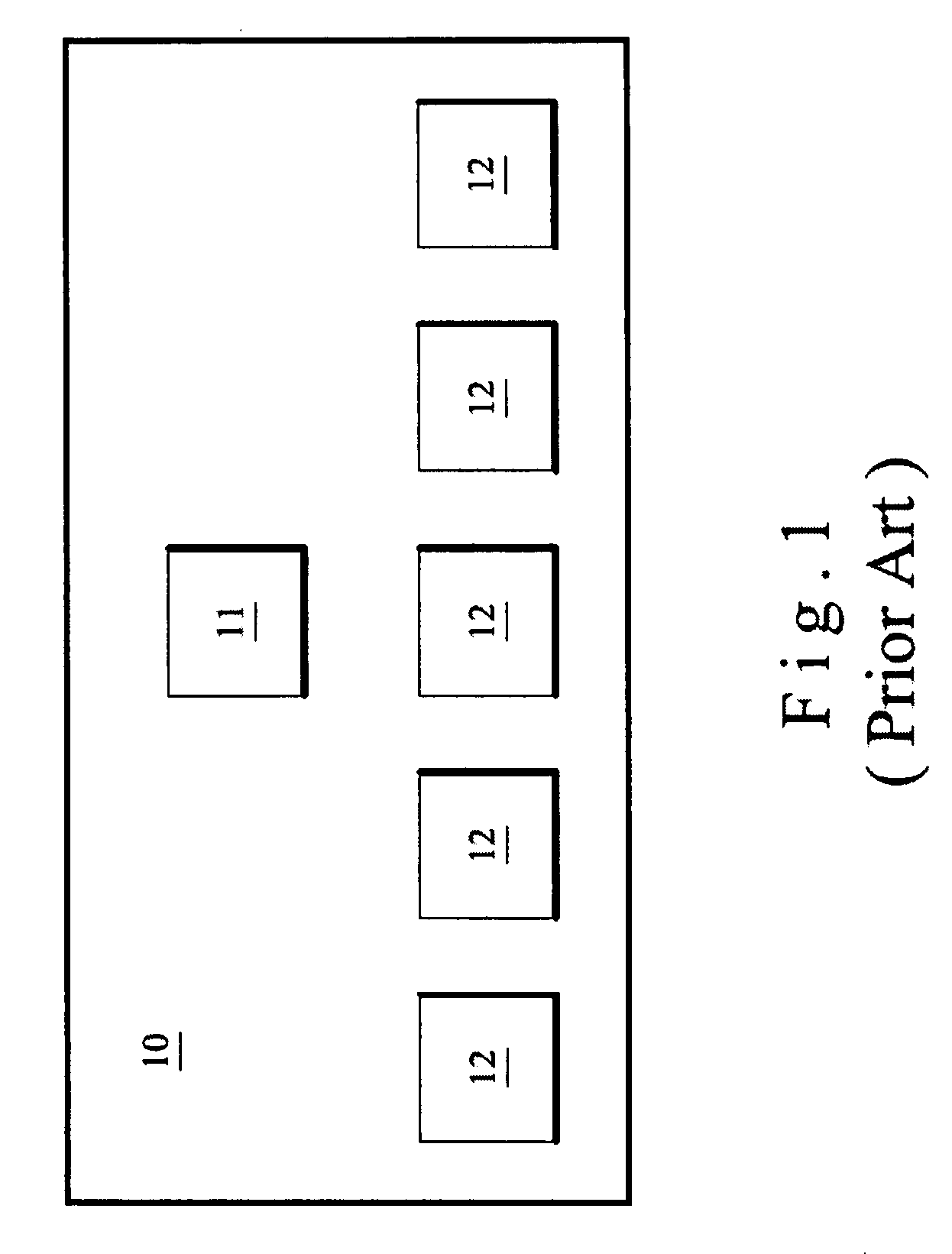

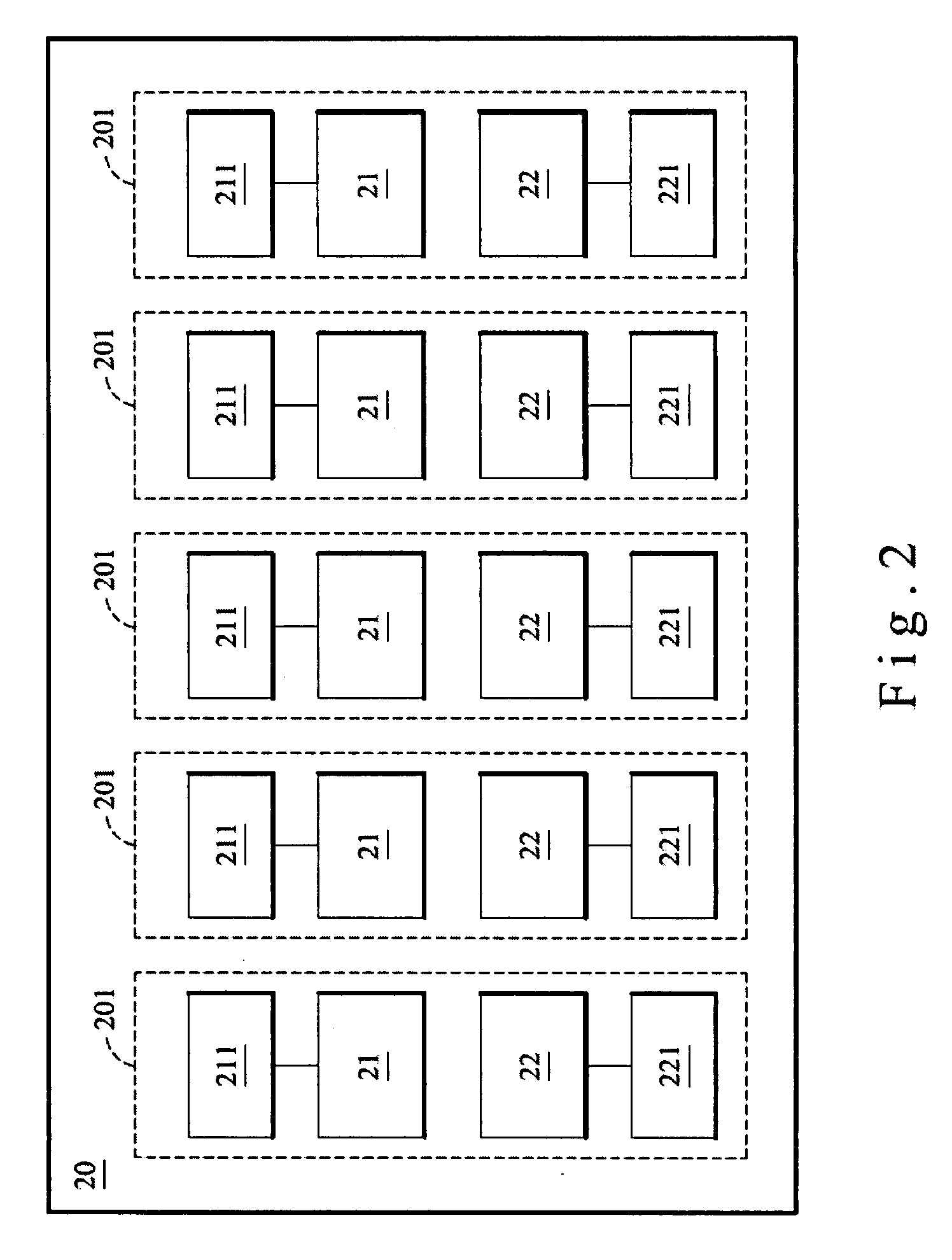

Structure of test area for a semiconductor tester

InactiveUS20080174331A1Measurement instrument housingAutomated test systemsEquipment under testTester device

Devices and methods for DC and SLT (system level test) integration are disclosed. The DC circuit and the SLT circuit are integrated into the same device. Therefore, the DUT (device under testing) can precede the SLT before the FT (final test) when the DUT passes the DC.

Owner:KING YUAN ELECTRONICS

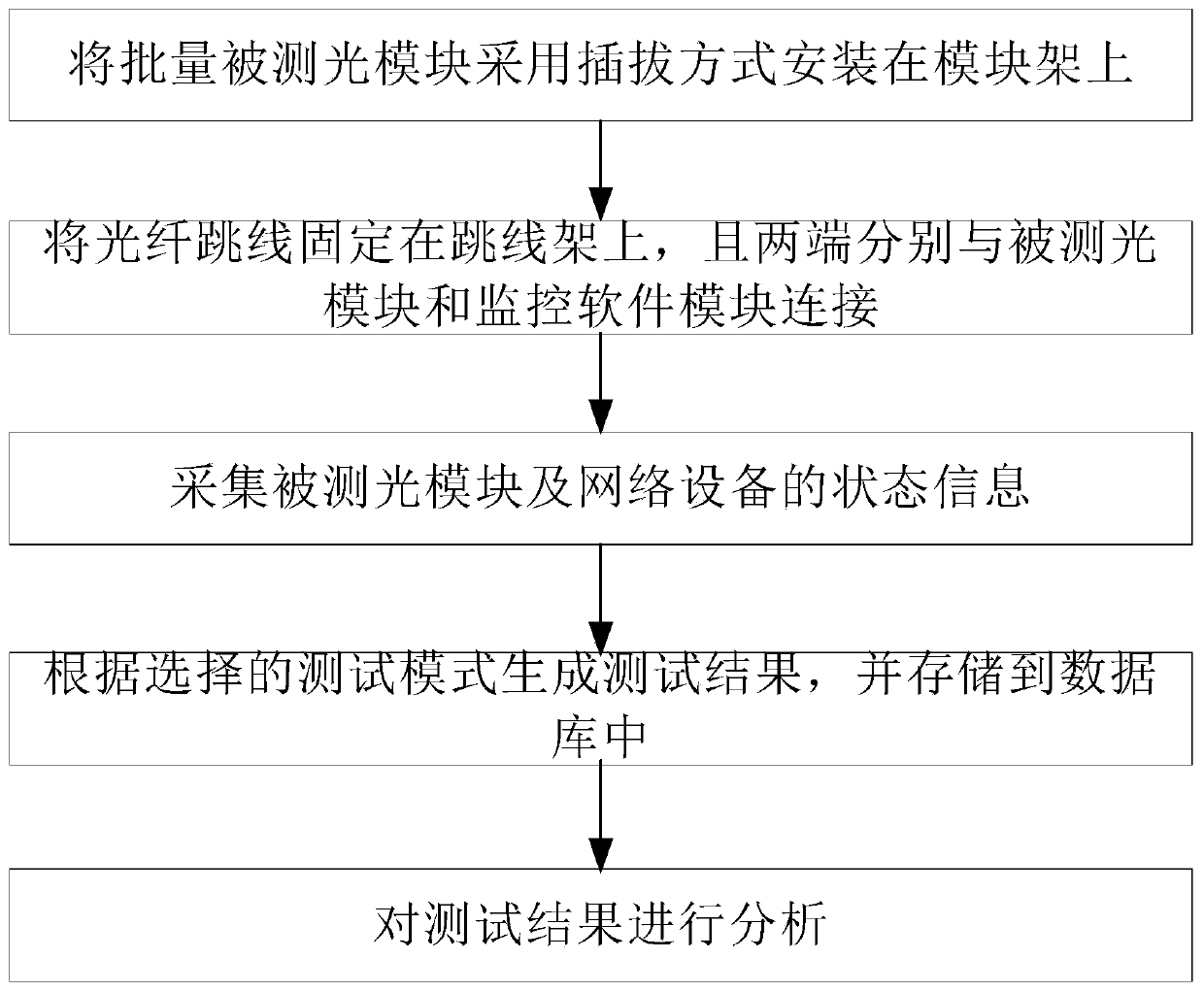

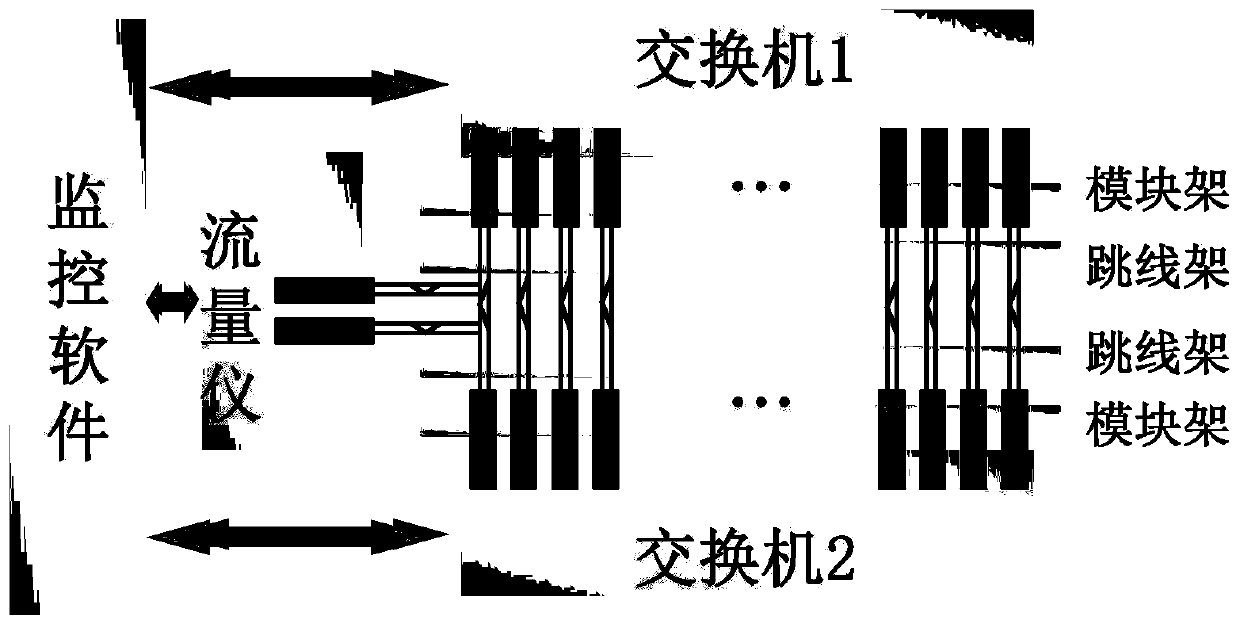

Optical module system-level batch detection system and method

InactiveCN110149145AEasy to operateImprove detection efficiencyMultiplex system selection arrangementsElectromagnetic transmissionComputer hardwareOptical Module

The invention discloses an optical module system-level batch detection system and method, and the system comprises a module frame which is used for fixing optical modules; a jumper frame used for fixing an optical fiber jumper; and a monitoring software module used for acquiring state information of the tested optical module and the network equipment, generating a test result according to the testmode selected by the user, analyzing the test result and storing the test result in a database. The system is used for carrying out system-level batch detection on the optical modules. The operationis simple and the detection efficiency is high. Hot plug testing, power-on and power-off testing, connectivity testing, EEPROM information testing, digital diagnosis testing, flow testing and the likeof the module on network equipment such as a switch and the like can be realized. The system fills the gap of system-level testing between the optical module and network equipment such as a switch, and is widely applied to the aspects of factory delivery detection module quality of optical module manufacturers, switch factory detection hardware welding quality, switch factory detection module compatibility and the like.

Owner:浪潮思科网络科技有限公司

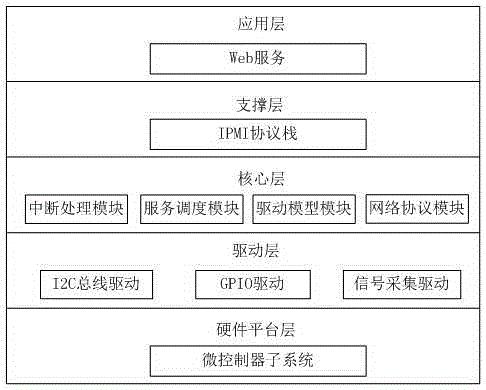

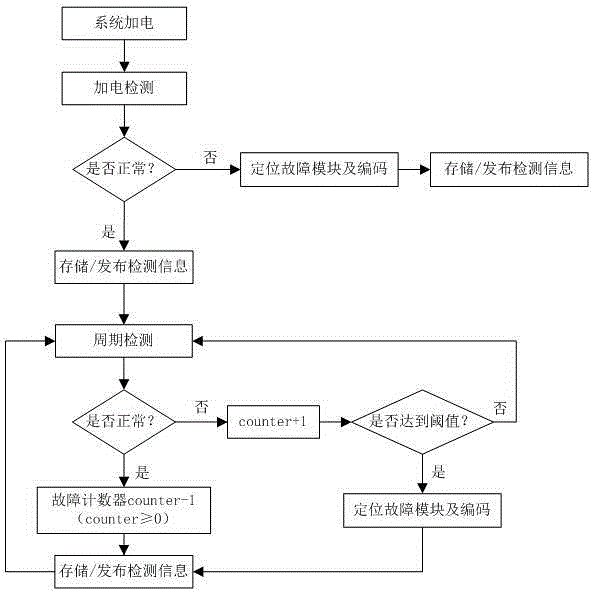

Homemade computer based build in test system and method

InactiveCN105183593AReal time monitoringReal-time managementDetecting faulty computer hardwareSystem level testingProtocol Application

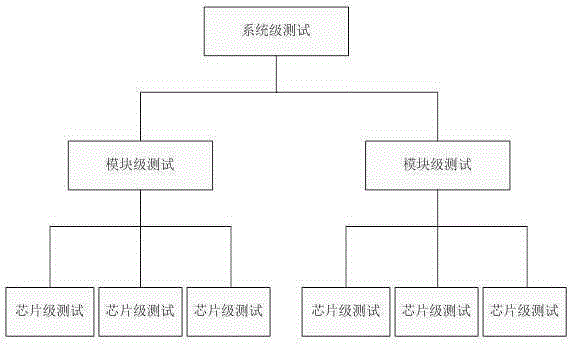

The invention discloses a homemade computer based build in test system and method, which belong to the technical field of computer self-detection and achieve the effects that a build in test (BIT) function of a homemade computer is realized and the demands of a homemade computer platform on possession of fault detection and isolation capabilities and shortening of maintenance time are met. The technical scheme is that: the homemade computer based build in test system and method is provided; hardware involved in the system comprises a system-level testing module, a module-level testing module and a chip-level testing module; and software layers involved in the system include a hardware platform layer, a driver layer, a kernel layer, a support layer and an application layer. The homemade computer based build in test system and method adopts the self-detection system, performs self-detection on the homemade computer, and comprises power-on BIT, periodic BIT and maintenance BIT.

Owner:SHANDONG CHAOYUE DATA CONTROL ELECTRONICS CO LTD

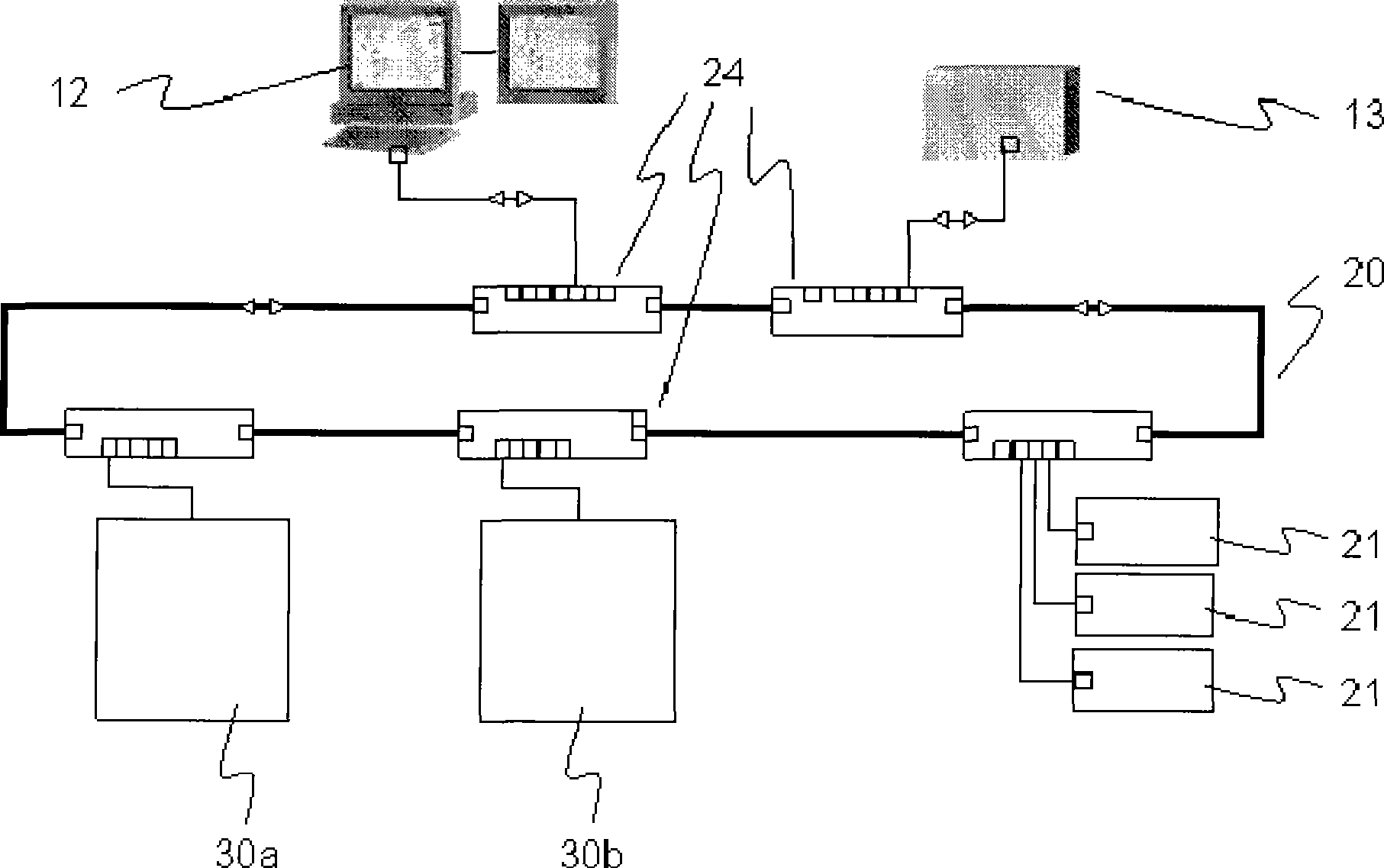

Scalable platform for system level testing

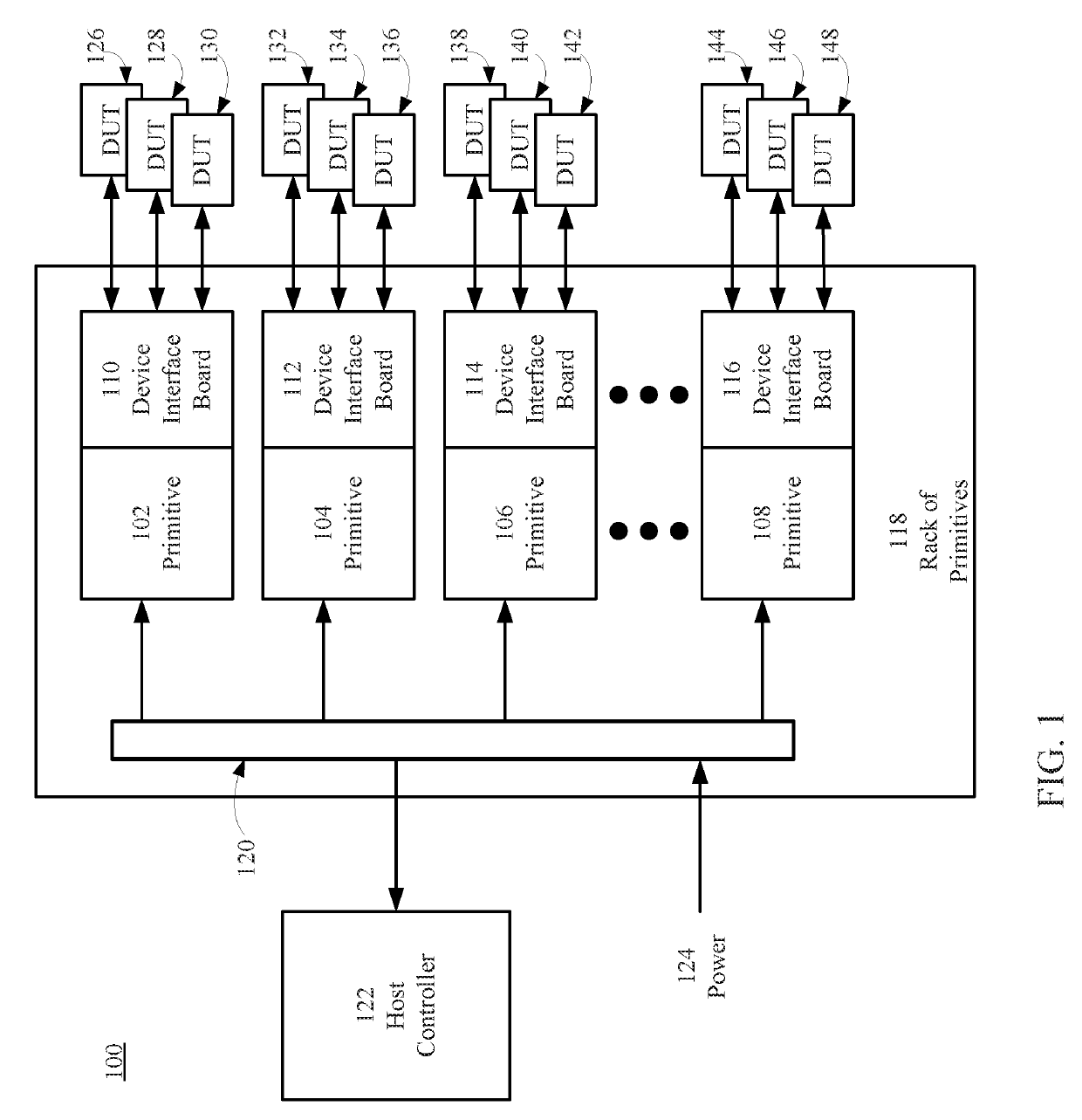

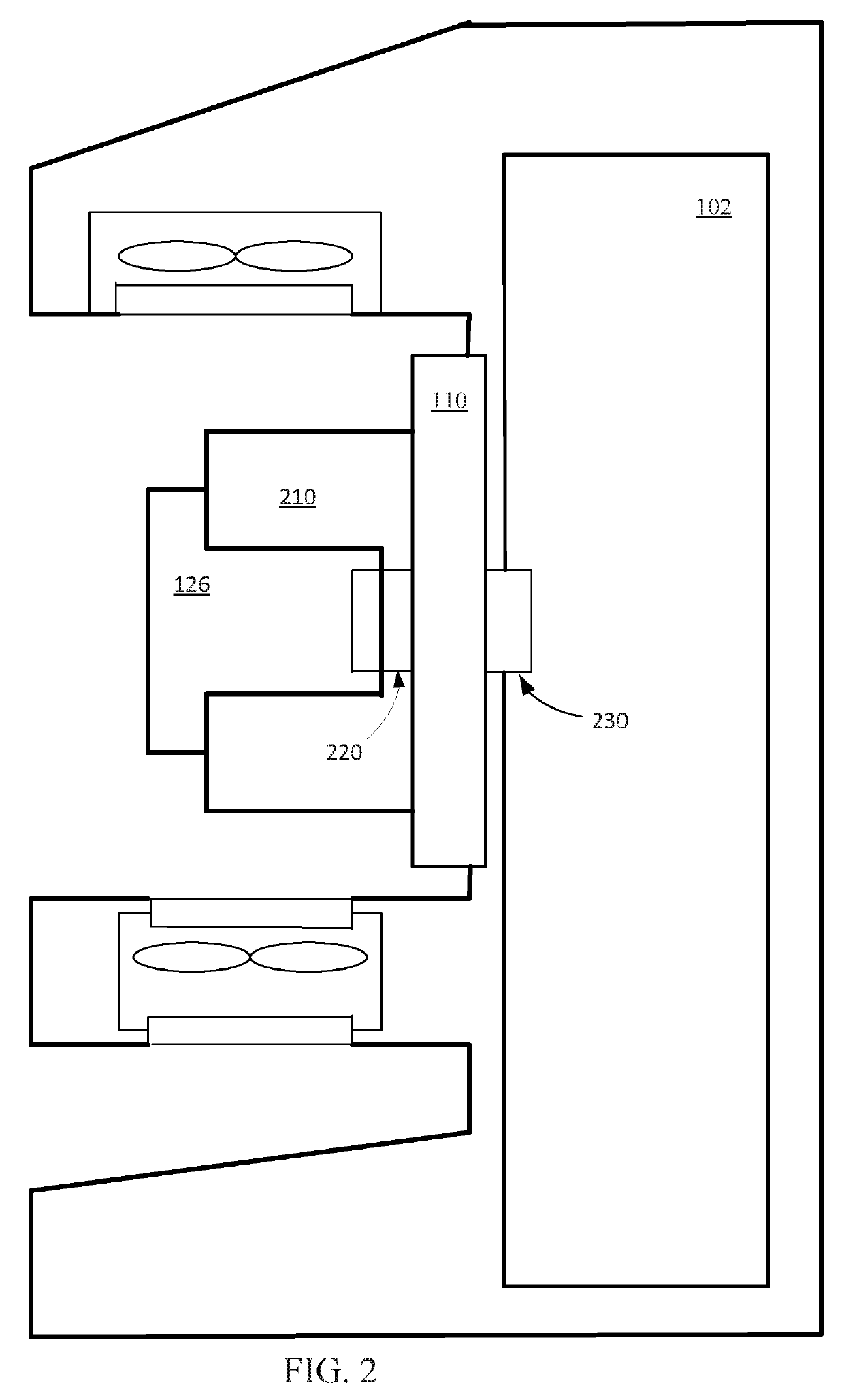

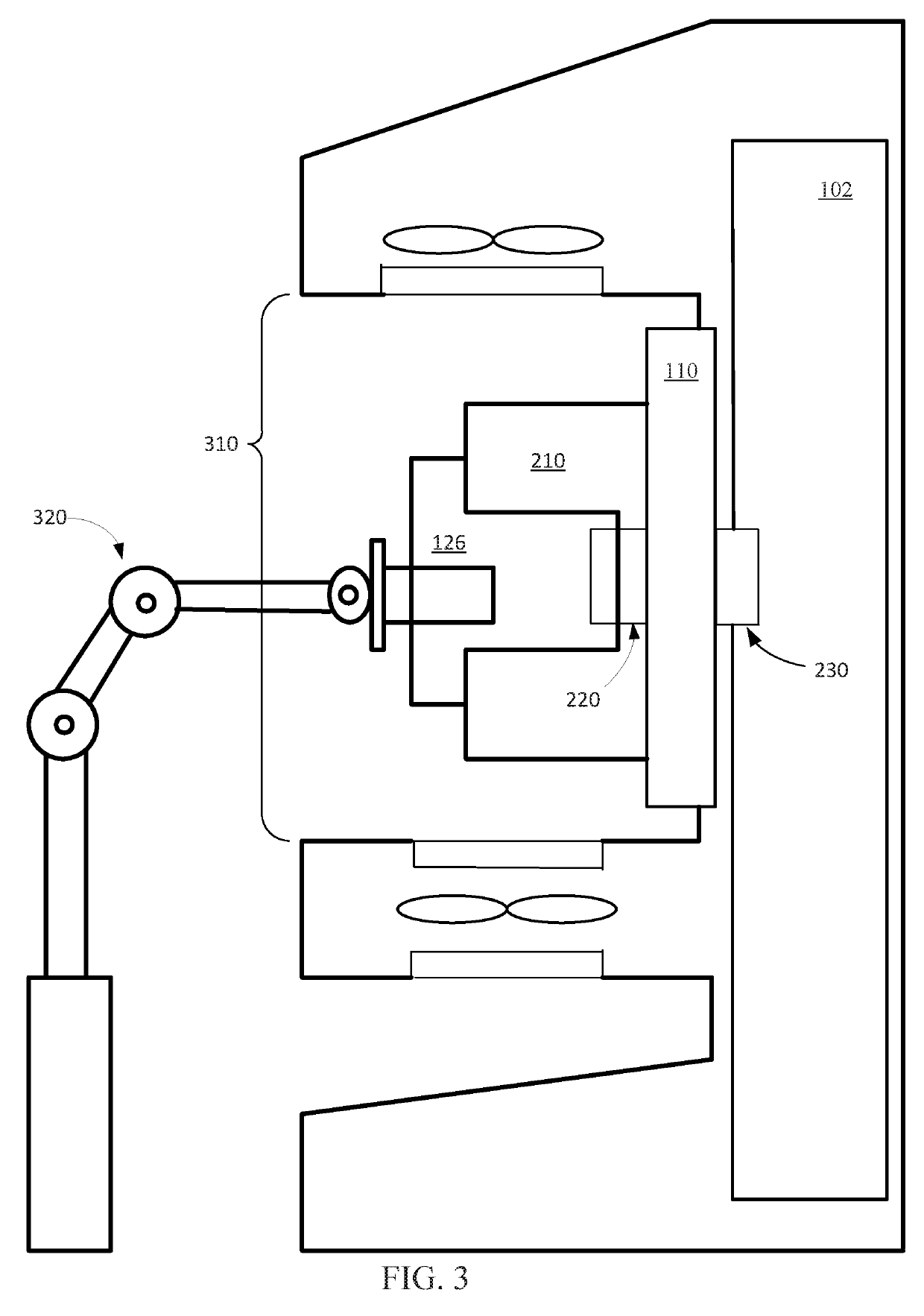

ActiveUS20190277907A1Readily re-configuredProvide a scalable test systemError detection/correctionMeasurement instrument housingDistributed powerSystem level testing

A scalable test platform can include one or more of a plurality of different device interface boards and a plurality of primitives. The different device interface boards can be configured to provide a uniform interface to couple different types of DUTs and or DUTs with different form factors to the plurality of primitives. The plurality of primitives can be configured to distribute power to the DUTs, and to perform system level testing of the respective DUTs. The plurality of primitives can be configurable by a user to perform any number of system level tests on a number of different types of DUTs and or DUTs with different form factors.

Owner:ADVANTEST CORP

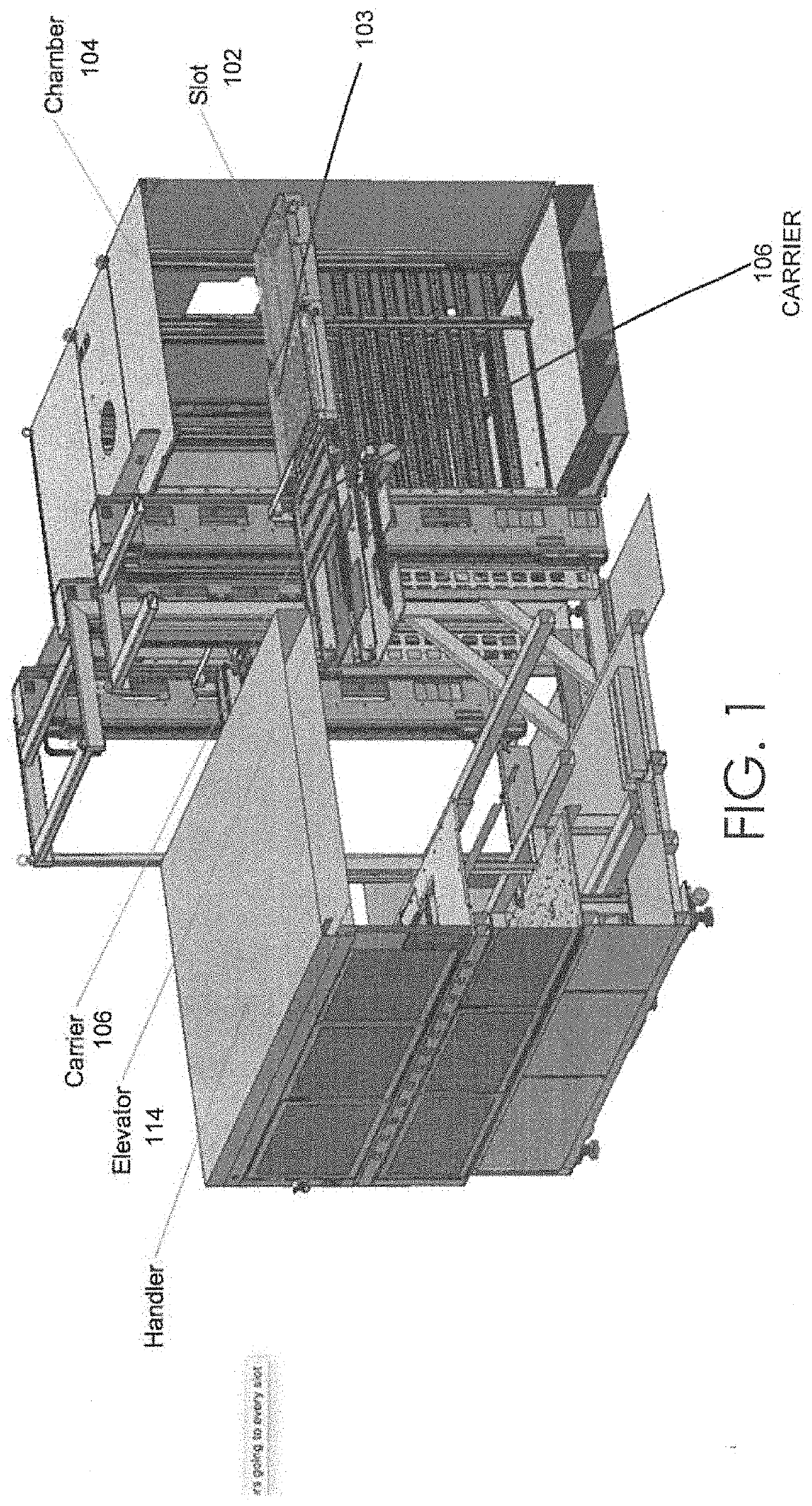

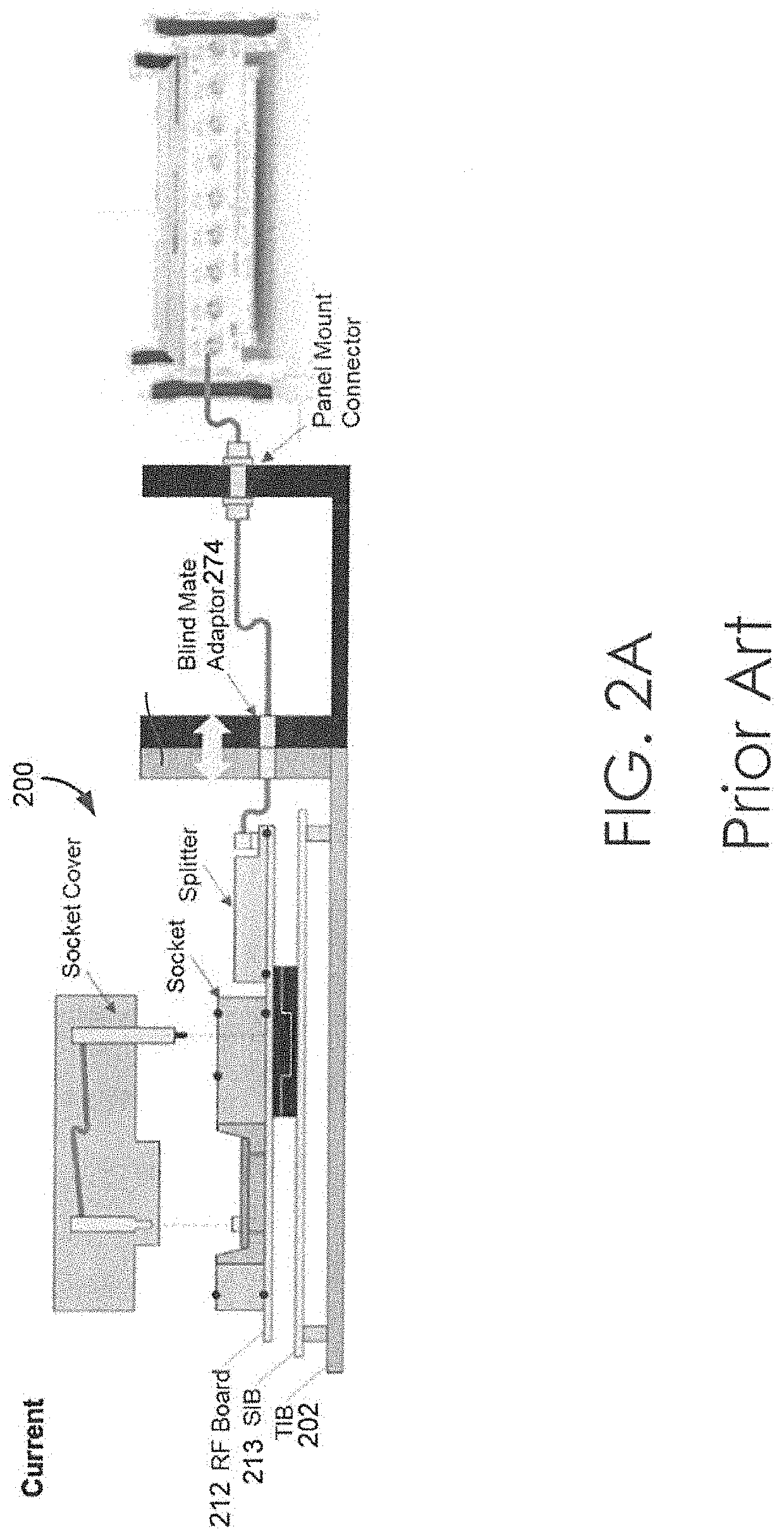

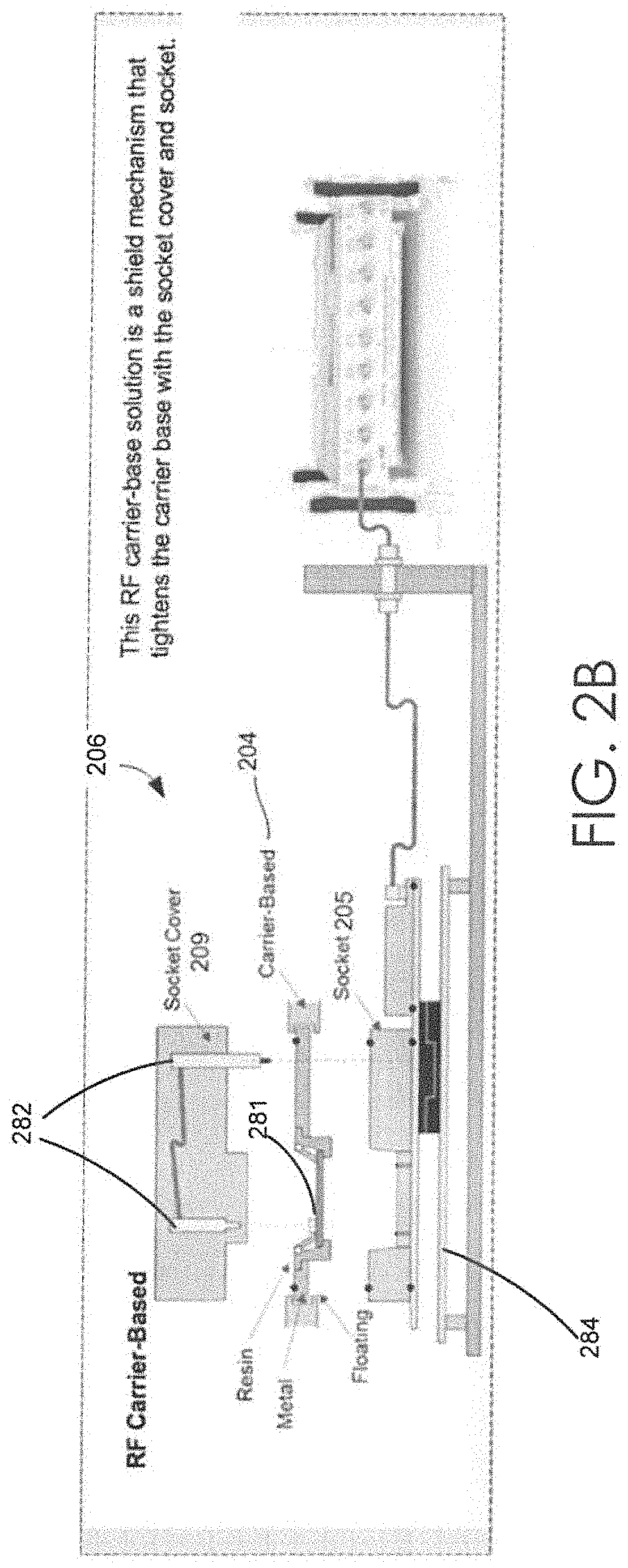

Carrier based high volume system level testing of devices with pop structures

ActiveUS20220284982A1Simplify System DesignImprove performanceDigital circuit testingStatic storageTester deviceHemt circuits

A testing apparatus comprises a tester comprising a plurality of racks, wherein each rack comprises a plurality of slots, wherein each slot comprises: (a) an interface board affixed in a slot of a rack, wherein the interface board comprises test circuitry and a plurality of sockets, each socket operable to receive a device under test (DUT); and (b) a carrier comprising an array of DUTs, wherein the carrier is operable to displace into the slot of the rack; and (c) an array of POP memory devices, wherein each POP memory device is disposed adjacent to a respective DUT in the array of DUTs. Further, the testing apparatus comprises a pick-and-place mechanism for loading the array of DUTs into the carrier and an elevator for transporting the carrier to the slot of the rack.

Owner:ADVANTEST TEST SOLUTIONS INC

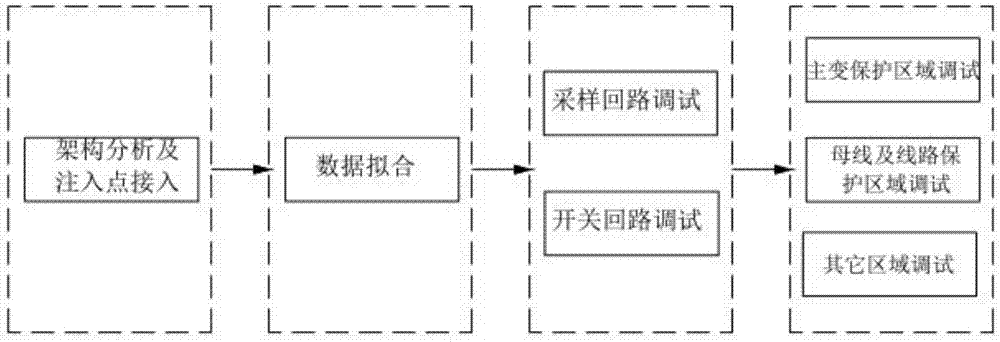

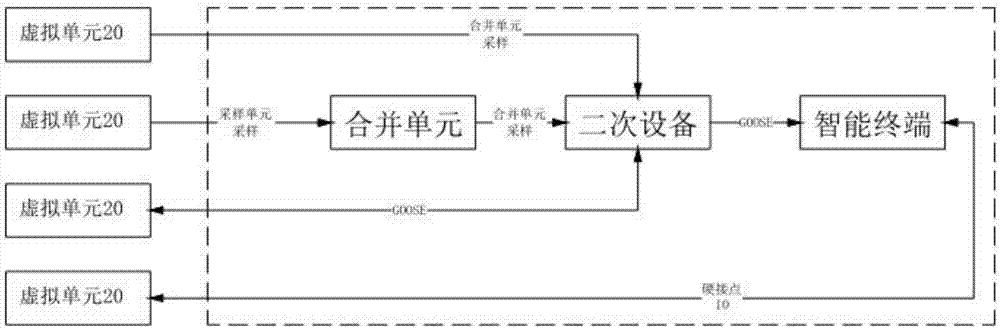

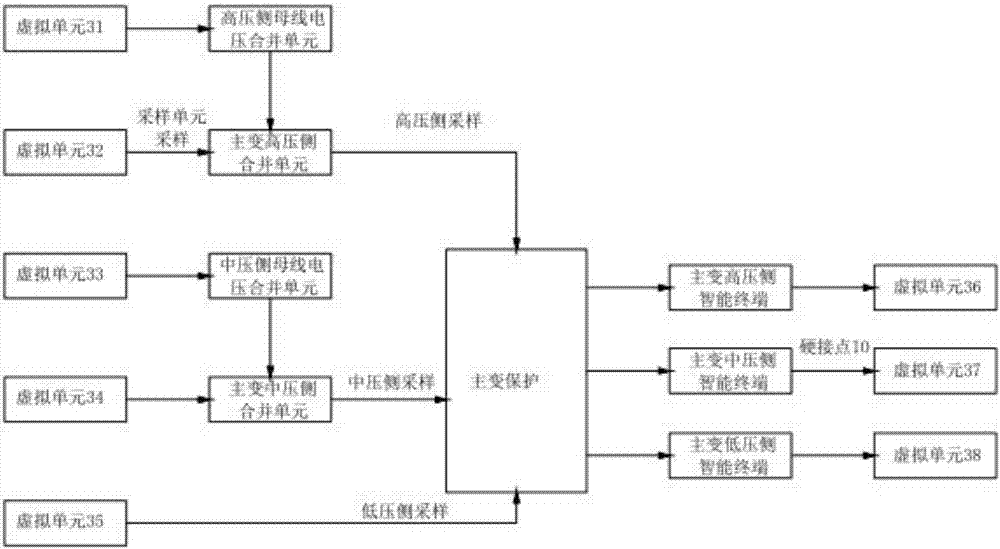

Multipoint virtual data injection type intelligent transformer substation site debugging method

InactiveCN108008223AExpand coverageRealize systematic debuggingElectrical testingElectric testing/monitoringConfiguration analysisSmart substation

The invention discloses a multipoint virtual data injection type intelligent transformer substation site debugging method. The multipoint virtual data injection type intelligent transformer substationsite debugging method comprises the following steps of (1) configuration analysis: determining a site test configuration of an intelligent transformer substation, a test data injection point quantityand a type; (2) data fitting: according to a sampling interval or a switch interval, virtualizing test data of all injection points; (3) sampling and switch loop debugging: debugging a sampling loopand a switch loop of the intelligent transformer substation; and (4) subsystem debugging: regionally debugging a secondary system of the intelligent transformer substation. The debugging method of theinvention is used to increase safety, reliability and economy of intelligent transformer substation construction engineering, a system acceptance period is effectively shortened, a guidance is provided for a lot of system-level tests in the further, and a good engineering application value is possessed.

Owner:STATE GRID JIANGSU ELECTRIC POWER CO LTD NANTONG POWER SUPPLY BRANCH

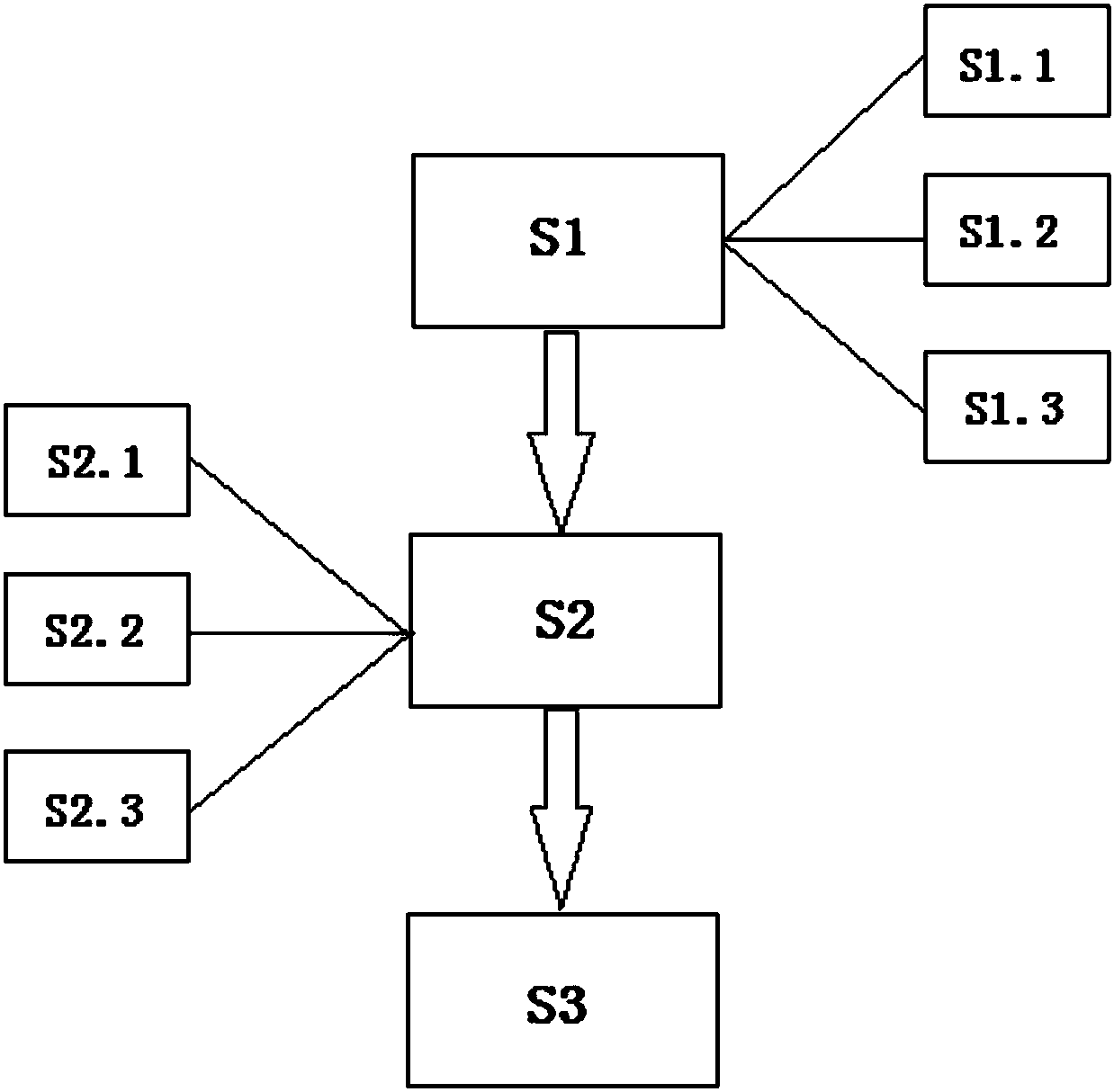

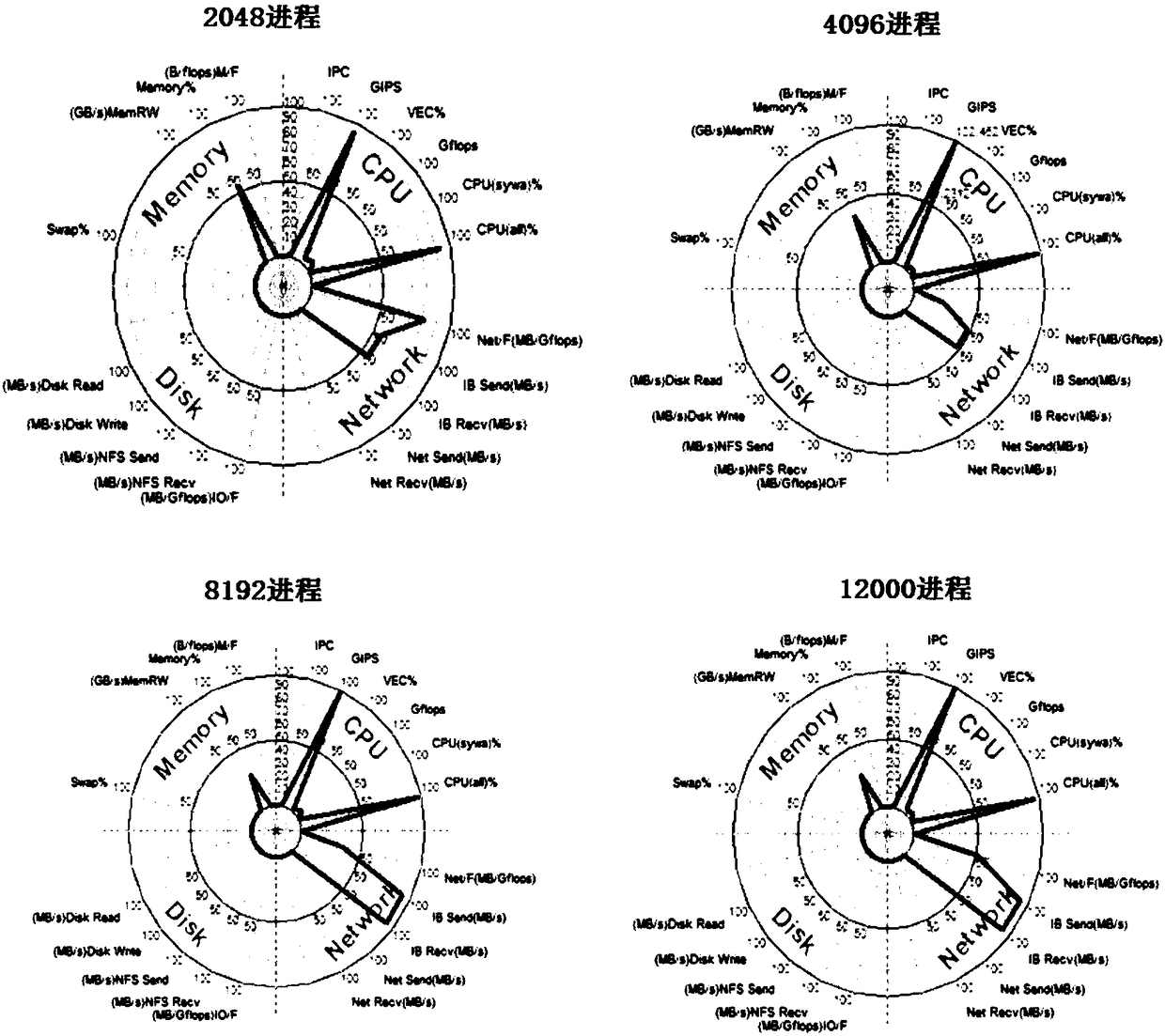

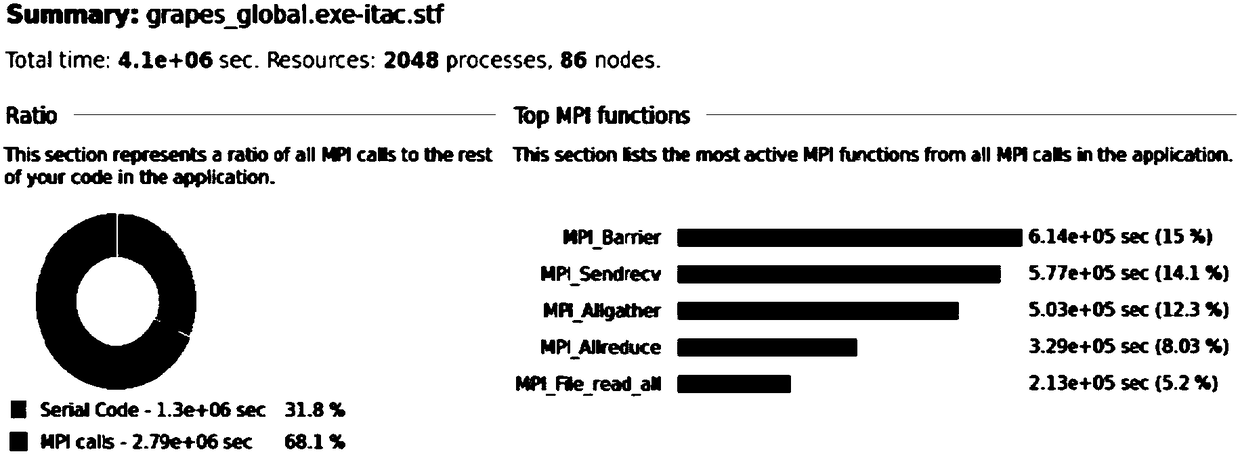

GRAPES system optimization method based on parallel supercomputing grid cloud platform

ActiveCN108132872ASolve optimization problemsImprove accuracyHardware monitoringSoftware testing/debuggingData setSystem testing

The invention relates to a GRAPES system optimization method based on a parallel supercomputing grid cloud platform. The method comprises the steps that (S1) a test dataset is loaded, a system is run,and (S1.1) a system-level test, (S1.2) a communication-level test and (S1.3) a function-level test are performed separately, wherein in the (S1.3) function-level test, a called function is monitored,and running features of the function are acquired; (S2), test result analysis is performed according to an exported system feature file, wherein test result analysis comprises (S2.1) system test result analysis, (S2.2) MPI communication-level test result analysis and (S2.3) function-level test result analysis; and (S3) optimization processing is performed according to analysis results, wherein optimization processing comprises vectorization, load balancing and replacement of a function in a GRAPES_GFS by use of a library function. Through the method, optimization of Grapes on the parallel supercomputing grid platform is realized, and system running efficiency is improved.

Owner:CHENGDU UNIV OF INFORMATION TECH

In-process system level test before surface mount

ActiveUS20080001618A1Low costReduce wasteIndividual semiconductor device testingProcess systemsSurface mounting

Owner:NVIDIA CORP