Supercomputer using wafer scale integration

一种晶片、芯片的技术,应用在大规模并行超级计算机领域,能够解决电气连接数限制等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

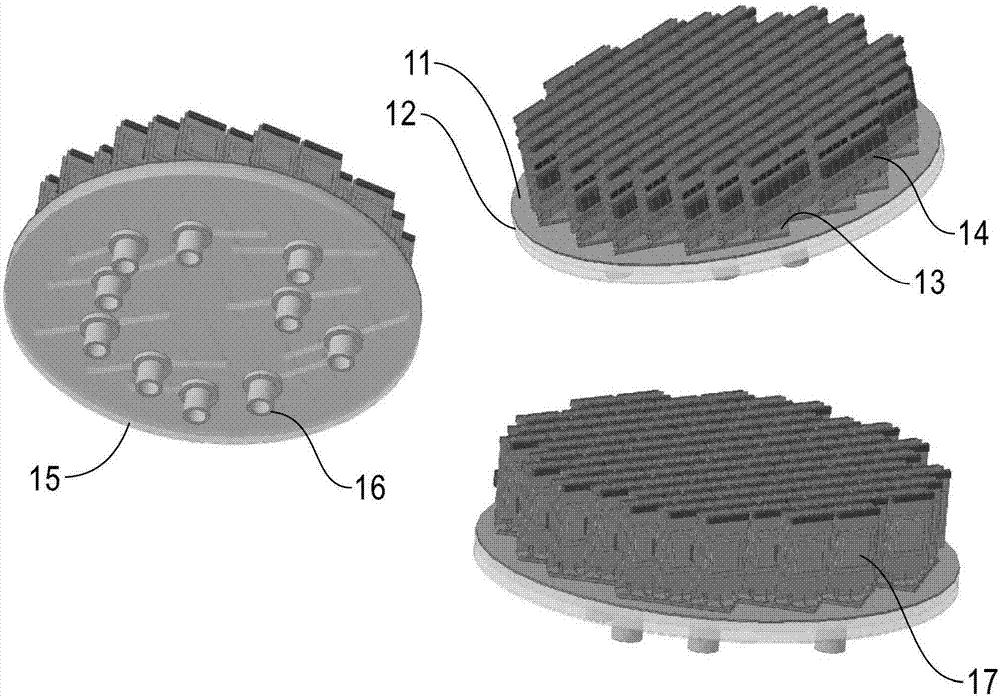

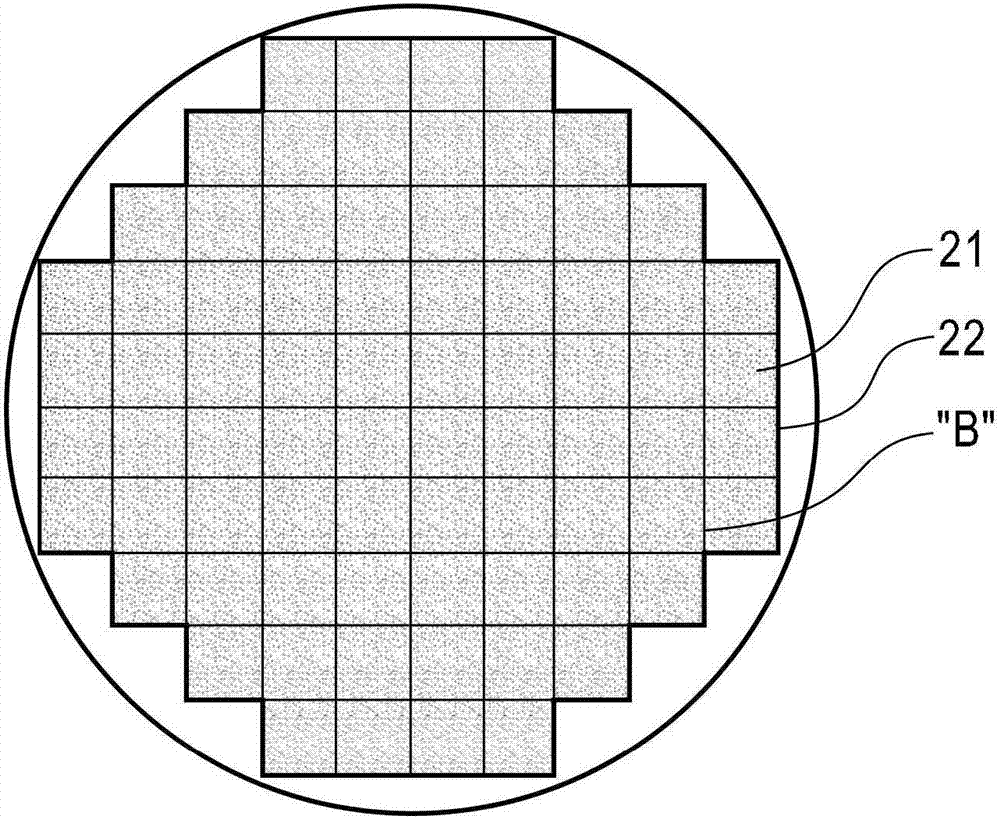

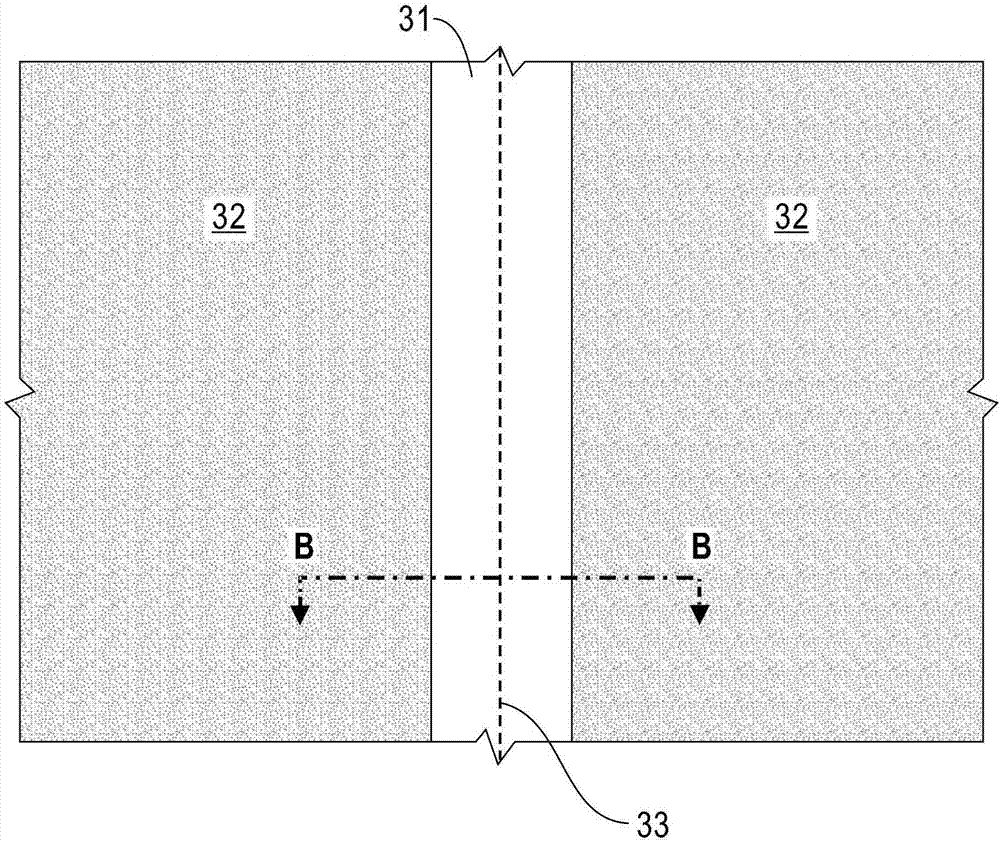

[0030] Exemplary embodiments of the invention described herein generally include supercomputers fabricated using wafer-level integration and methods of fabrication thereof. Therefore, while the embodiments of the present invention are susceptible to various modifications and alternative forms, specific embodiments thereof have been shown by way of example in the drawings and will be described in detail herein. It should be understood, however, that there is no intention to limit the embodiments of the invention to the particular exemplary embodiments disclosed, but on the contrary, embodiments of the invention are to cover all modifications, equivalents, and alternatives falling within the scope of the invention.

[0031] Exemplary embodiments of the invention include a wafer whose surface is completely populated with many small processors that are electrically interconnected using upper-level chip wiring, a connectivity scheme known as wafer-level integration. Chip-to-chip in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More