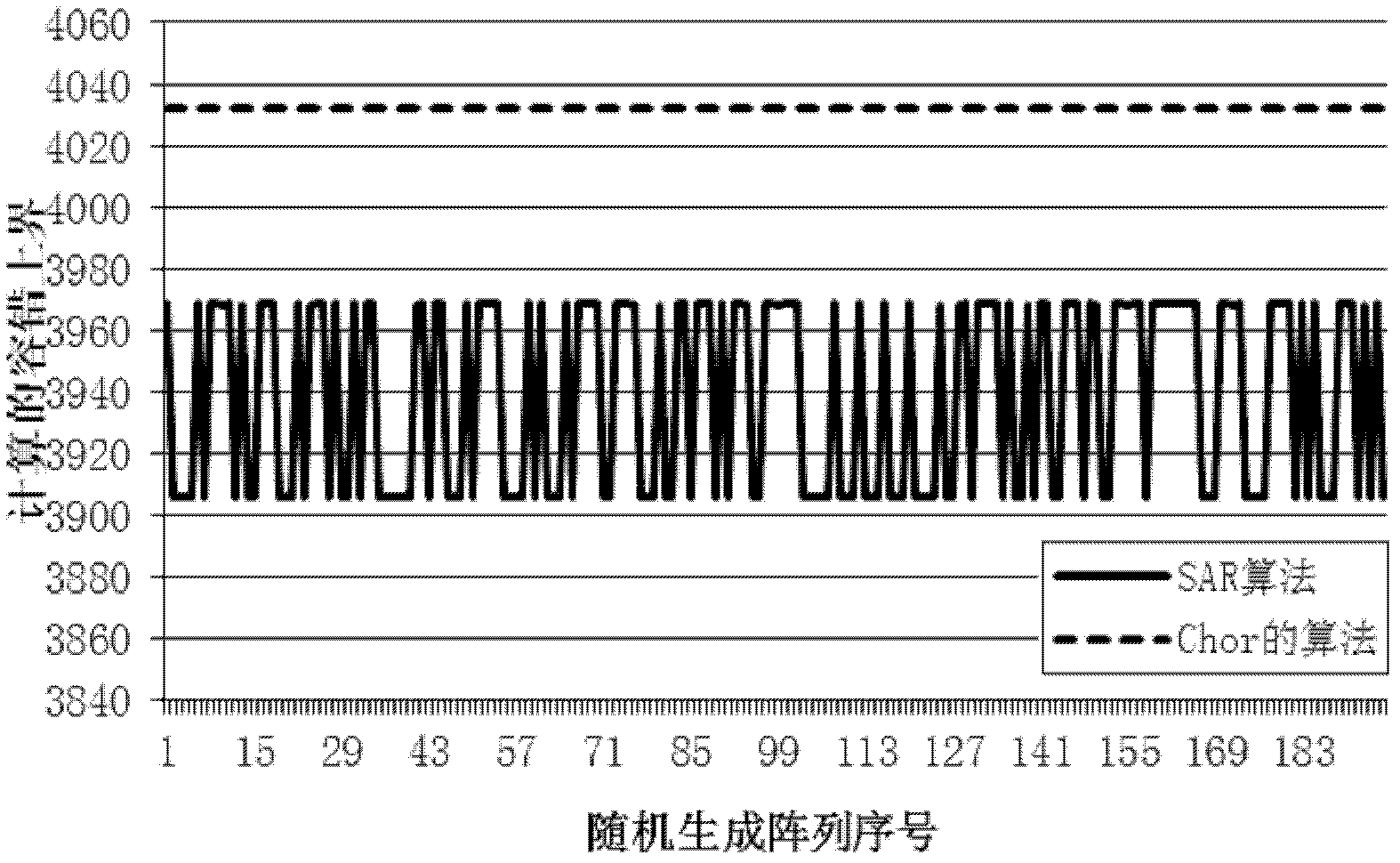

Method for solving fault-tolerant upper bound of reconfigurable multiprocessor array

A processor array and multi-processor technology, applied to the generation of response errors, combination of various digital computers, etc., can solve the problem of high fault-tolerant upper bound, and achieve the effect of accurate fault-tolerant upper bound

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0057] Below in conjunction with accompanying drawing, the present invention is described in further detail:

[0058] In order to improve the existing methods, the present invention introduces the following concepts:

[0059] 1. The unavailable processor unit refers to such a processor: the processor unit is not physically damaged, but due to the presence of damaged processor units nearby, the processor unit no matter which routing method is used cannot be included in the refactored postprocessor array;

[0060] The method for marking all unusable processors evolved from damaged processor units in the array is as follows:

[0061] (1) If an undamaged processor unit is in row r, column c (denoted as P r,c ), then when P r+1,c-1 , P r+1,c , P r+1,c+1 When the processor unit is damaged or unusable, P r,c is an unavailable processor unit; when P r-1,c-1 , P r-1,c , P r-1,c+1 When the processor unit is damaged or unusable, P r,c is an unavailable processor unit;

[0062]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More