DVFS-based optimal reconfiguration algorithm

A reconfiguration and algorithm technology, applied in computing, computers, computer components, etc., can solve problems such as unreliability, achieve the effects of improving reliability, reducing overhead, and maximizing stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The present invention will be further described below in conjunction with specific embodiments. It should be understood that these embodiments are only used to illustrate the present invention and not to limit the scope of the present invention. In addition, it should be understood that after reading the teachings of the present invention, those skilled in the art can make various changes or modifications to the present invention, and these equivalent forms also fall within the scope defined by the appended claims of the present application.

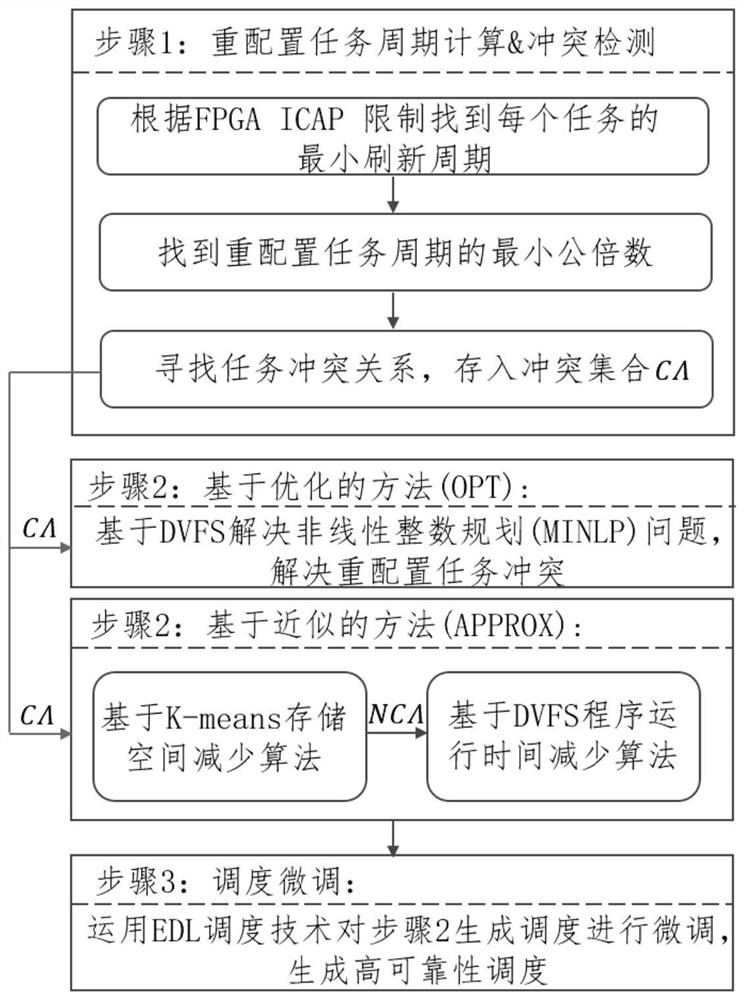

[0034] Such as figure 1 As shown, an optimized reconfiguration algorithm based on DVFS provided by the present invention includes the following steps:

[0035] Step 1: First extract the user task information mapped to all user tasks in the FPGA system, where the user task information of the i-th user task includes the running period T of the user task i , The maximum operating frequency of user tasks f i .

[0036] For the i-th user ta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More