Address transition detection circuit and method

A detection circuit and address conversion technology, applied in information storage, static memory, digital memory information, etc., can solve problems such as large chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] The invention discloses a signal detection circuit suitable for detecting address transitions on multiple address signal lines in a memory device. The circuit can also be used to detect transitions of other signals such as die select control signals or die enable control signals.

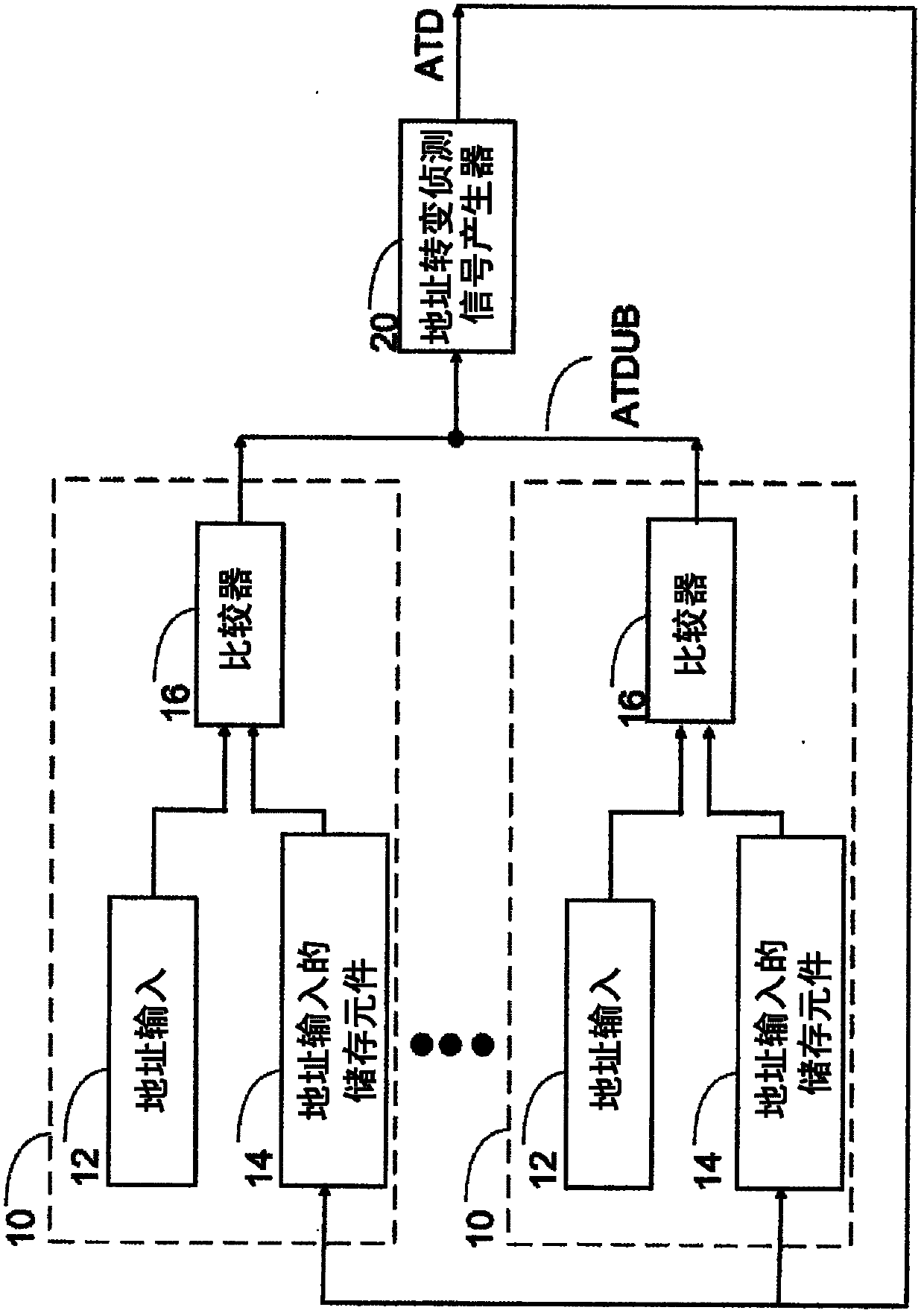

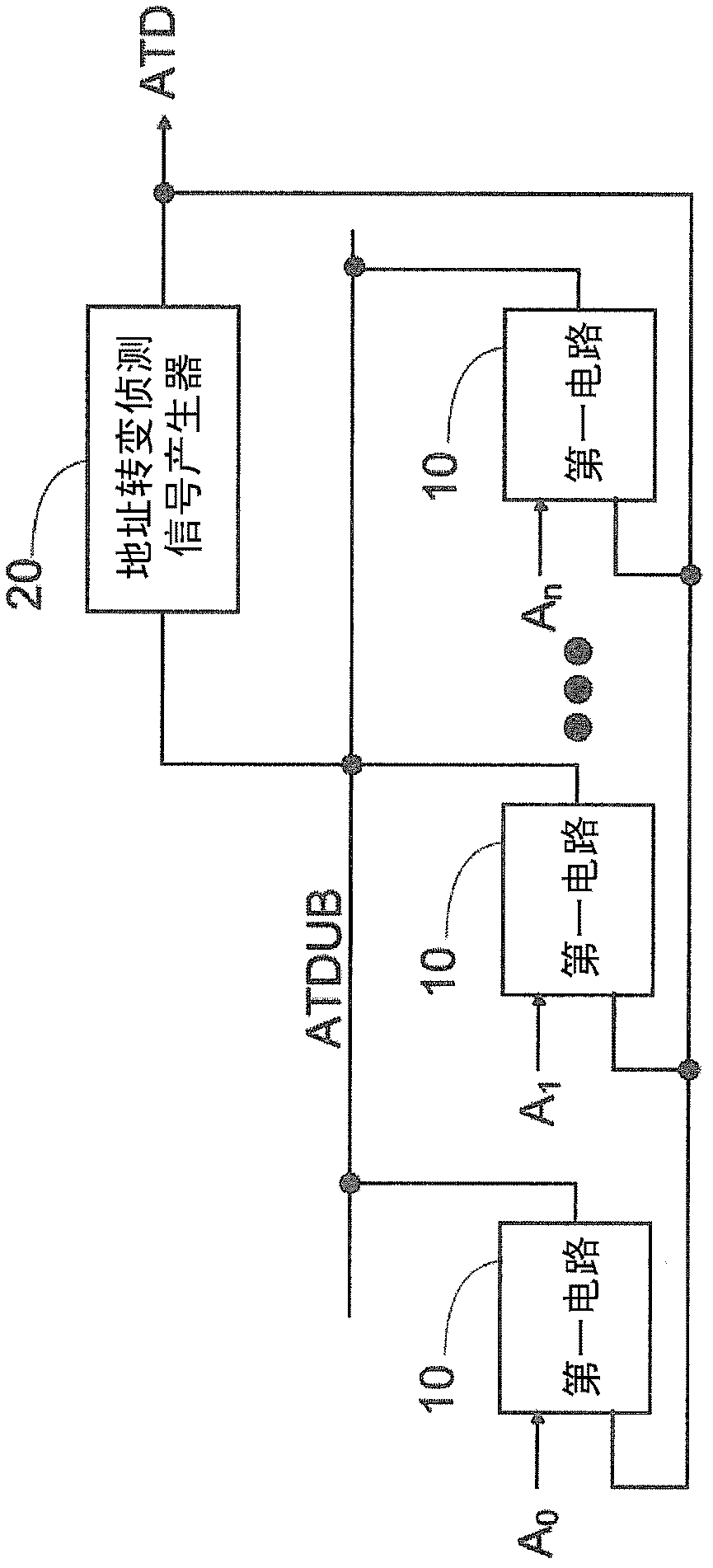

[0048] figure 2 A block schematic diagram of an embodiment of the invention is shown. The block diagram includes a plurality of first circuits 10 corresponding to a plurality of address signal lines, and an address transition detection signal (ATD) generator 20 (second circuit). Each first circuit 10 includes a comparator 16 which compares an input address at the address input 12 with the stored address in the storage element 14 . The address input 12 includes a signal line corresponding to an address signal line, such as a signal line connected to an input pin of an integrated circuit or a line connected to an address generator in an integrated circuit. For example, a 32-pin packaged mem...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com