A chip defect detection method

A detection method and technology for chip defects, applied in the direction of semiconductor/solid-state device testing/measurement, etc., can solve the problems of rough detection, inability to accurately perform defect detection, and influence of defect detection accuracy, and achieve the effect of improving the success rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

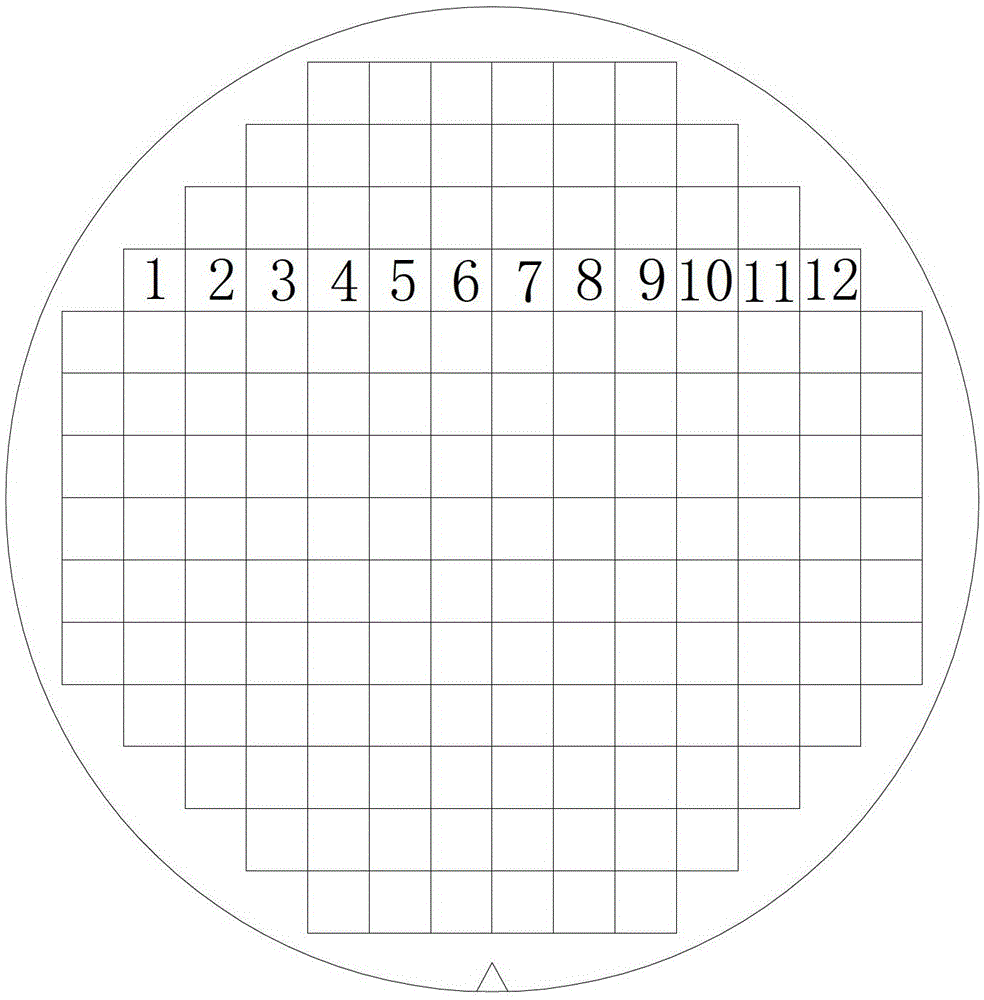

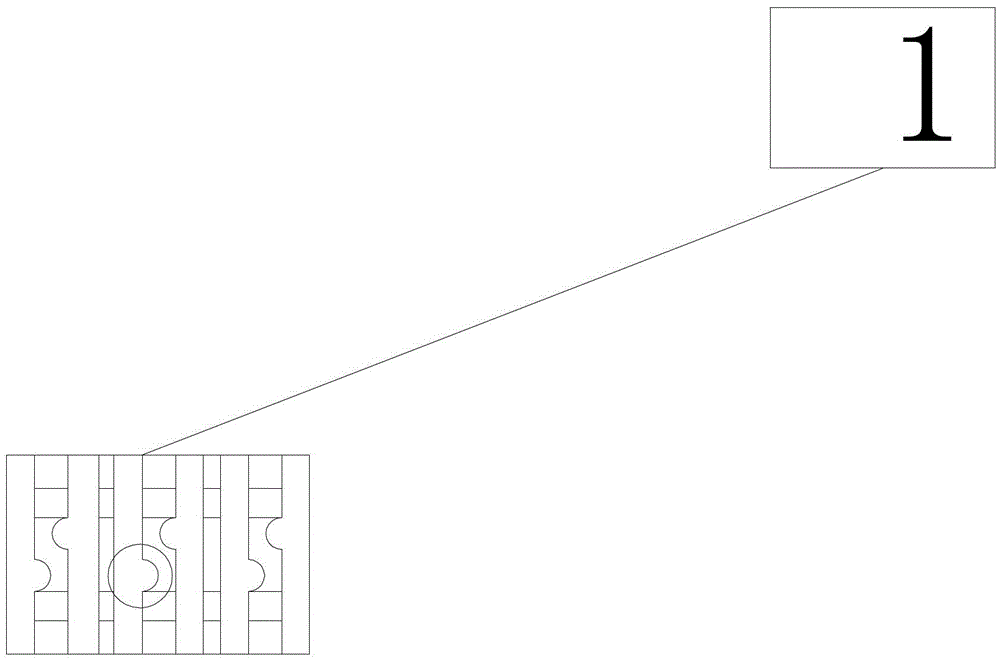

[0055] First, the position of the wafer with multiple identical chips prepared on the surface is fixed. The multiple identical chips are arranged in a matrix. After the wafer position is fixed, a direction is selected to scan the wafer row by row. The optical detection equipment may preferably adopt high-sensitivity optical detection equipment to perform the progressive scanning, and obtain optical images of all the chips in the entire wafer to be tested by scanning the wafer progressively.

[0056] Then, the obtained optical image is converted into a data image represented by different bright and dark gray scales, so as to be used in the subsequent detection and comparison process.

[0057] Such as figure 2 As shown, the chip in the fourth row and the fourth column starting from the top of the wafer is selected as the chip 4 to be tested in the entire wafer, and an appropriate spacing value is selected according to the manufacturing process of the chip to be tested. In this ...

Embodiment 2

[0061] The difference between this embodiment and Embodiment 1 is that when the chip to be tested is selected as Figure 4 As shown in , when it is located at the edge position of the wafer (such as row 4, column 1), at this time, since the chip to be tested is located at the first position in row 4, it is also the first position in column 1 position, at this time, no matter what value the spacing value is set to, the chip to be tested can not find two contrasting chips equal to the spacing of the chip to be tested no matter in the row or the column. Therefore, in this embodiment, it is mainly solved. The detection problem of a class of chips.

[0062] Same as Example 1, firstly, the position of the wafer with multiple identical chips prepared on the surface is fixed, wherein the multiple identical chips are arranged in a matrix, and after the wafer position is fixed, a direction is selected to carry out the process on the wafer. Progressive scanning, wherein an optical detec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com