Method measuring interlayer offset of printed circuit board (PCB) and in-process PCB

An offset and measurement technology, applied in the direction of measuring devices, electrical connection printing components, instruments, etc., can solve problems such as the inability to detect offsets

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be described in detail below with reference to the accompanying drawings and in combination with embodiments.

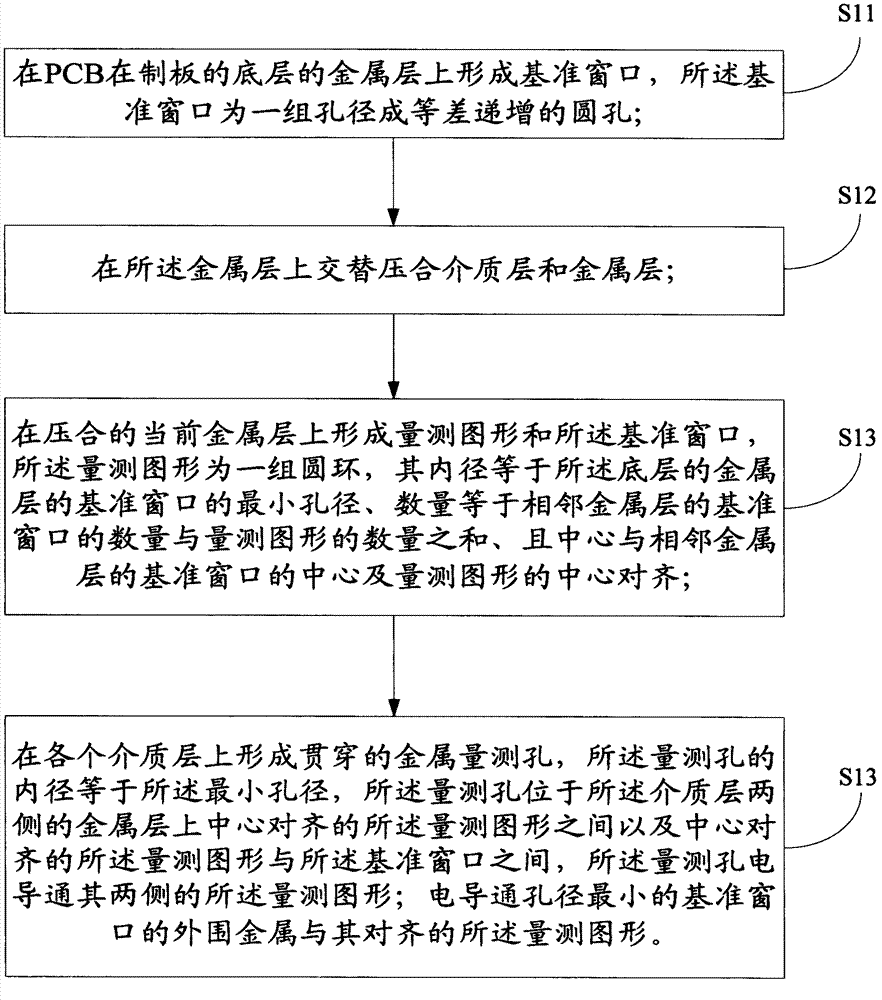

[0036] see figure 1 , an embodiment of the present invention includes the following steps:

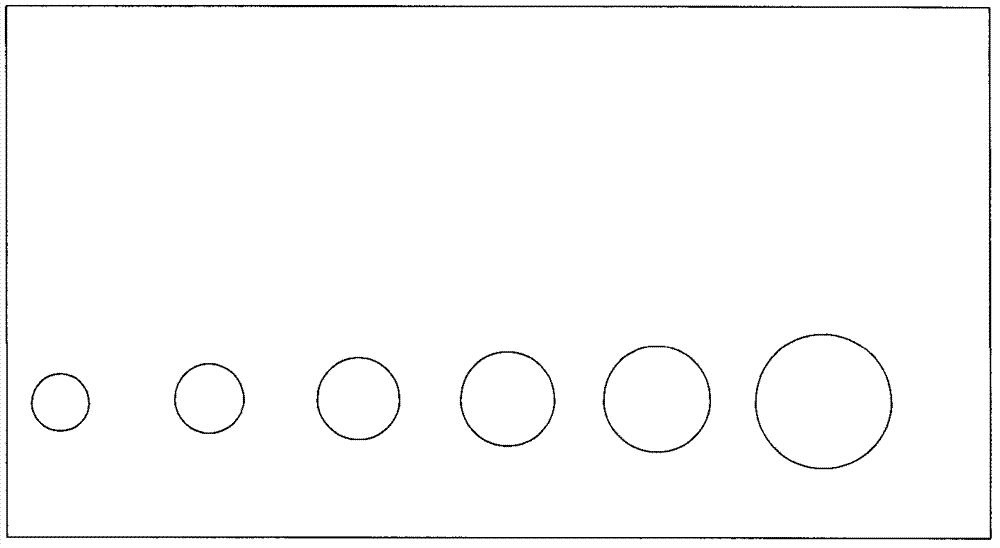

[0037] S11: forming a reference window on the metal layer of the bottom layer of the PCB, the reference window is a group of circular holes with increasing apertures;

[0038] see figure 2 In the top view of the bottom layer of the circuit board shown, round holes with increasing diameters are formed on the bottom metal layer.

[0039] The bottom layer can be any initial layer in the multilayer circuit board, for example, it can be the base layer, or it can be the outermost layer in the multilayer circuit board structure.

[0040] S12: Alternately laminating the dielectric layer and the metal layer on the metal layer;

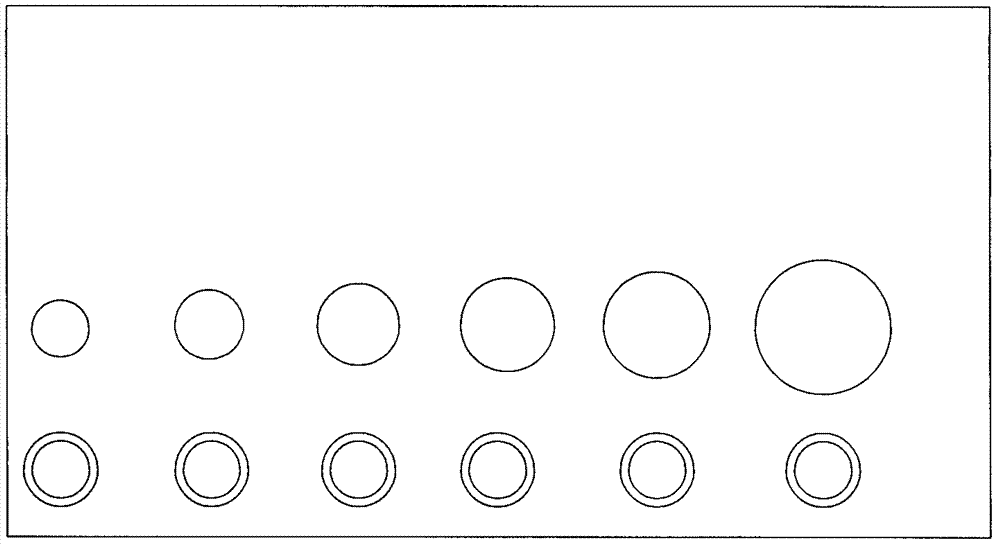

[0041] S13: Form a measurement pattern and the reference window on the pressed current metal layer, the measurement pat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More