A half-rate clock-data recovery circuit based on phase-selective interpolation

A technology of clock data recovery and phase selection, applied in the direction of electrical components, automatic power control, etc., can solve the problems of increasing the difficulty of digital controller design, redundant phase selection/interpolation circuits, etc., and achieve the goal of reducing design difficulty and reducing scale Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to further illustrate the advantages of the present invention and the specific technical means adopted, the specific implementation of a phase-selective interpolation-based half-rate clock data recovery circuit of the present invention will be further described in detail below in conjunction with the accompanying drawings.

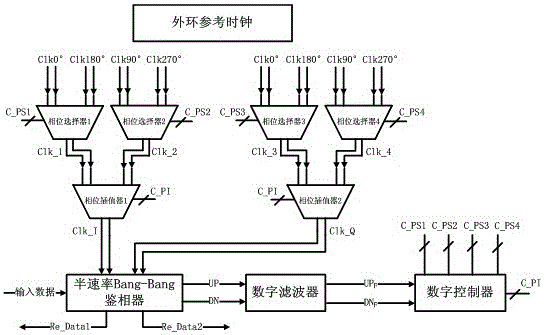

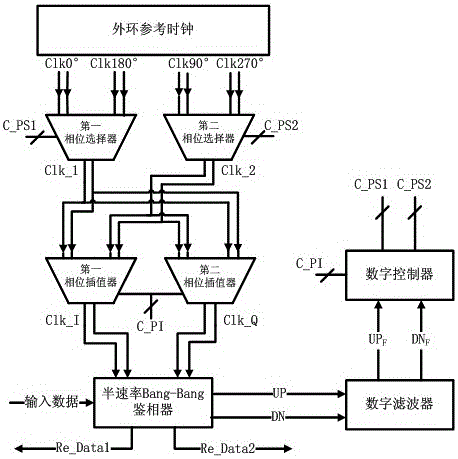

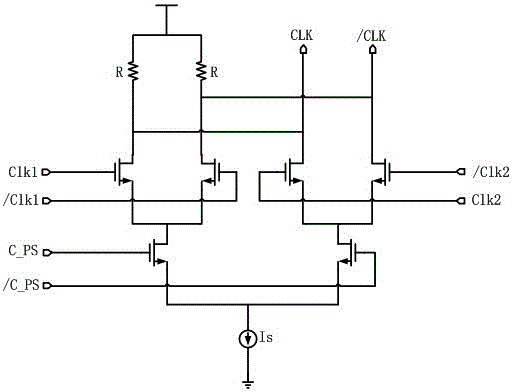

[0024] The half-rate clock data recovery circuit based on the phase selection interpolation type of the present invention, the clock data recovery circuit includes a half-rate Bang-Bang type phase detector, a digital filter, a digital controller, a phase selector, a phase interpolator, and outer ring reference clock;

[0025] The half-rate Bang-Bang type phase detector receives the input data and the clock signals Clk_I and Clk_Q output by the phase interpolator I, Q, and compares the phase relationship between the input data and Clk_Q to generate the first lead signal UP and the second lag signal DN; The first lead signal UP and the second...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More