Semiconductor chip test baseboard

A chip testing and semiconductor technology, applied in the direction of measuring devices, measuring device casings, measuring instrument components, etc., can solve the problems that the chip cannot be pressed down correctly, cannot meet the test requirements, cannot realize position adjustment, etc., and can expand the position adjustment range, The effect of meeting test requirements and improving positioning accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

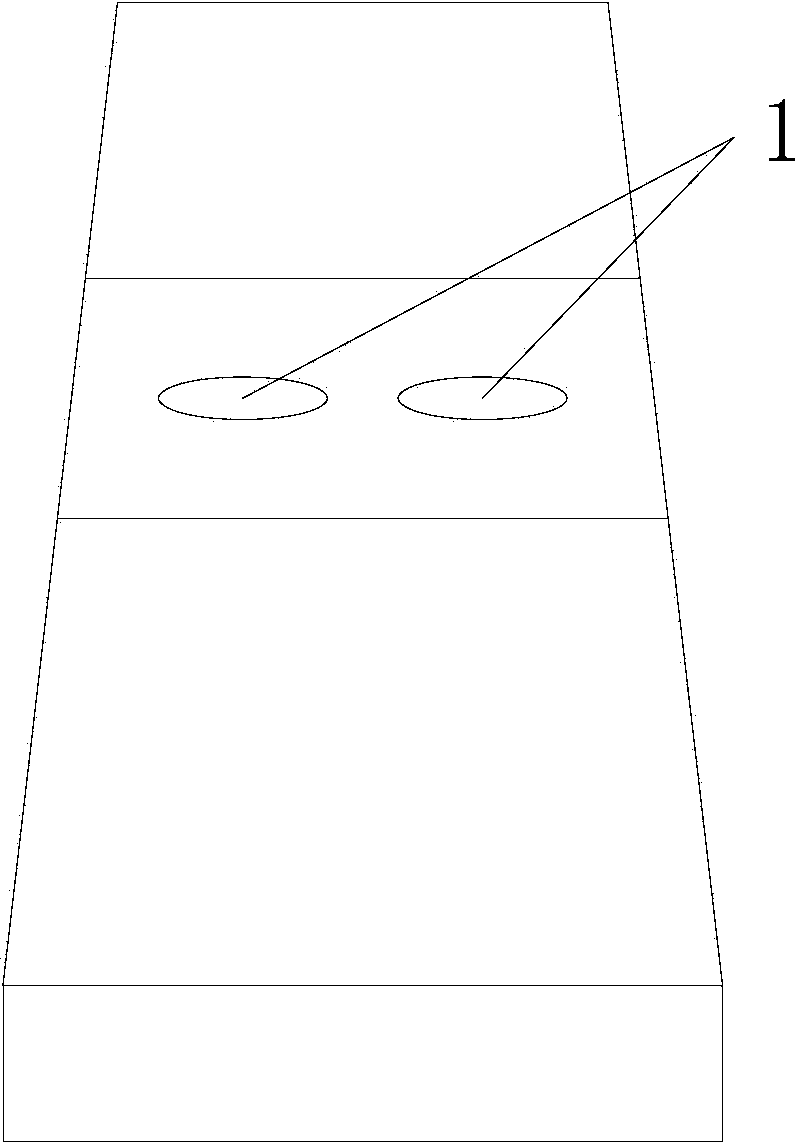

[0011] Embodiment 1: as attached figure 1 As shown, a semiconductor chip test base plate is provided with two positioning holes 1 on it. The shape of the positioning holes 1 is elliptical. The angular direction of the ellipse opening should be consistent.

[0012] When the test base plate is fixed on the test base, the positioning is roughly adjusted relative to the test base, and then finely adjusted and positioned through the test base to meet the test requirements, ensure that the chip is correctly pressed into the socket, protect the socket, and improve the test yield .

Embodiment 2

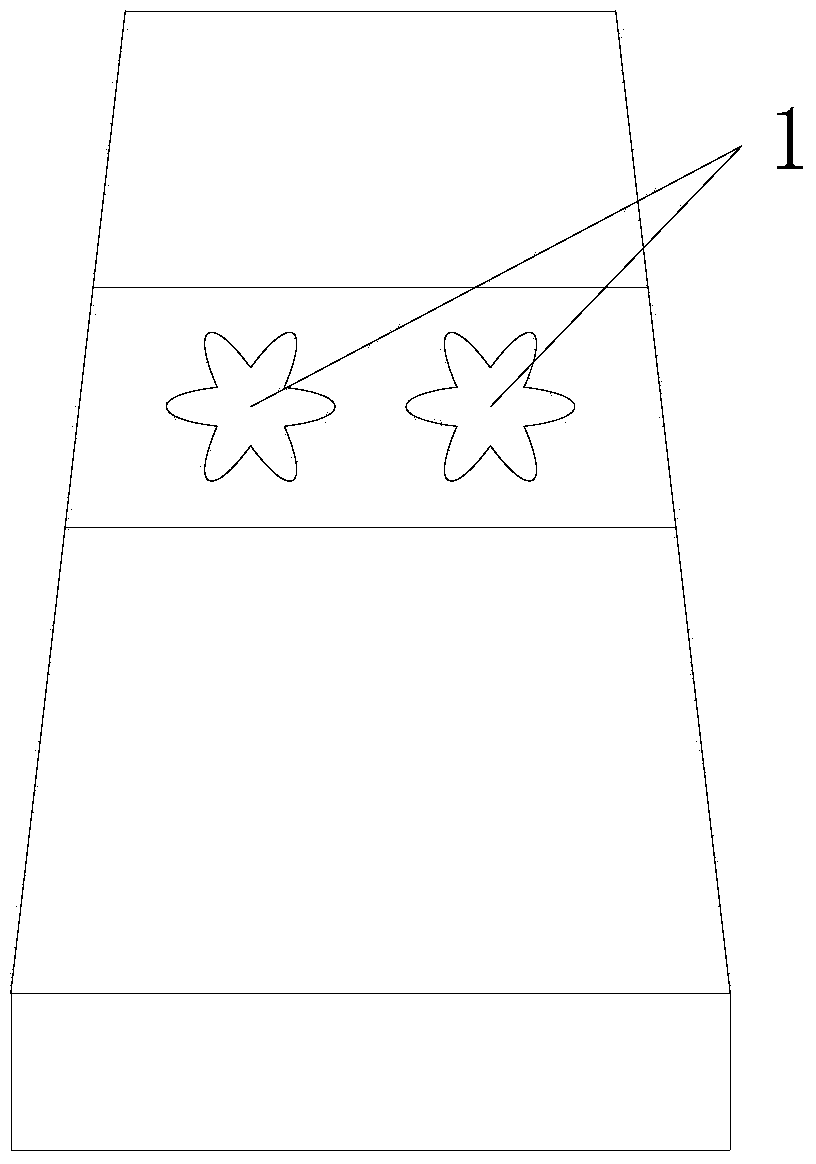

[0013] Embodiment 2: basically the same as Embodiment 1, the difference is: as attached figure 2 As shown, each positioning hole 1 is formed by a group of ellipses with the same center, and is opened radially from the center point, providing adjustment space in multiple directions for the position adjustment of the test base plate. A group of each positioning hole 1 The ovals are the same size.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More