System and method for executing scan test

一种扫描测试、扫描链的技术,应用在扫描测试和存储器内置自测试领域,能够解决产率损失等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The detailed description of the drawings is intended as a description of presently preferred embodiments of the invention and is not intended to represent the only forms in which the invention may be embodied. It is to be understood that the same or equivalent functionality may be achieved by different embodiments, which are intended to be encompassed within the spirit and scope of the invention.

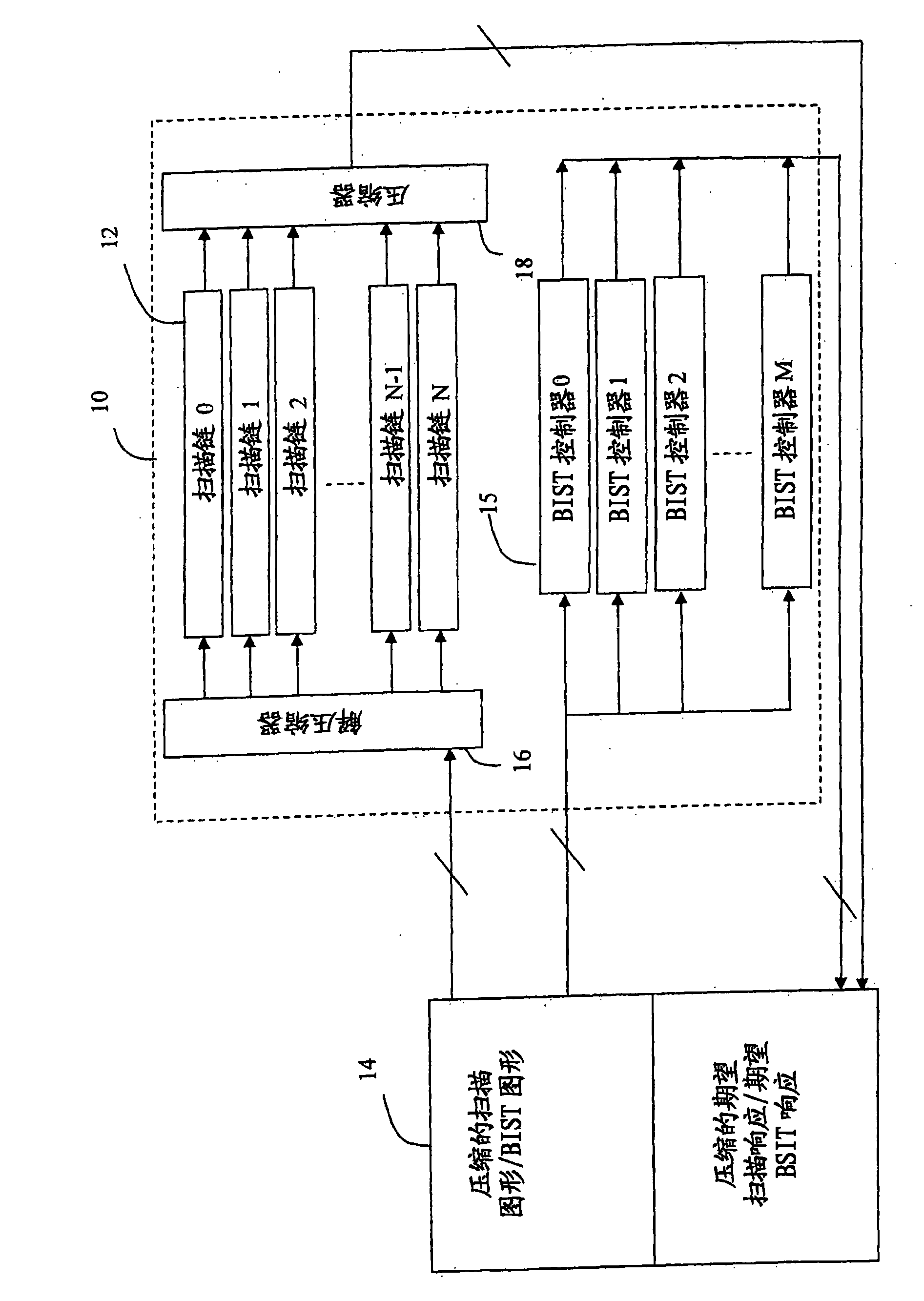

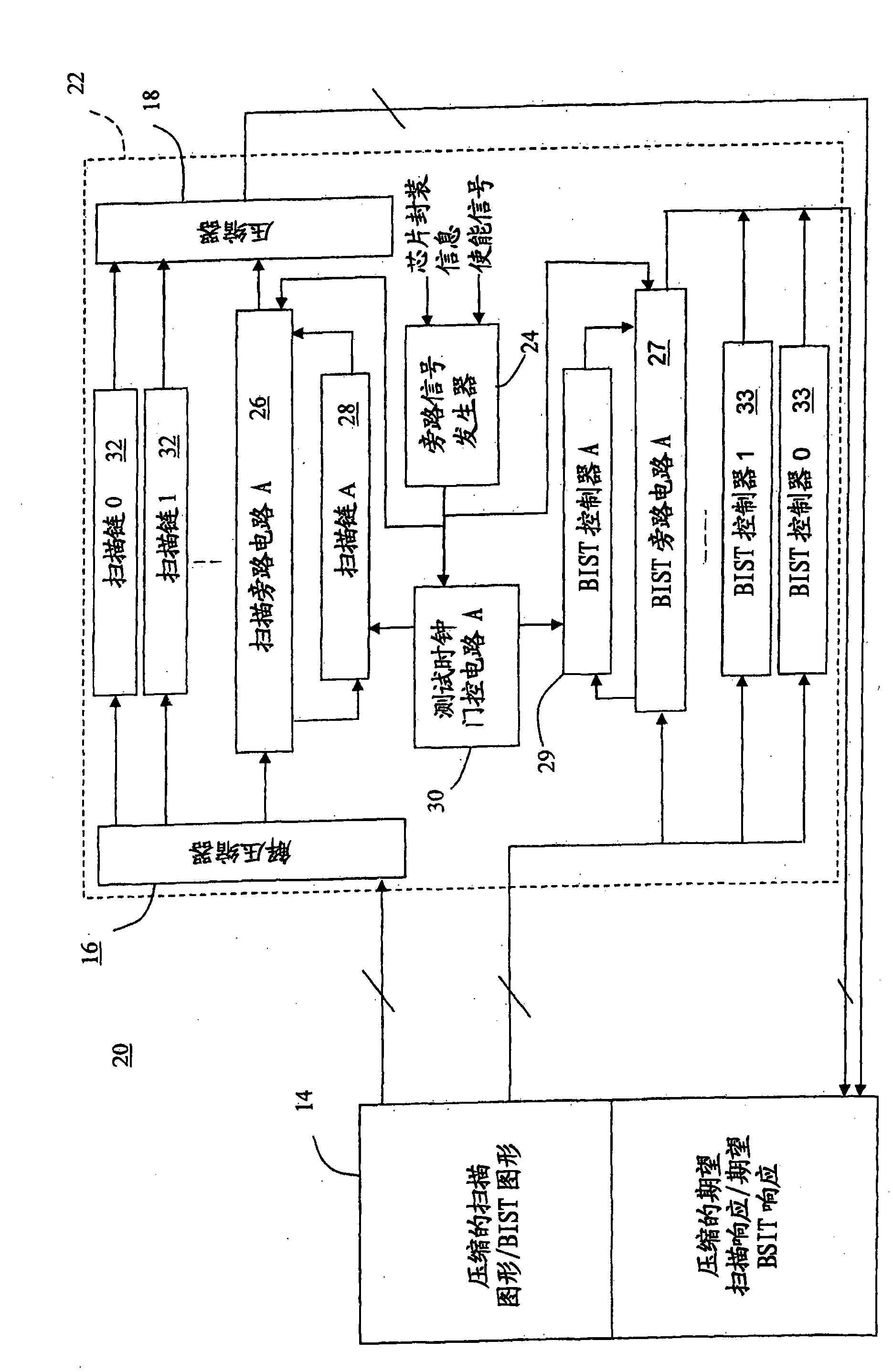

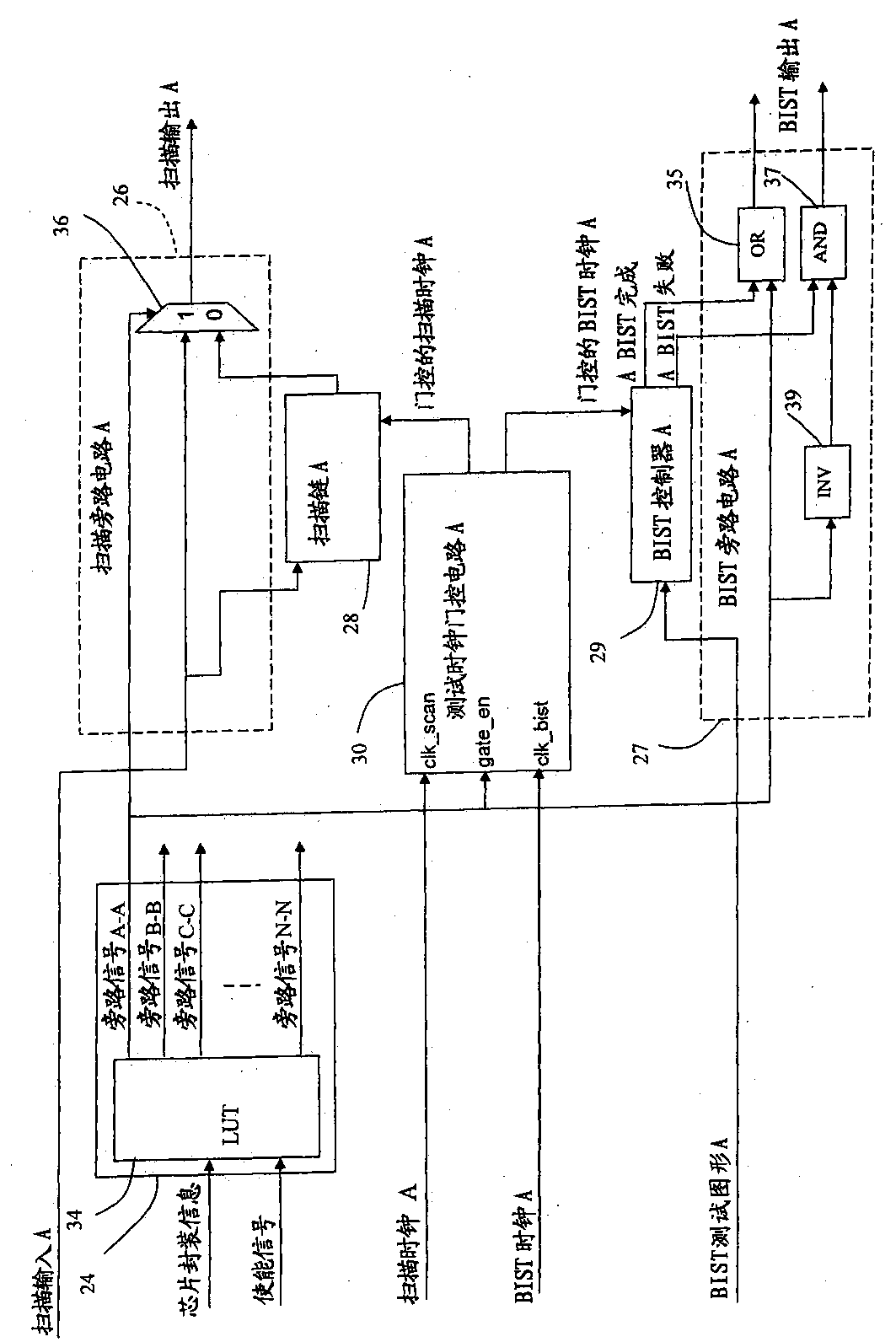

[0017] In one embodiment, the present invention provides a system for performing a scan test, the system including a bypass signal generator and a first scan bypass circuit. The bypass signal generator generates a first bypass signal based on chip package information. The first bypass signal indicates whether a first scan chain associated with a first non-generic IP block of the chip is to be bypassed during scan testing. The first scan bypass circuit bypasses the first scan chain in response to a first bypass signal.

[0018] In another embodiment, the present invention pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More