Delay line circuit, delay locked loop and tester system including the same

A technology of delay-locked loop and test system, applied in the fields of delay line circuit, delay-locked loop and test system, can solve the problem that the frequency of the output clock signal cannot be changed, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

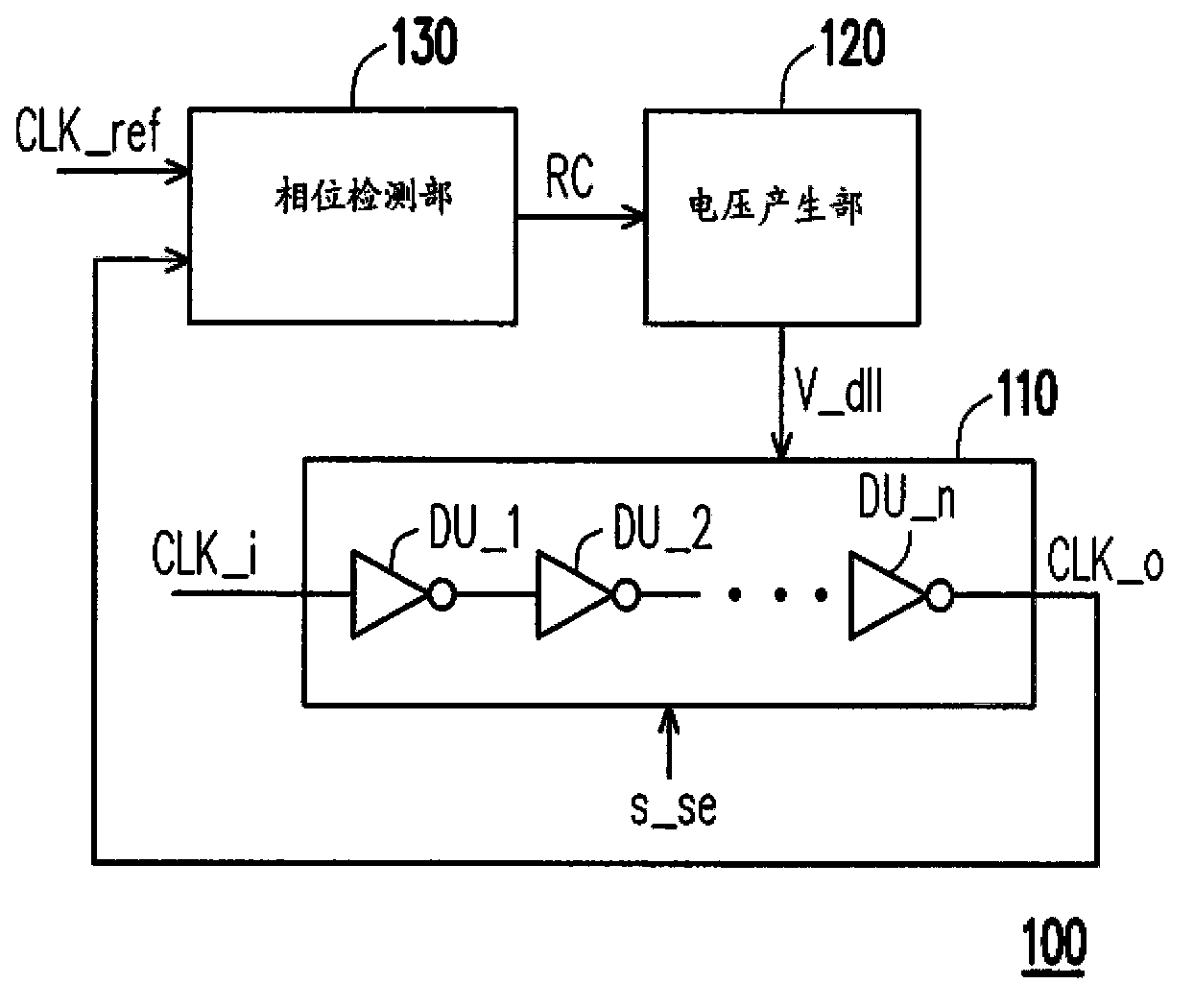

[0056] figure 1 It is a delay locked loop shown according to an embodiment of the present invention. Please refer to figure 1 , in this embodiment, the delay locked loop 100 includes a delay line circuit 110 , a voltage generating unit 120 and a phase detecting unit 130 . The delay line circuit 110 receives an input clock signal CLK_i and an internal feedback clock signal, and delays one of the input clock signal CLK_i and the feedback clock signal to generate an output clock signal CLK_o. Wherein, the delay line circuit 110 includes a plurality of delay units DU_1 -DU_n connected in series. Based on the selection signal s_se, a certain number of delay units delay one of the input clock signal CLK_i and the feedback clock signal to change the frequency CLK_o of the output clock signal, where n is an integer.

[0057] The voltage generator 120 is coupled to the delay line circuit 110 and provides the control voltage V_dll to the delay line circuit 110 . The delay line circu...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap