Patents

Literature

355 results about "Mount used" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

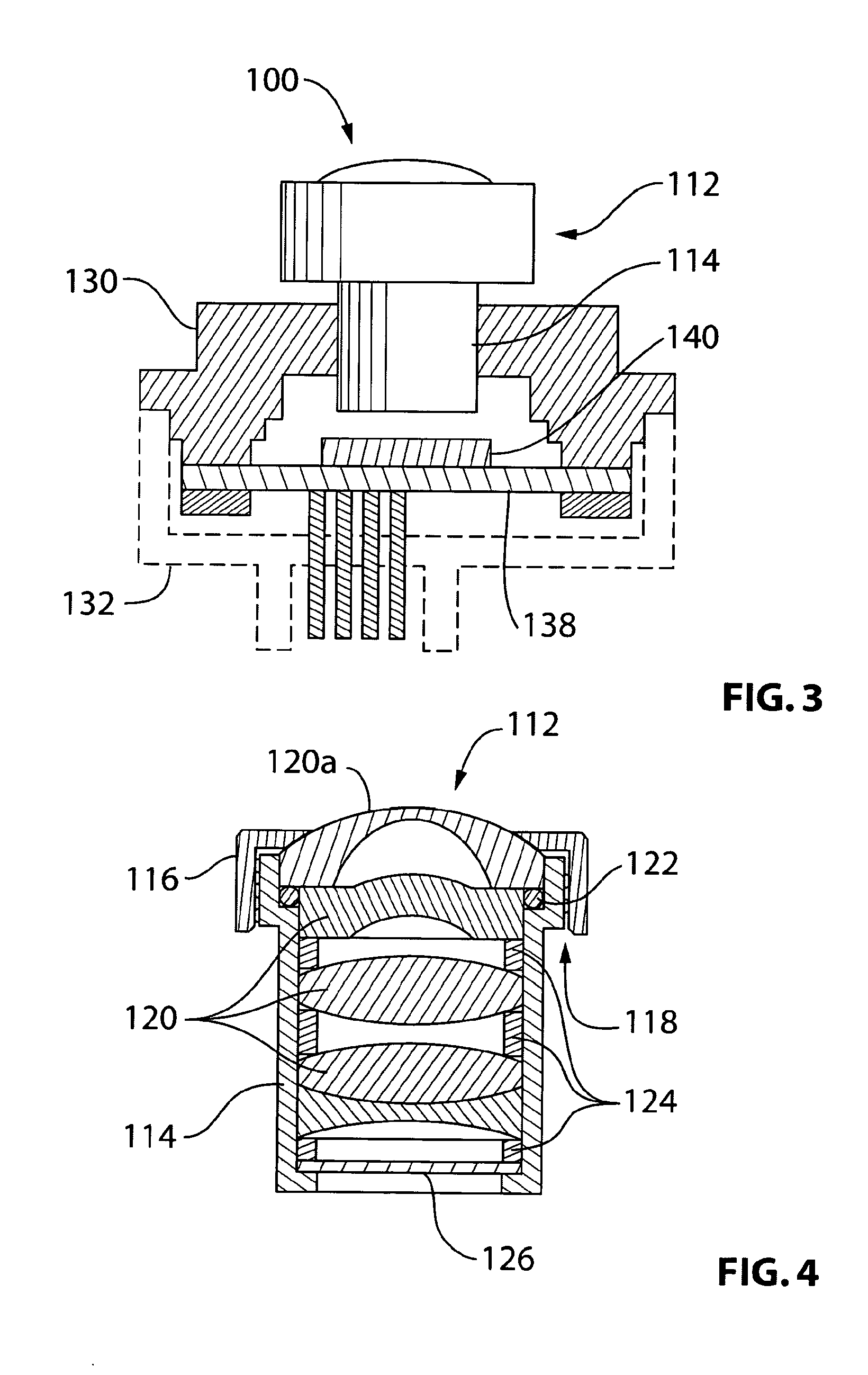

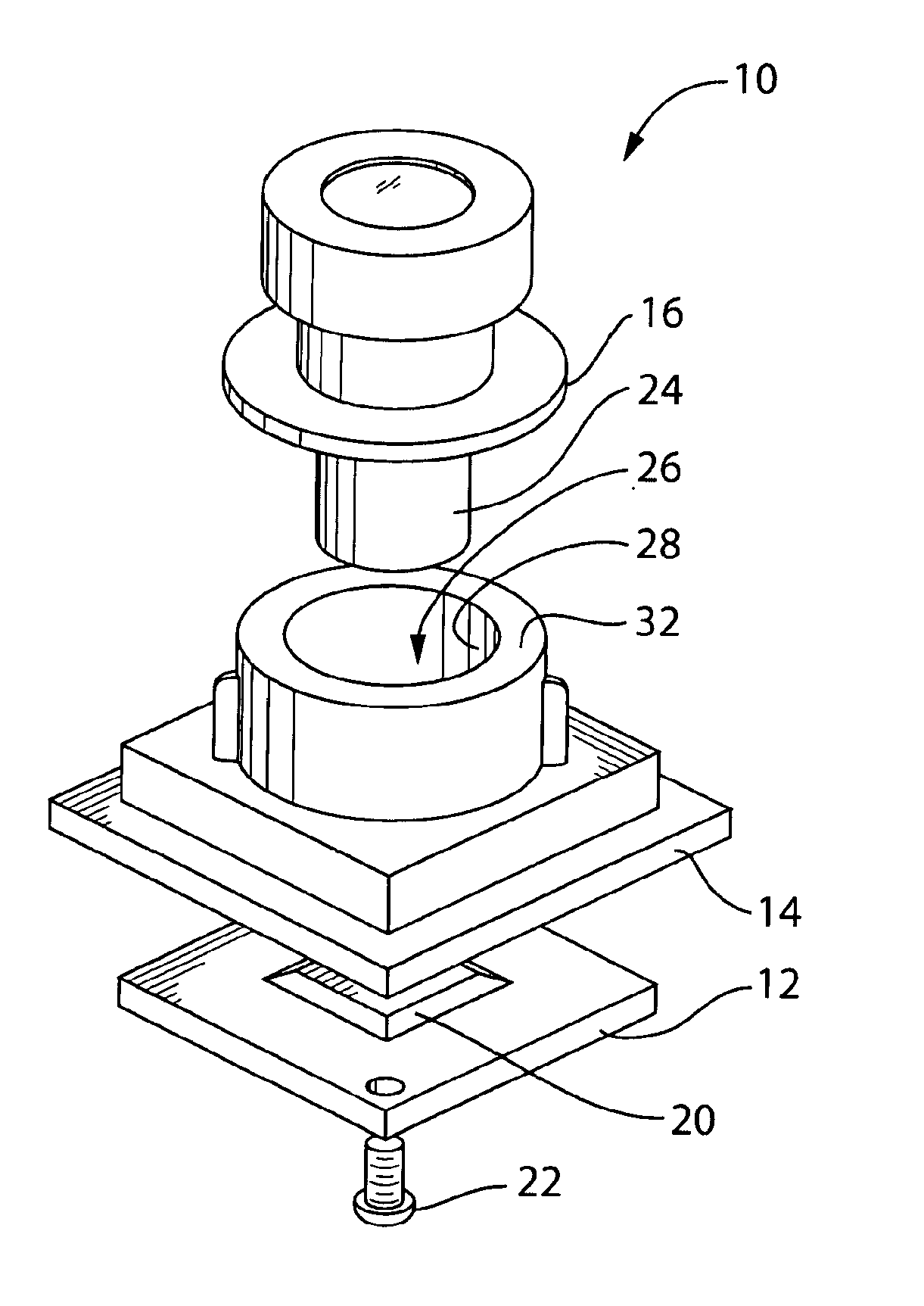

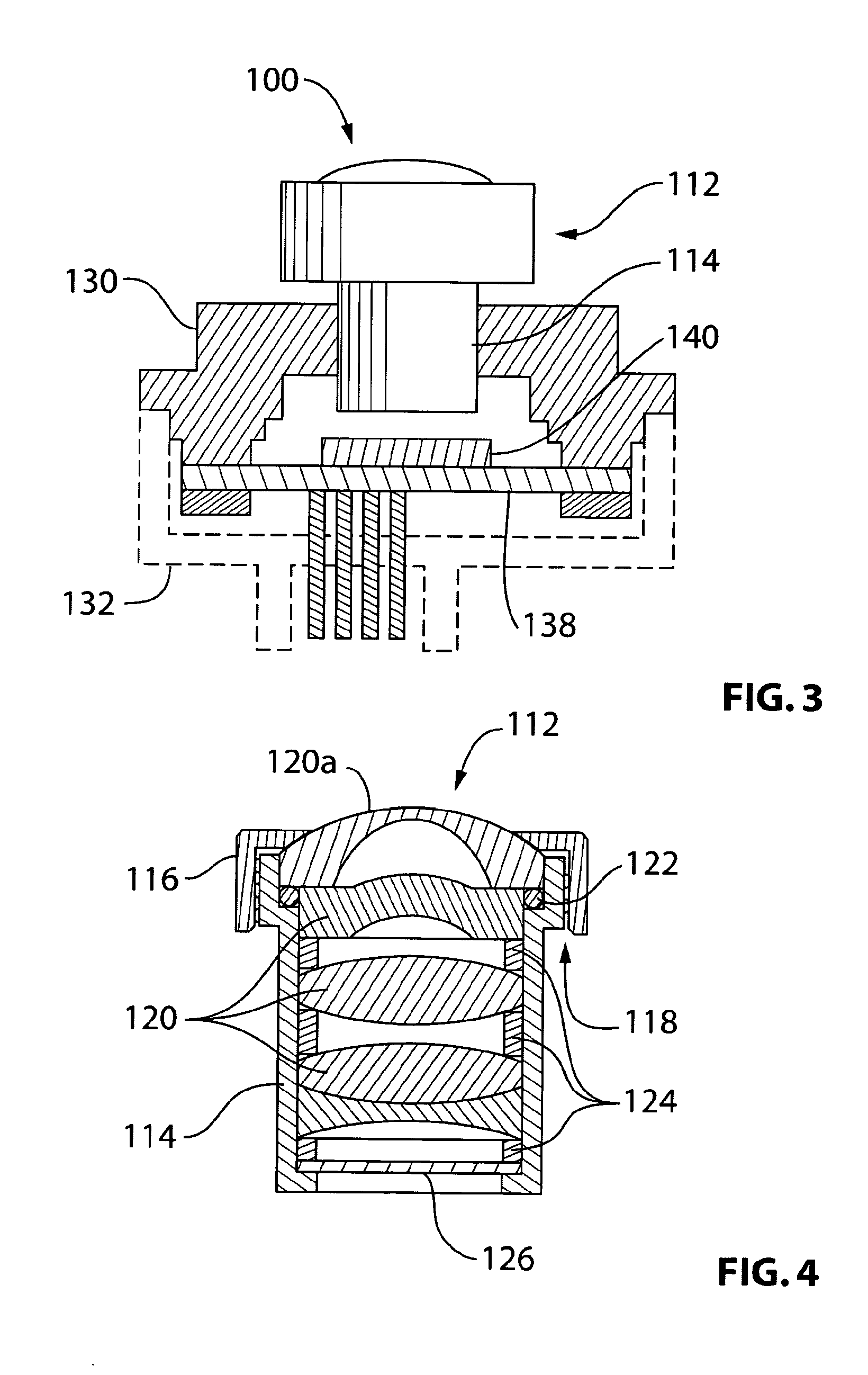

Vehicular camera and lens assembly

Low cost constructions of vehicular cameras employ various means for aligning and mounting the camera lens with respect to the imager. Such means include adhesive mounting using a UV curable adhesive, wherein the lens may be focused prior to cure of the adhesive. Other means include directly attaching the lens to the imager by adhesive; integrating the lens barrel and camera lens holder; dropping the lens barrel onto the surface of the imager; focusing the lens utilizing PCB mounting and focusing Screws; and focusing the lens by the relative positioning of camera front and back housings. Costs can also be contained by utilizing matching the resolution of the lens in conformance to human contrast sensitivity function, and by replacing optical chromatic aberration with digital chromatic aberration.

Owner:MAGNA ELECTRONICS INC

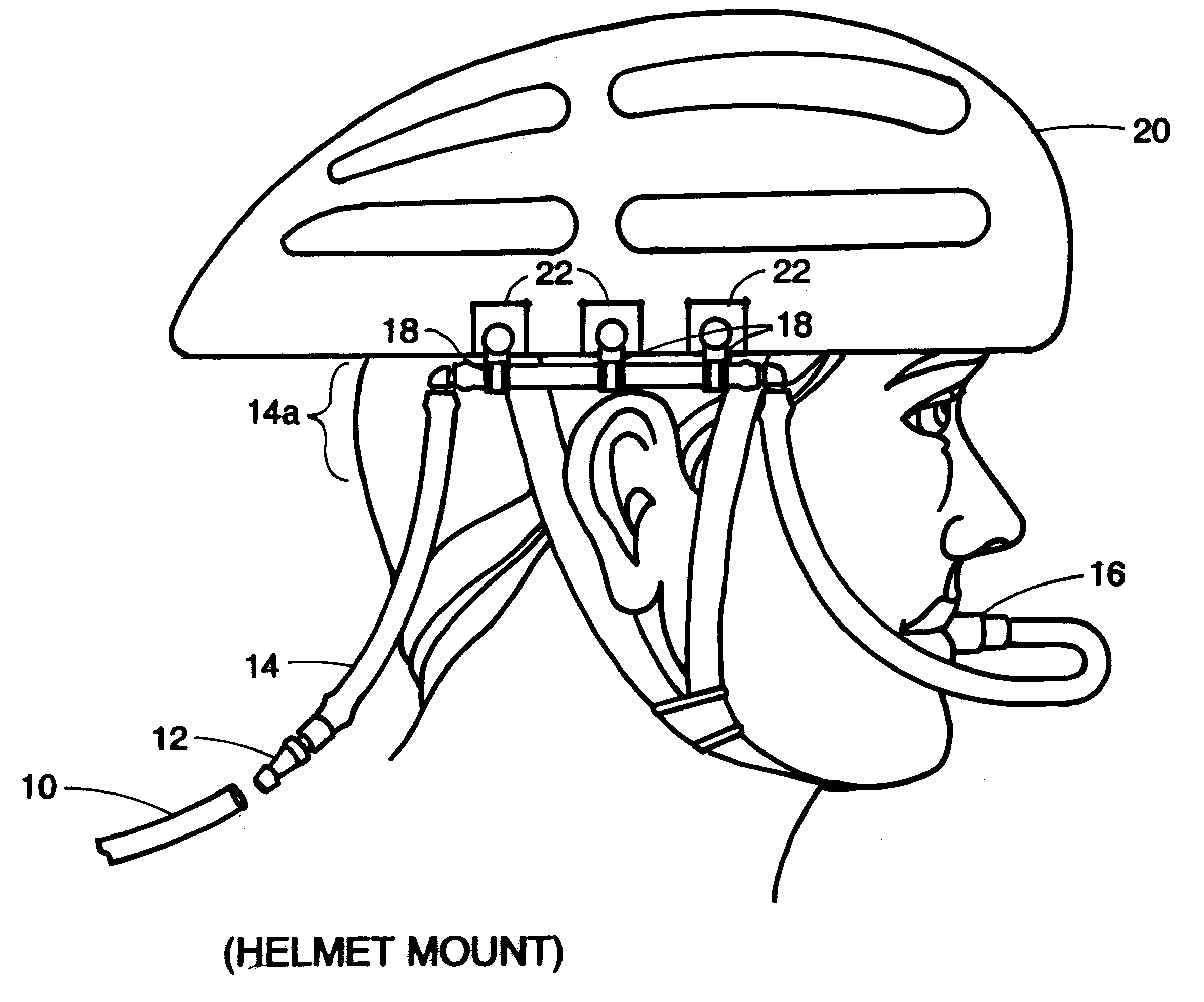

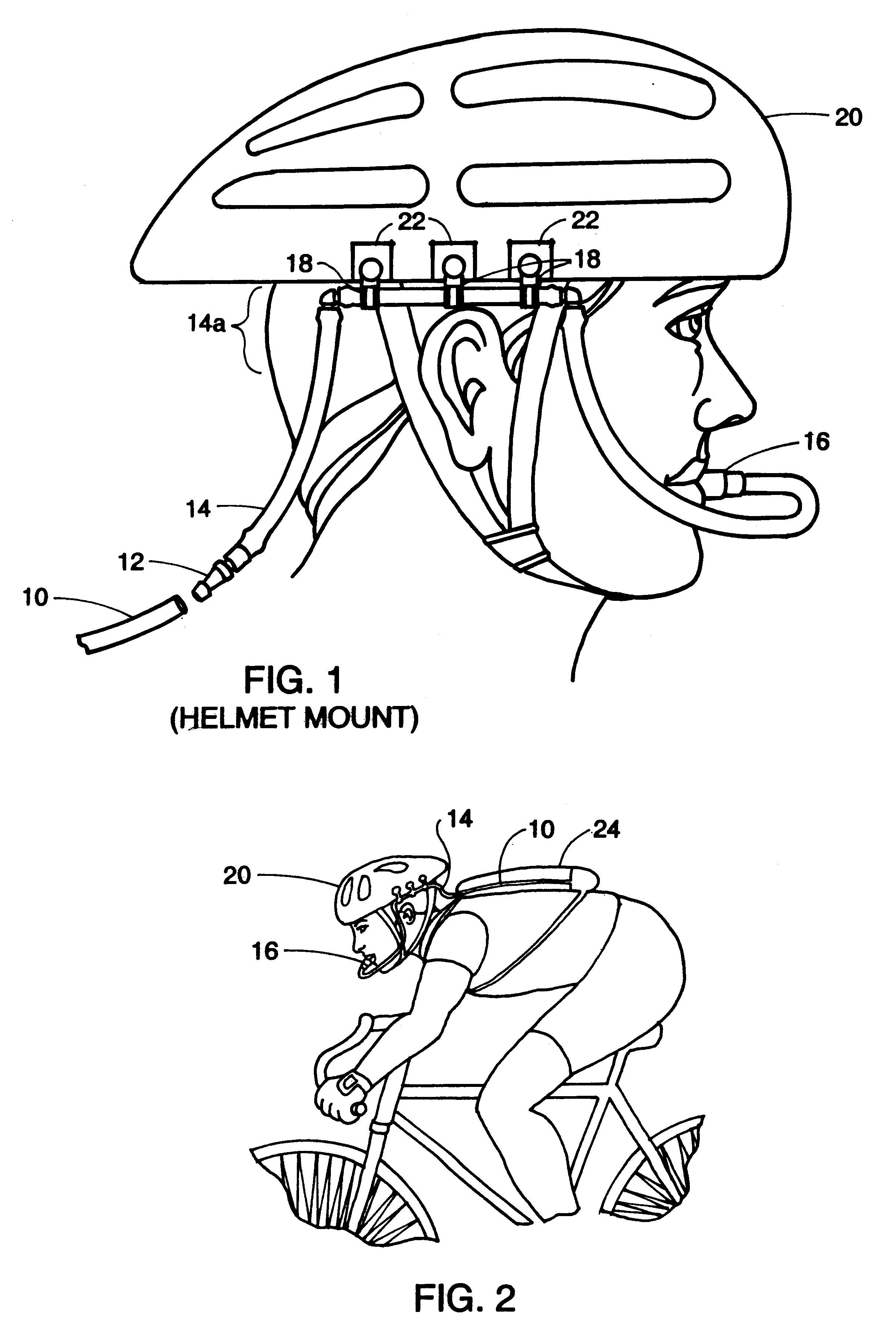

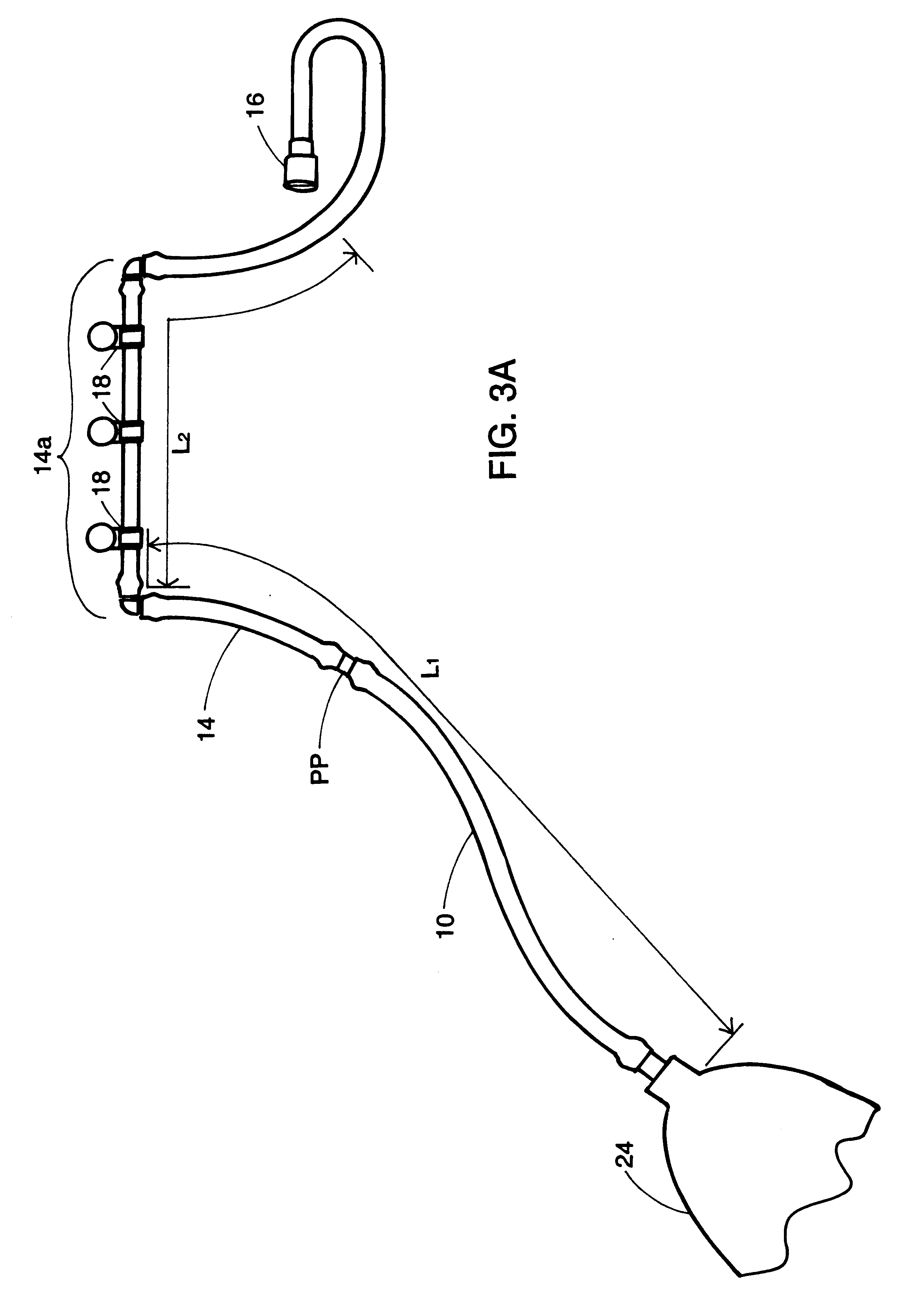

Hands free personal hydration delivery system

InactiveUS6283344B1Little suction effortReduce flow of fluidTravelling sacksTravelling carriersHigh elevationHands free

A hands-free personal hydration delivery system has a tubing assembly that has one end that detachably connects to a feed tube for a container of fluid worn on the back or torso of a user. The other end of the tubing assembly is coupled to a bite valve which is opened when manipulated by the user's mouth to allow fluid to be drawn by suction applied by the user, and is closed when not being manipulated so as to cut off fluid flow in an air-tight condition. An intermediate portion of the tubing assembly is mounted on the user's head or to the user's headgear at a position of higher elevation than the user's mouth. This allows fluid to be drawn to the elevated position and flow downward from there to the user's mouth by gravity feed. The fluid flow can then continue with little suction effort due to the gravity feed and siphoning effect of fluid from the container. The tubing can be mounted using retainer loops or other type of fasteners attached to a helmet, sports cap, head band bracket, headphone bracket, headband, or an earpiece worn by the user. The hydration delivery system is especially useful for bicycling, canoeing, mountain biking, kayaking, canoe paddling, and rowing environments.

Owner:BRADLEY TODD H

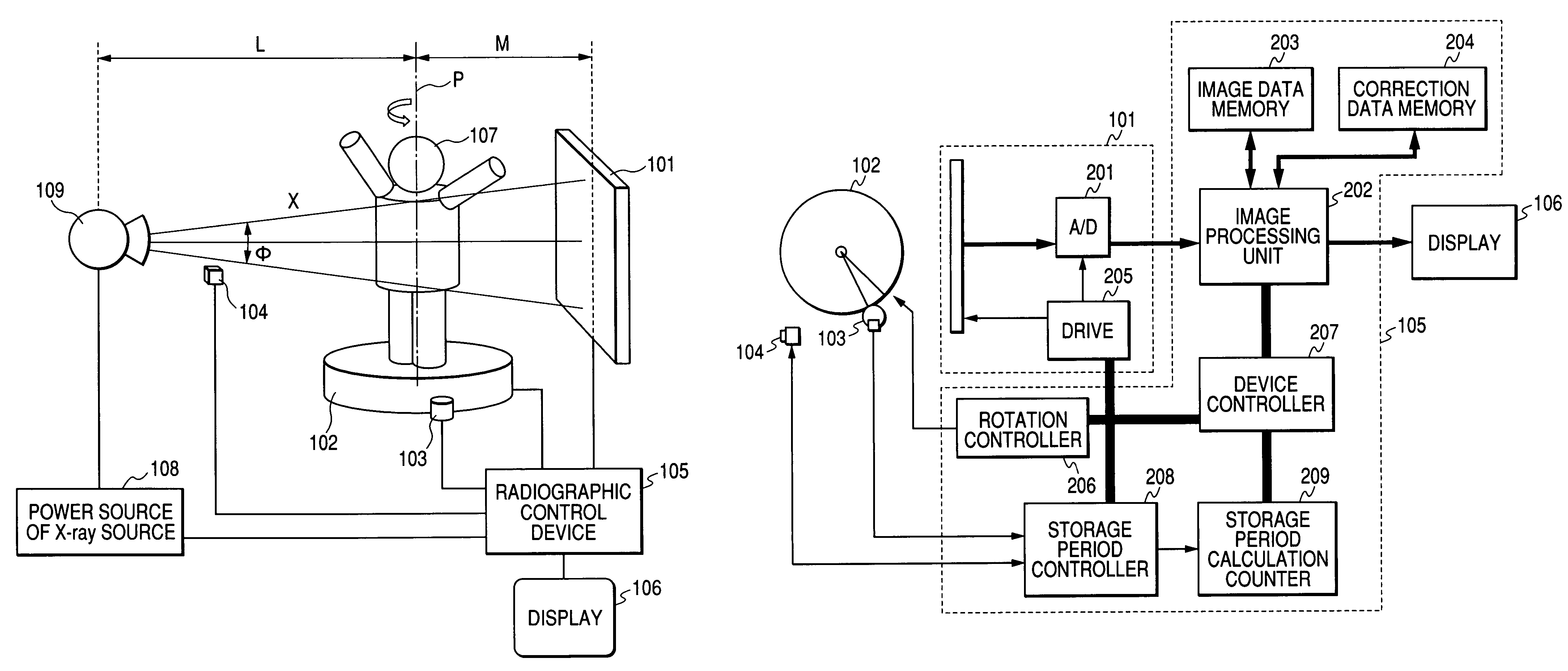

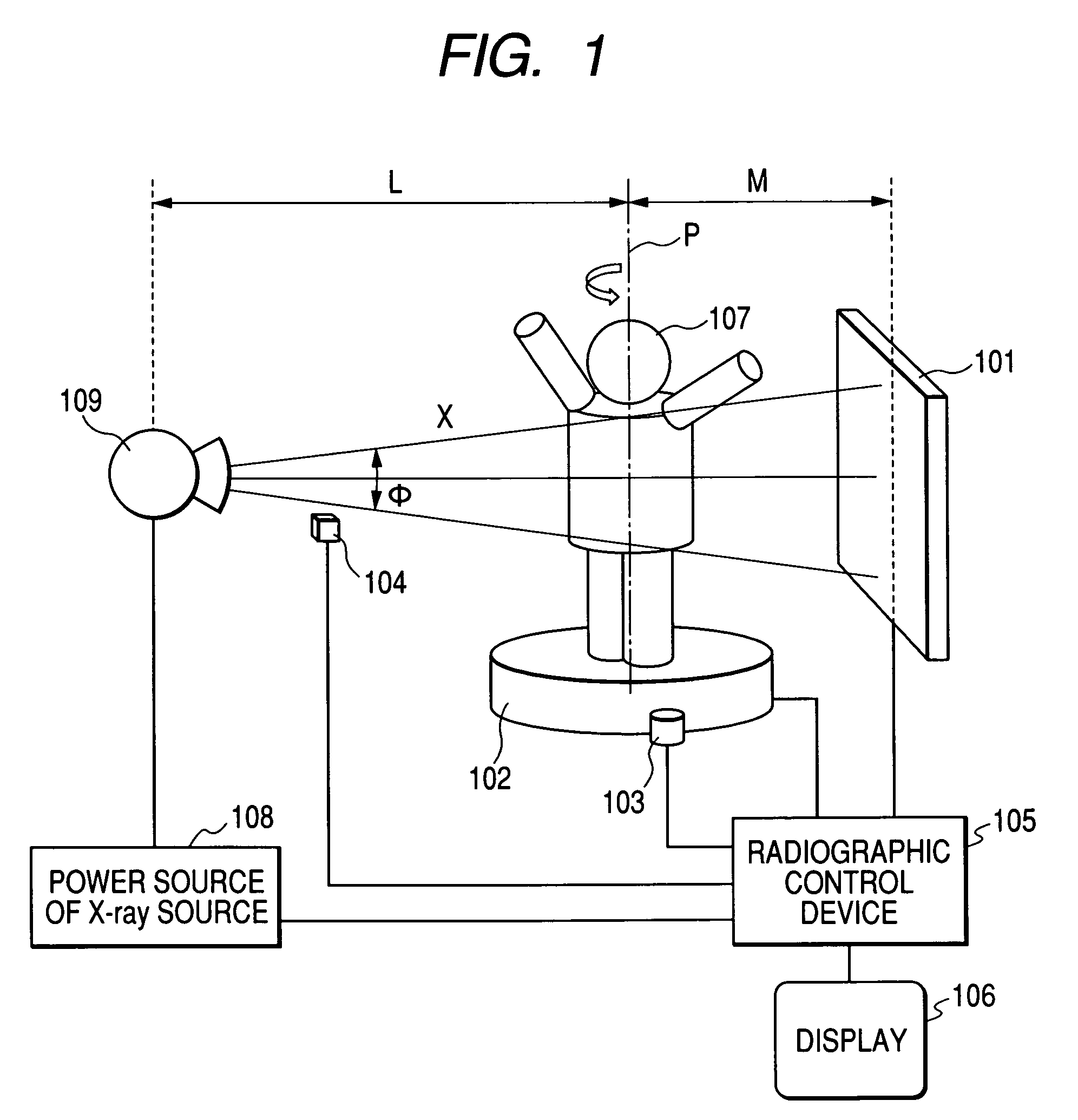

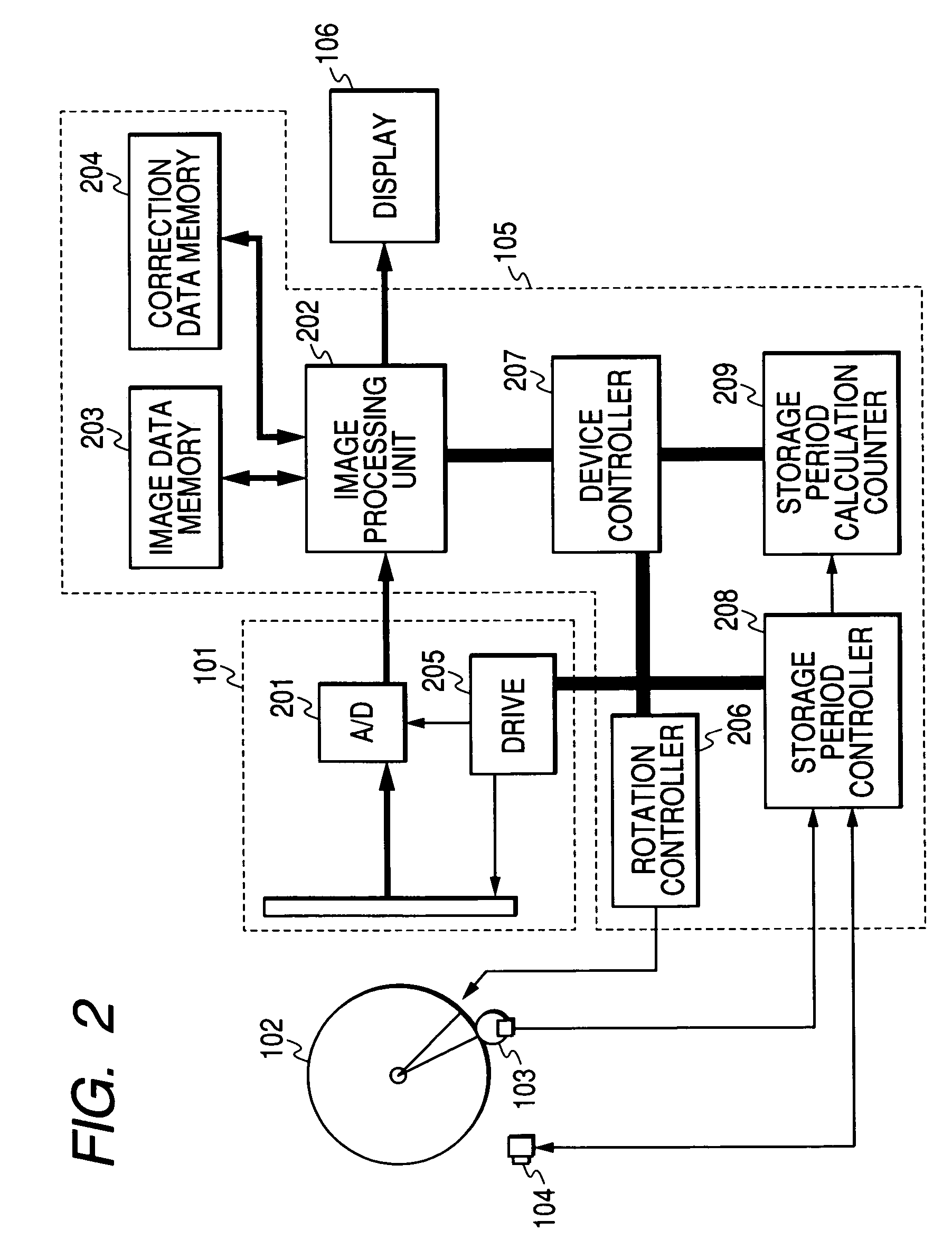

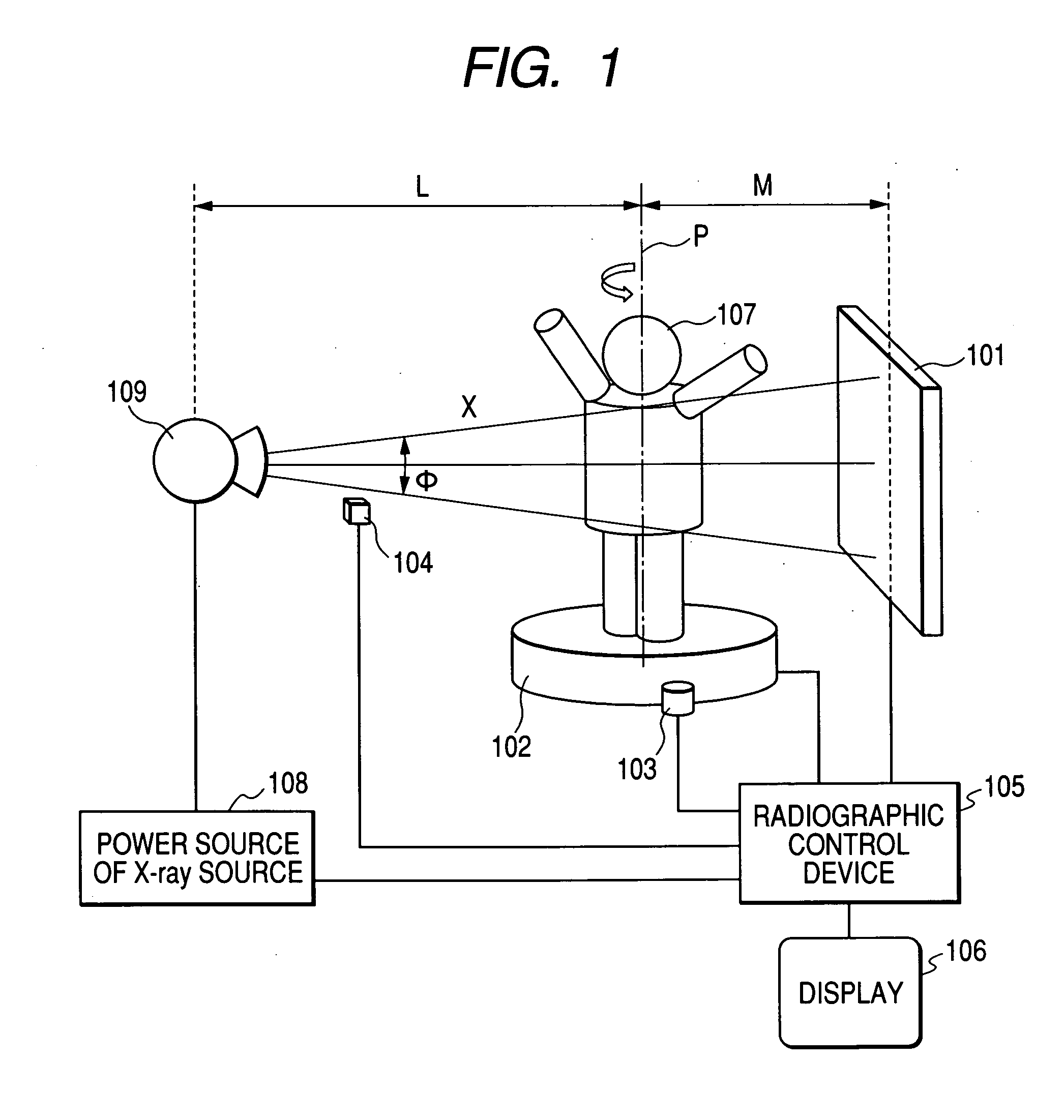

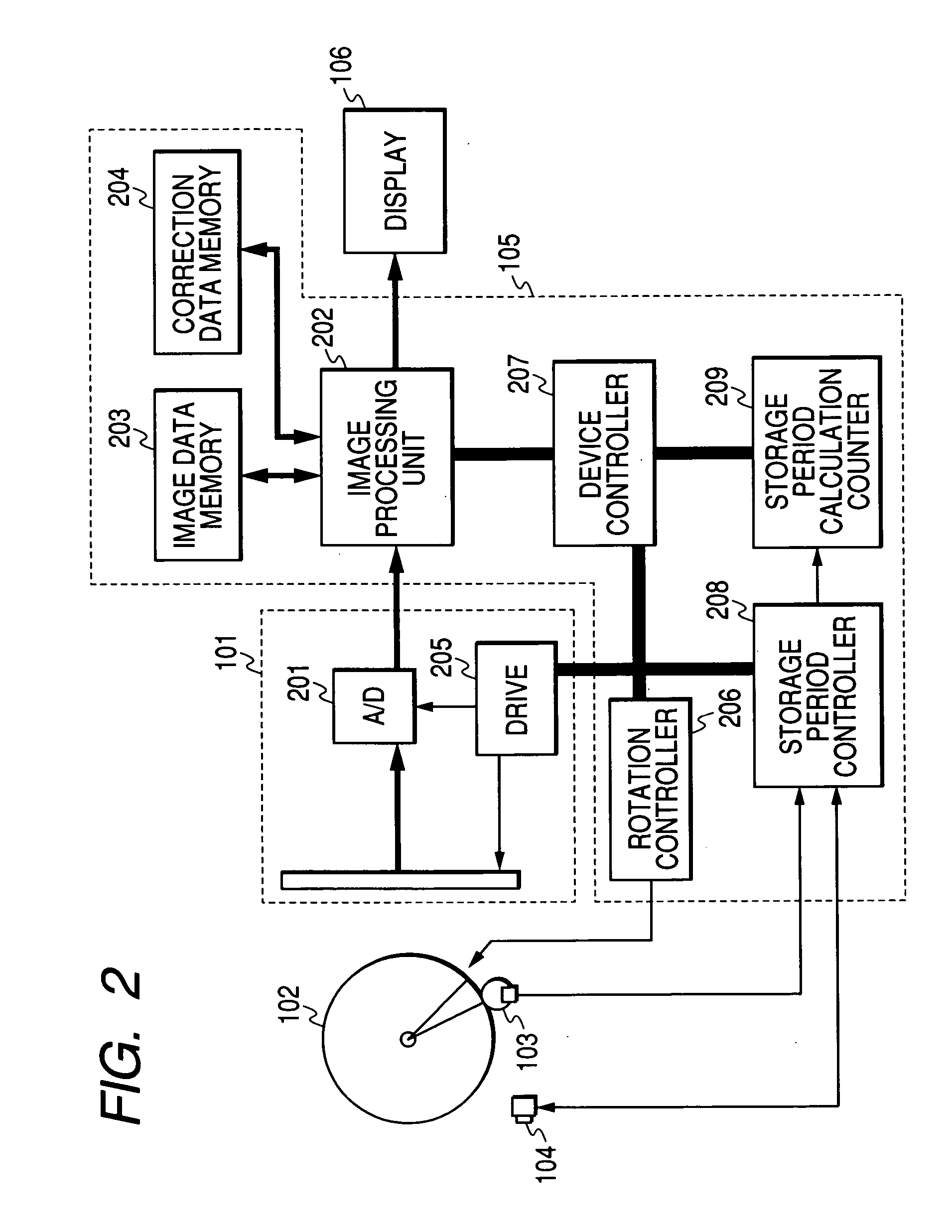

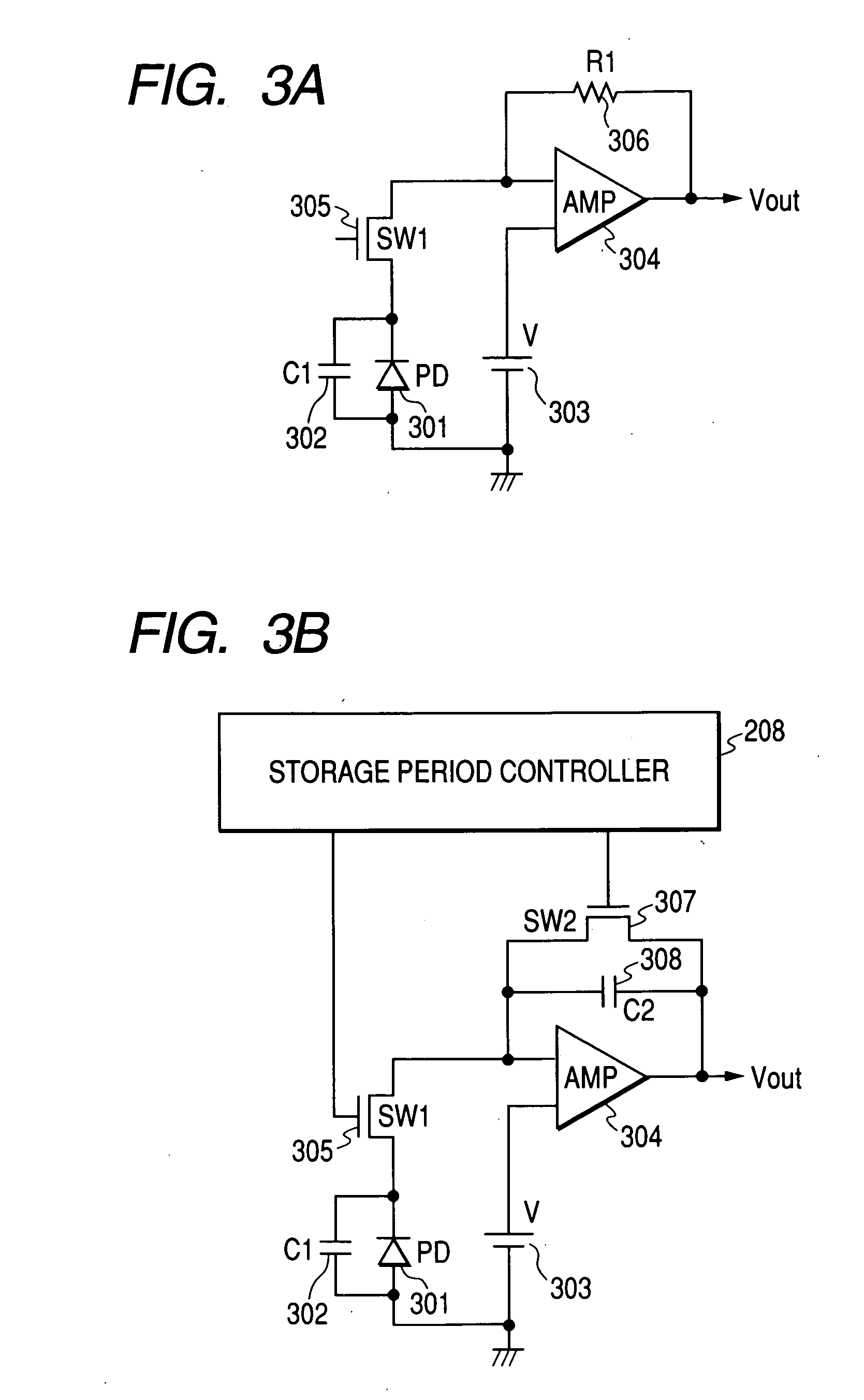

Radiation CT radiographing device, radiation CT radiographing system, and radiation CT radiographing method using the same

InactiveUS7310404B2Fast processingLow costMaterial analysis using wave/particle radiationRadiation/particle handlingControl signalSignal generator

An object rotating type cone beam radiation CT radiographing device in which a high speed and high sensitivity are obtained with low costs is provided. Thus, a radiation CT device of high performance for vehicle-mounted use and group medical examination can be provided at low costs. In the object rotating type cone beam radiation CT radiographing device, a rotational angle of an object is detected, a signal storage period of a batch-exposure type radiation image sensor panel is controlled on the basis of the rotational angle signal, and a signal storage period of a signal storage type reference signal generator is controlled. There is provided a radiation CT radiographing device in which the object can be photographed at arbitrary resolution during the photographing, a fluctuation of a radiation source during the photographing can be detected without using a special detector and corrected in accordance with its detection amount.

Owner:CANON KK

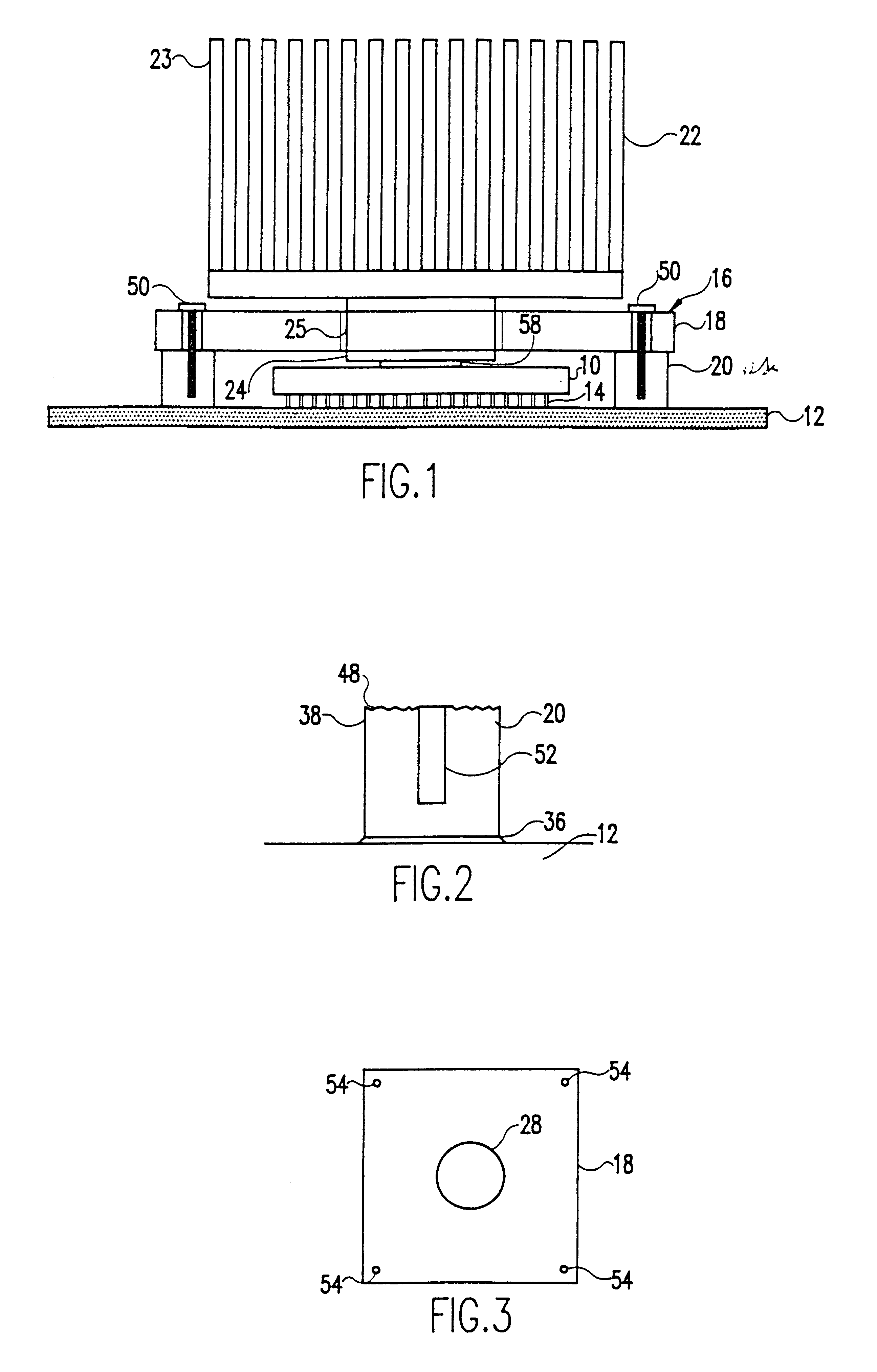

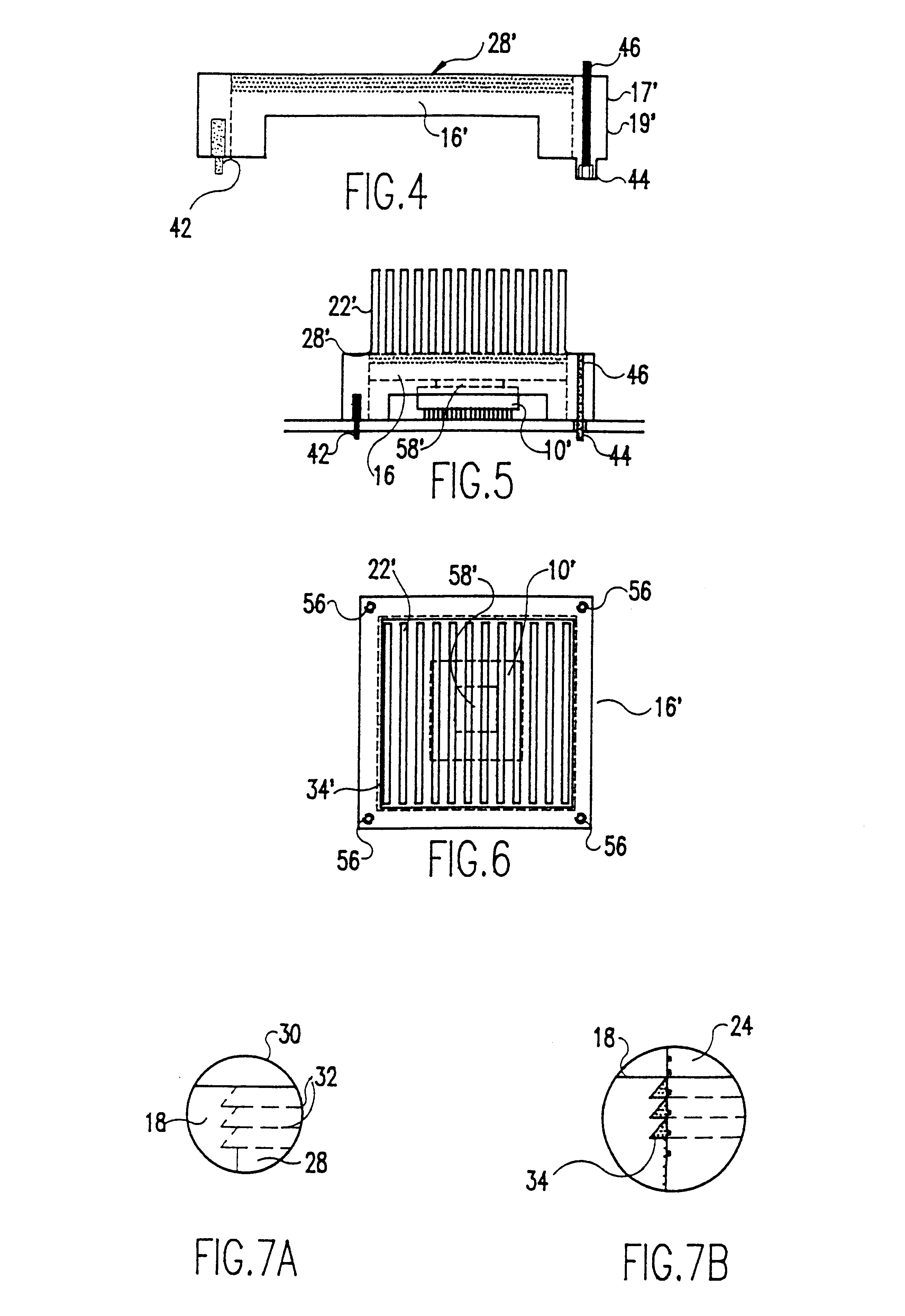

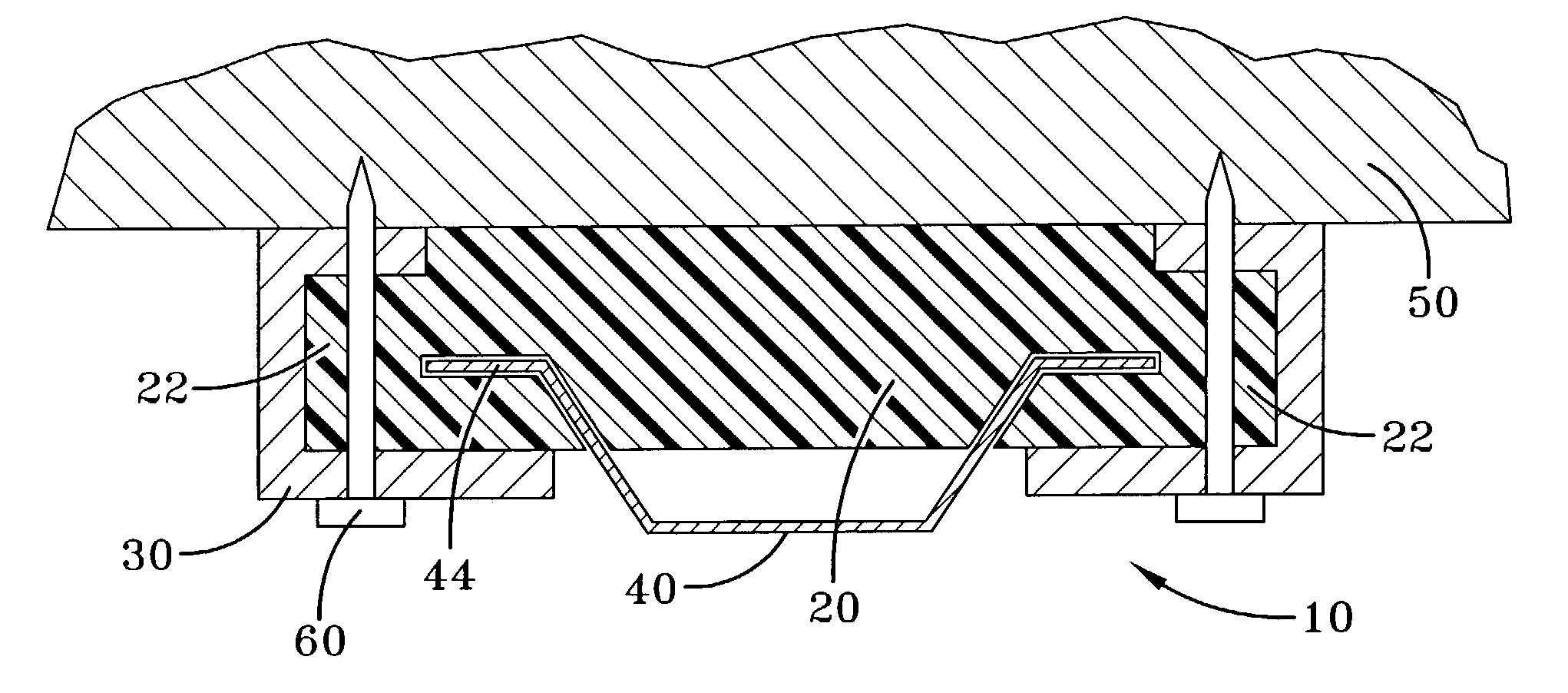

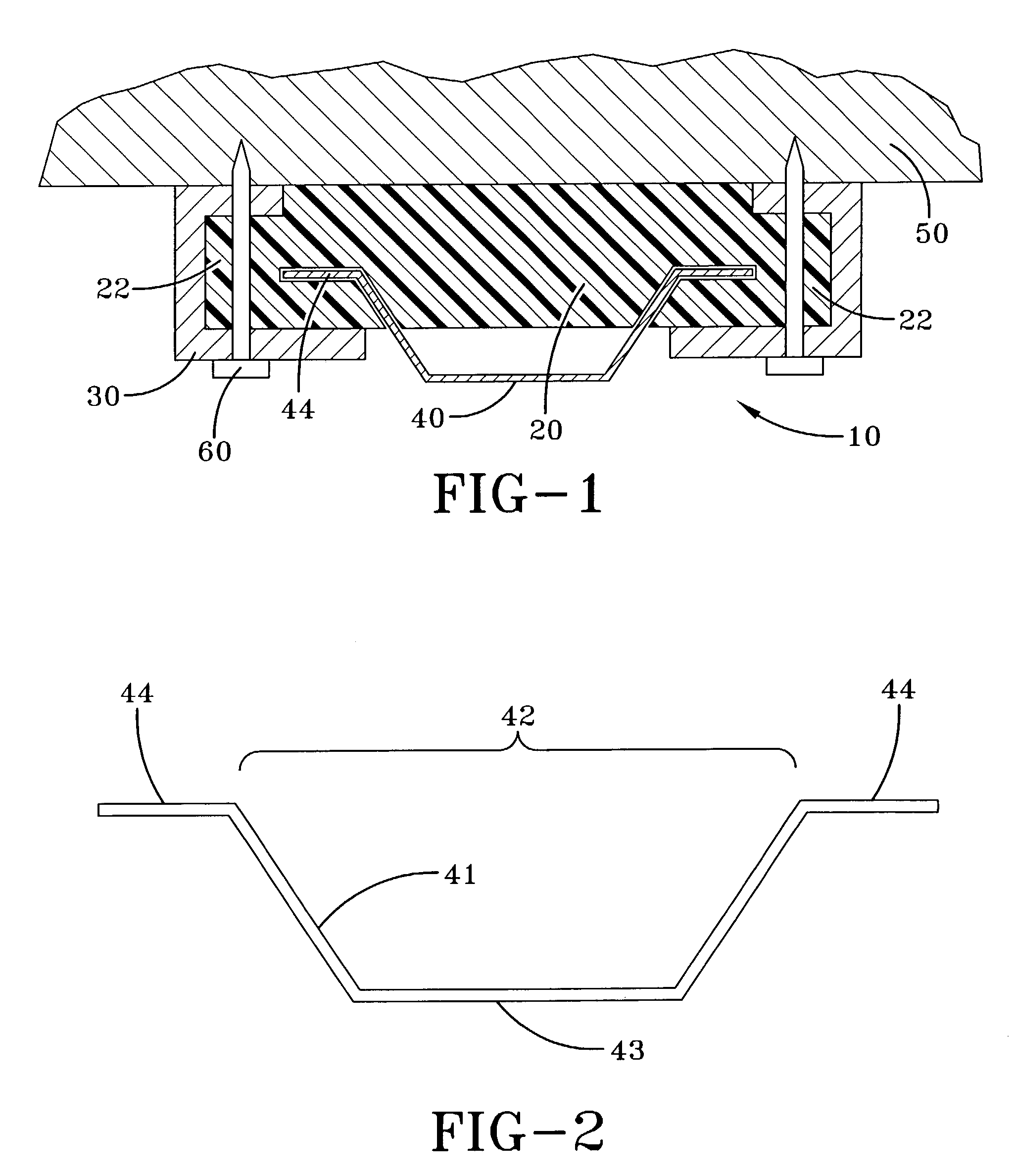

Zero force heat sink

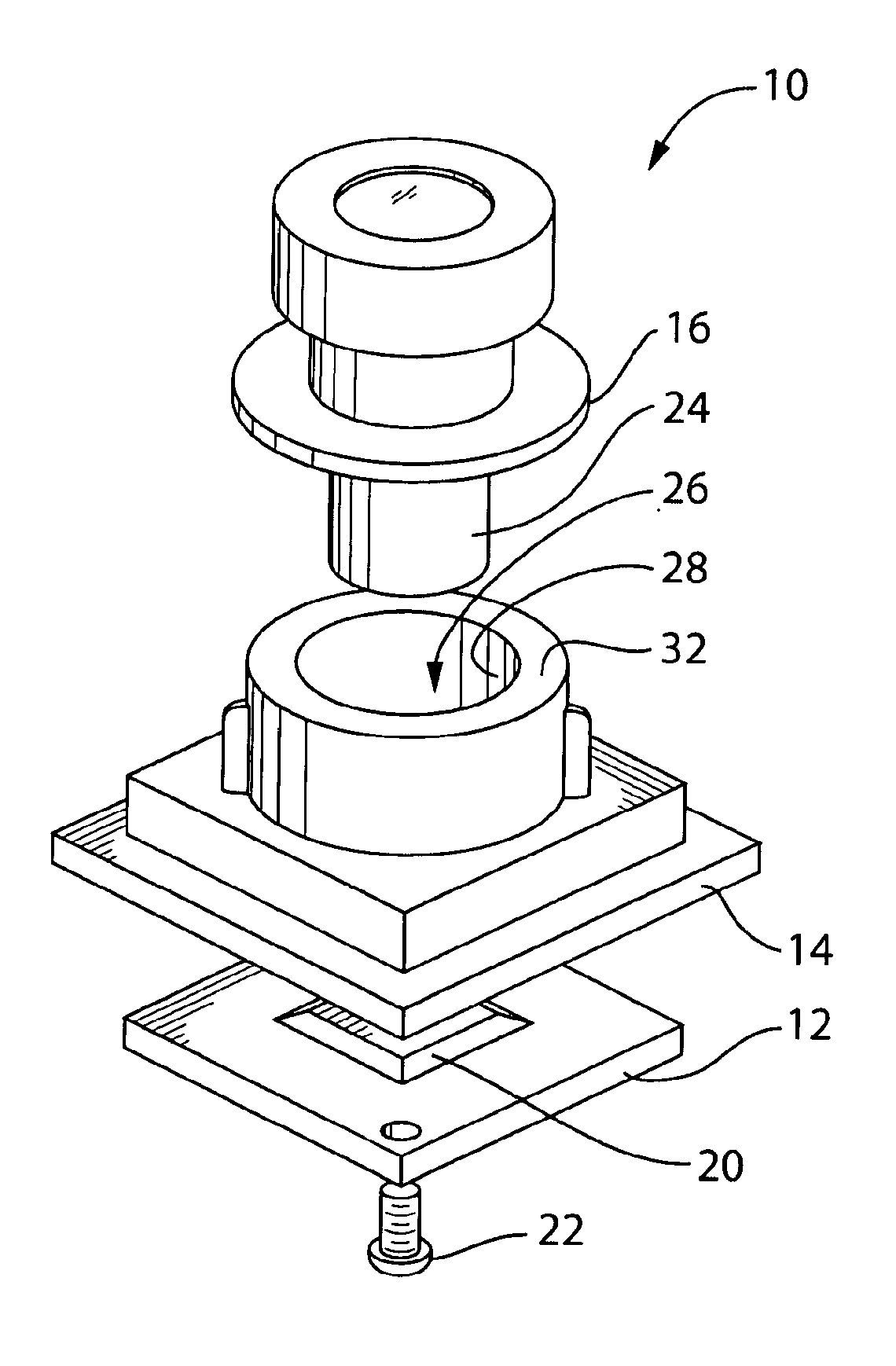

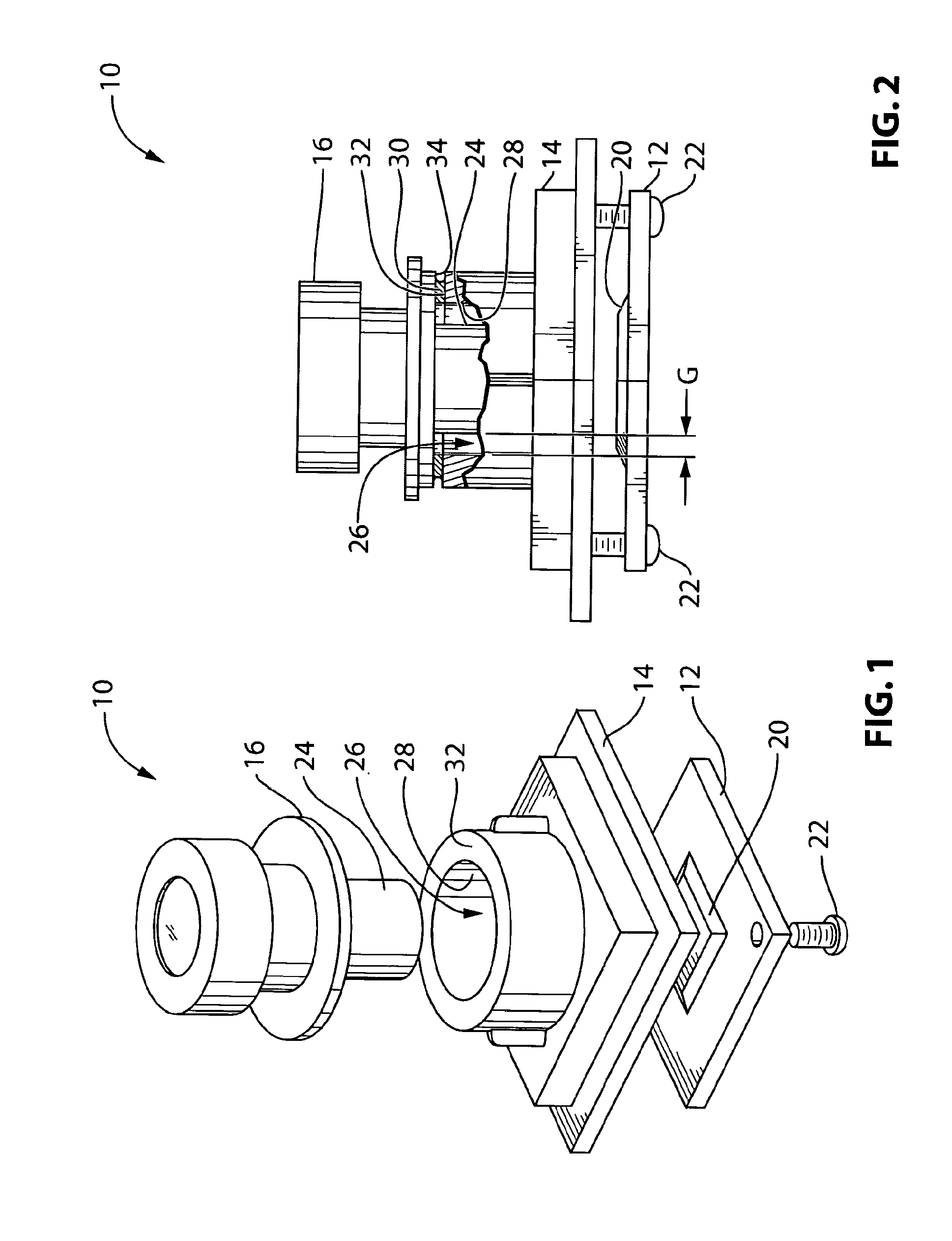

InactiveUS6212070B1Semiconductor/solid-state device detailsSolid-state devicesSurface mountingSolder ball

A heat sink in a heat transfer relationship with a substrate such as an integrated chip, chip carrier, or other electronic package. The heat sink is connected to a frame which is connected to a printed circuit board or other suitable support on which the substrate is positioned. The heat sink, which extends through an aperture in the frame is coupled to a surface of the substrate. The heat sink is mechanically decoupled from the substrate. Large heat sinks may be thermally connected to surface mount substrates mounted using technologies such as ceramic ball or column grid arrays, plastic ball or column grid arrays, or solder balls or columns. The heat sink is attached coaxially through the aperture to the substrate. After assembly and lead / tin or other metallic surface mount interconnects are relaxed such that the substrate and is completely supported by the frame and the heat sink imparts zero or nearly zero downward force. Because the heat sink moves freely within the aperture during assembly, the heat sink package is useful for a variety of different substrates. Preferably, the frame is a plate and a plurality of studs. The plate material are selected to match the thermal expansion of the underlying support, and the stud material matched the thermal expansion of the substrate. Thus, the frame construction allows matching expansion and contraction of the assembly to the underlying substrate and support.

Owner:IBM CORP

Vehicular camera and lens assembly

Low cost constructions of vehicular cameras employ various means for aligning and mounting the camera lens with respect to the imager. Such means include adhesive mounting using a UV curable adhesive, wherein the lens may be focused prior to cure of the adhesive. Other means include directly attaching the lens to the imager by adhesive; integrating the lens barrel and camera lens holder; dropping the lens barrel onto the surface of the imager; focusing the lens utilizing PCB mounting and focusing Screws; and focusing the lens by the relative positioning of camera front and back housings. Costs can also be contained by utilizing matching the resolution of the lens in conformance to human contrast sensitivity function, and by replacing optical chromatic aberration with digital chromatic aberration.

Owner:MAGNA ELECTRONICS

Multi-link antenna array that conforms to cellular leasing agreements for only one attachment fee

InactiveUS7394439B1Antenna supports/mountingsIndividually energised antenna arraysMulti linkMultiple point

A system and method for mounting a plurality of antenna elements onto a cell tower is disclosed. A plurality of antennas are mounted onto a mounting system. The mounting system is configured to attach to a cellular antenna mount using the same physical mounting system as the cellular antenna elements. The plurality of antennas provide multiple point-to-point links that may be used for wireless backhaul links or other applications.

Owner:SPRINT CORPORATION

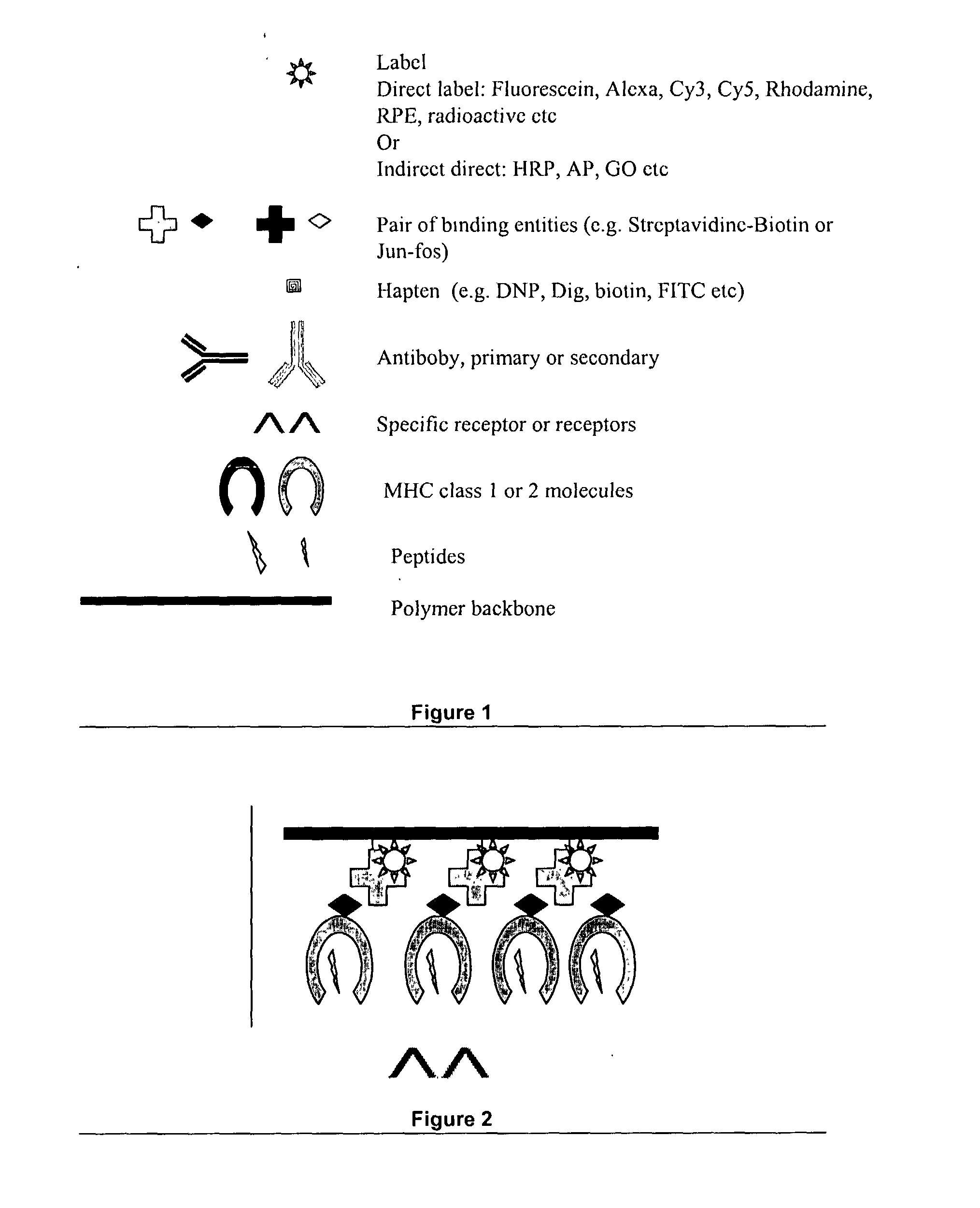

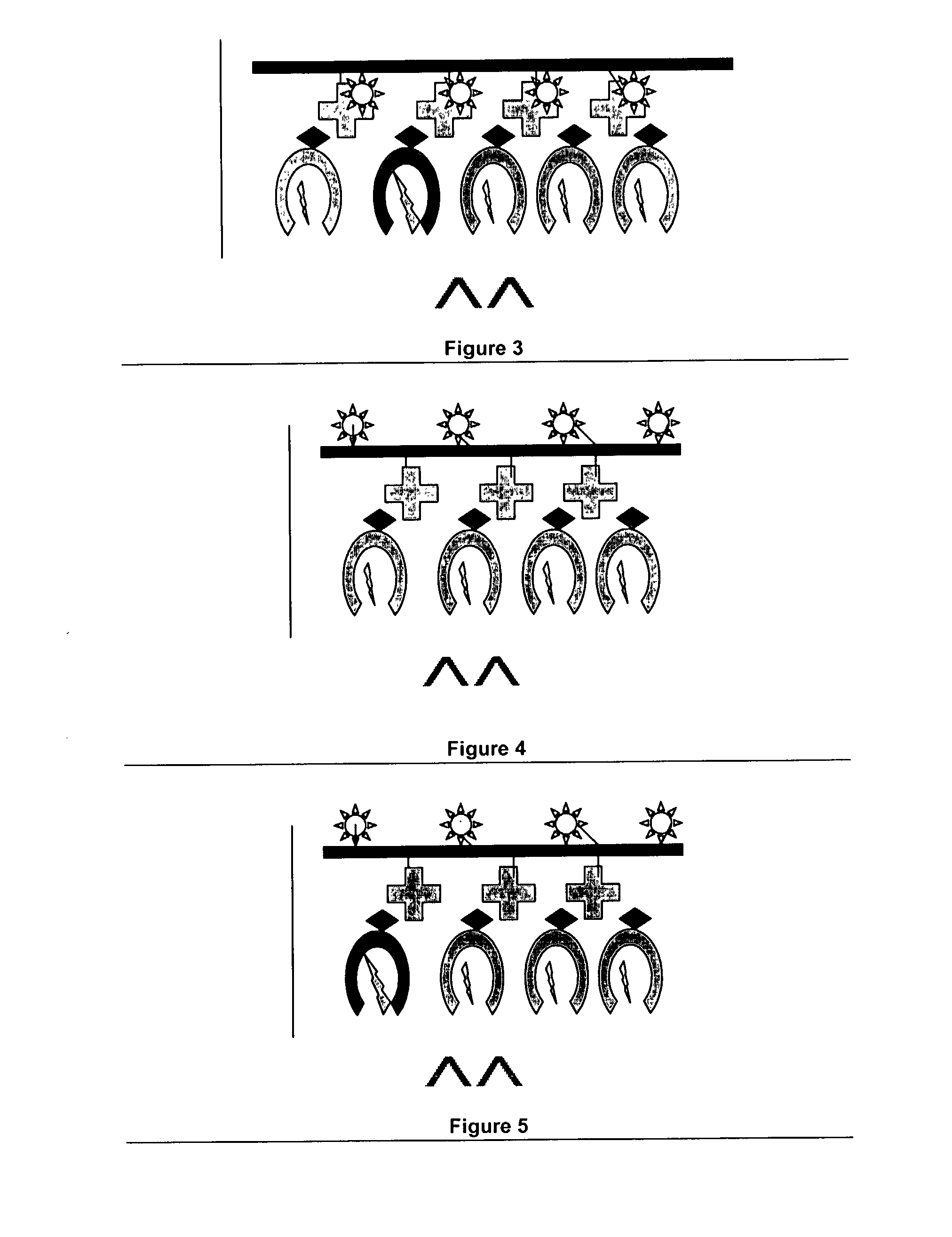

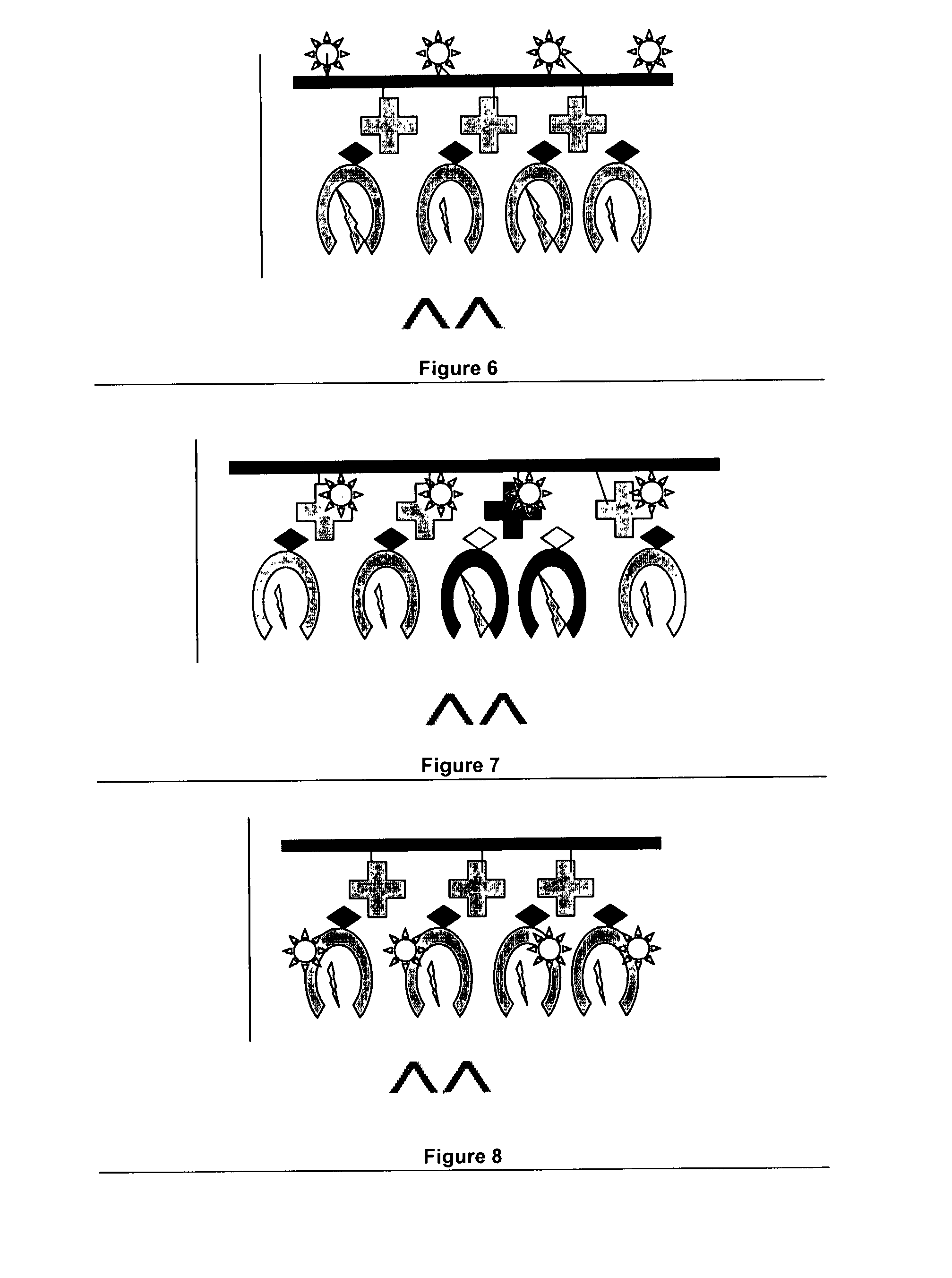

Novel MHC molecule constructs, and methods of employing these constructs for diagnosis and therapy, and uses of MHC molecules

InactiveUS20150329617A1Tall in constructionHigh expectationSugar derivativesPeptide/protein ingredientsBiochemistryAvidity

Novel compounds carrying ligands capable of ligating to counter receptors on relevant target cells are disclosed. The compounds possess a number of advantageous features, rendering them very suitable for a wide range of applications, including use as detection systems, detection of relevant target cells as well as in various methods. In particular, novel MHC molecule constructs comprising one or more MHC molecules are disclosed. The affinity and avidity of the MHC molecules of the constructs are surprisingly high. The possibility of presenting to the target cells a plurality of MHC molecules makes the MHC molecule constructs an extremely powerful tool e.g. in the field of diagnosis. The invention relates in general to the field of therapy, including therapeutic methods and therapeutic compositions. Also comprised by the present invention is the sample-mounted use of MHC molecules, MHC molecule multimers, and MHC molecule constructs.

Owner:DAKOAS +1

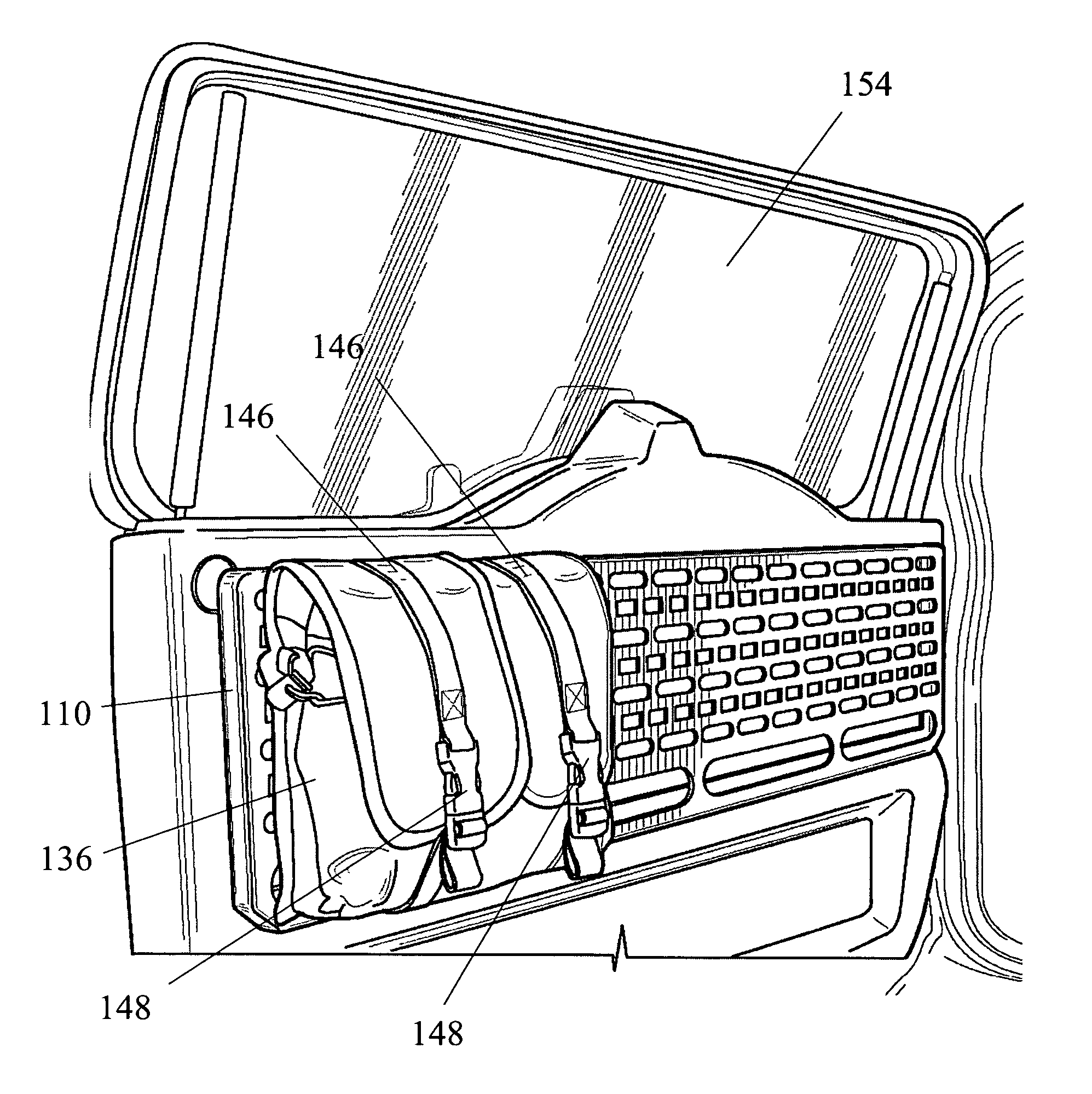

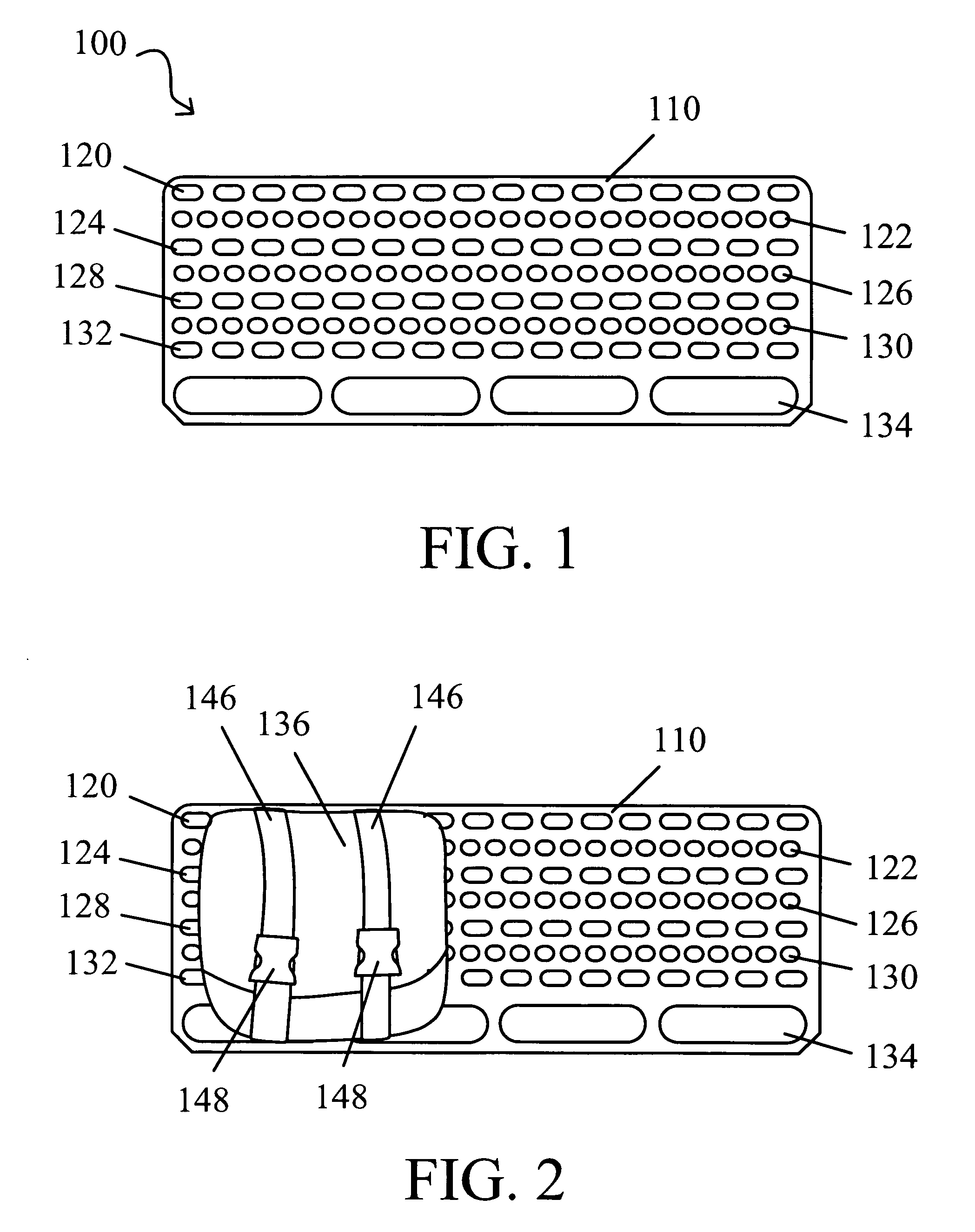

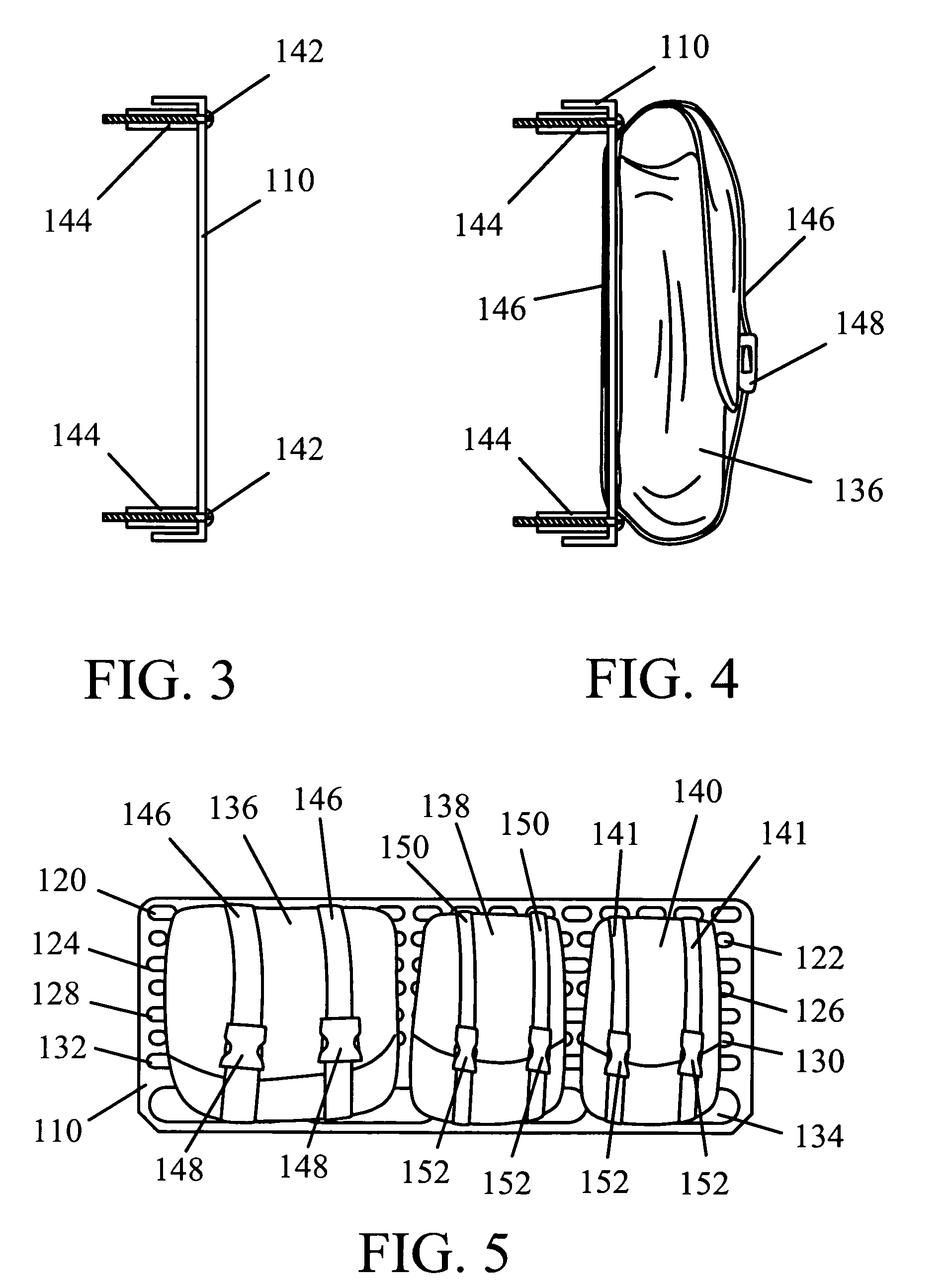

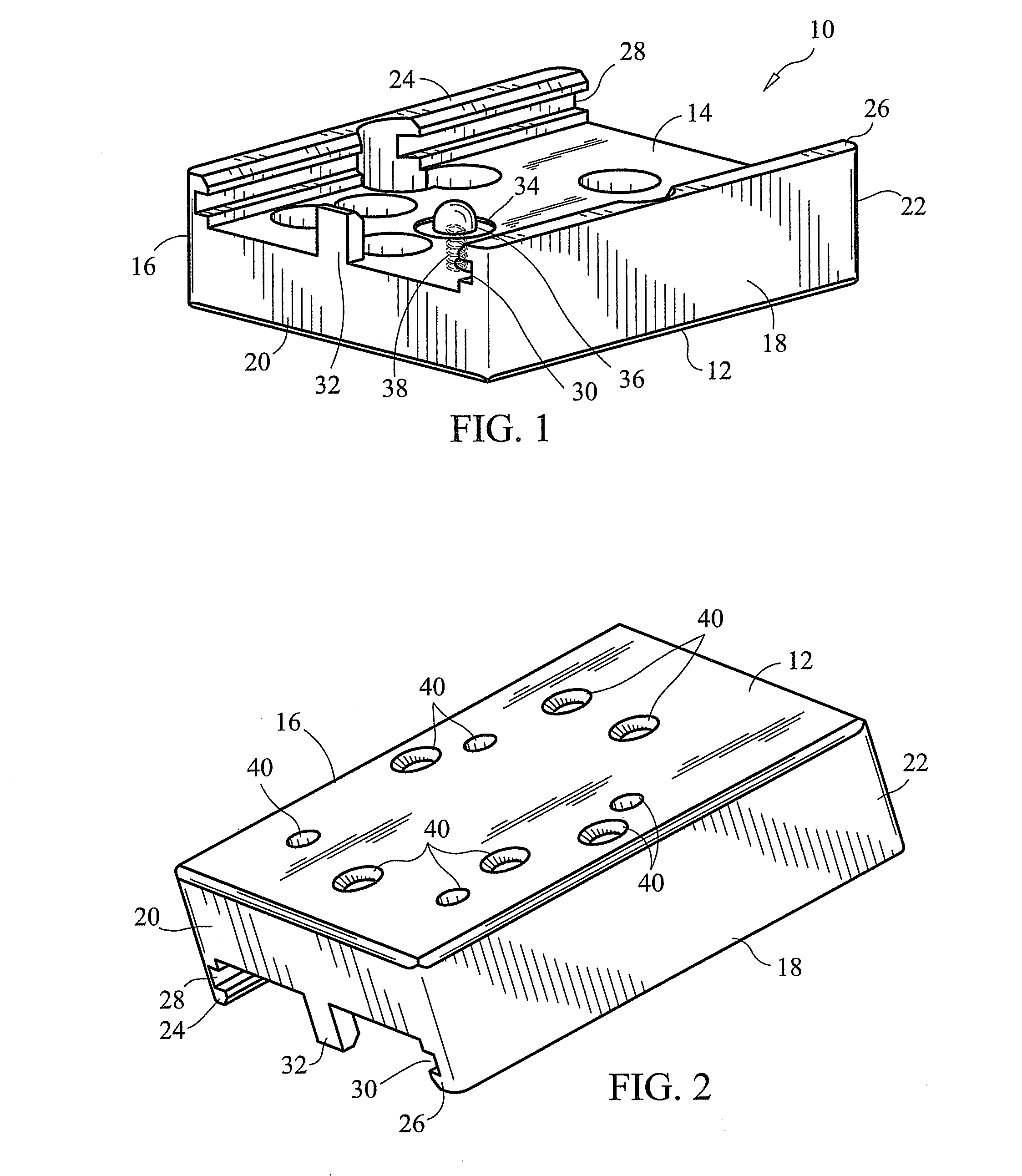

Load Bearing Bracket for Adjustable Gear Bags

A load bearing bracket for adjustable gear bags comprises a base bracket having a plurality of openings disposed therein. The openings are arranged in columns and rows. A top row consists of uniformly sized openings and alternates with another row of uniformly but different sized openings. This arrangement maximizes adjustability when attaching a variety of holding items such as Modular Lightweight Load-carrying Equipment (MOLLE) bags or other equipment bags or holders. The base bracket is mounted using bolts, rivets or other fasteners to a vehicle. The equipment bags have an attached strap that fits within the openings to secure them therein. A plurality of large adjustment openings are disposed along a bottom portion of the base bracket allowing a user to insert a hand to guide and secure the straps. A snap on the bottom of the strap secures the free end of the strap to the bag.

Owner:FROST ANDREW MEYER

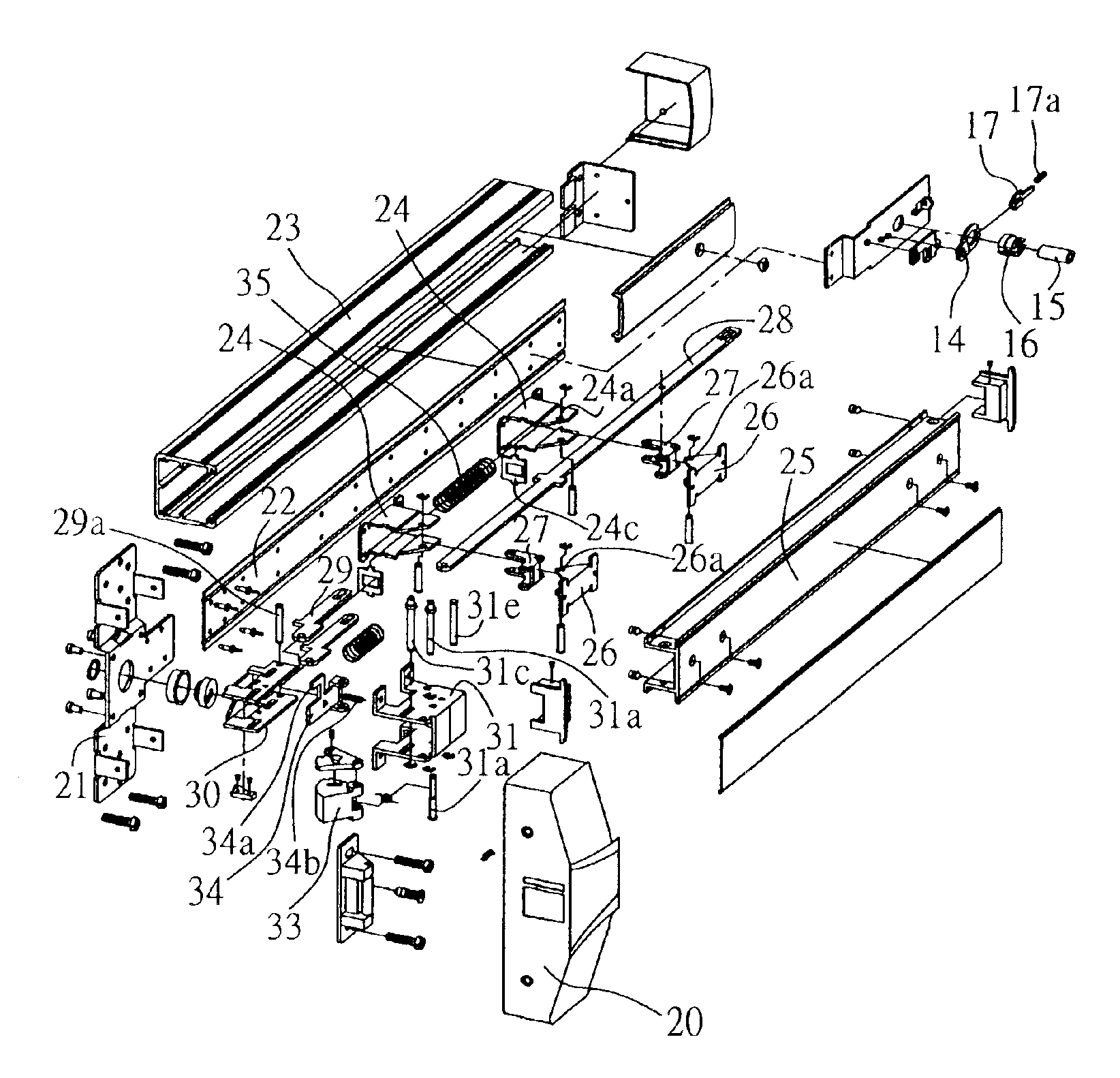

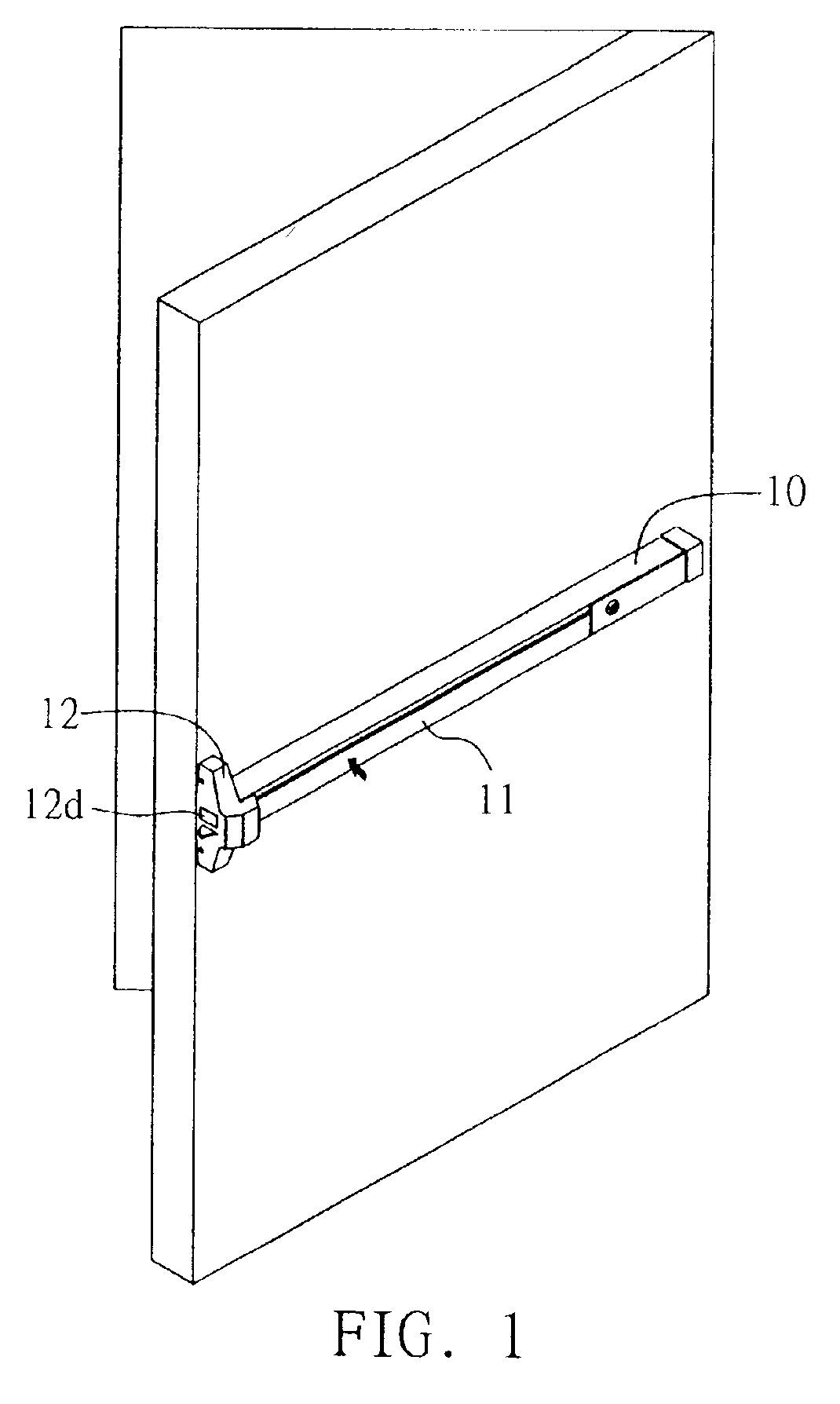

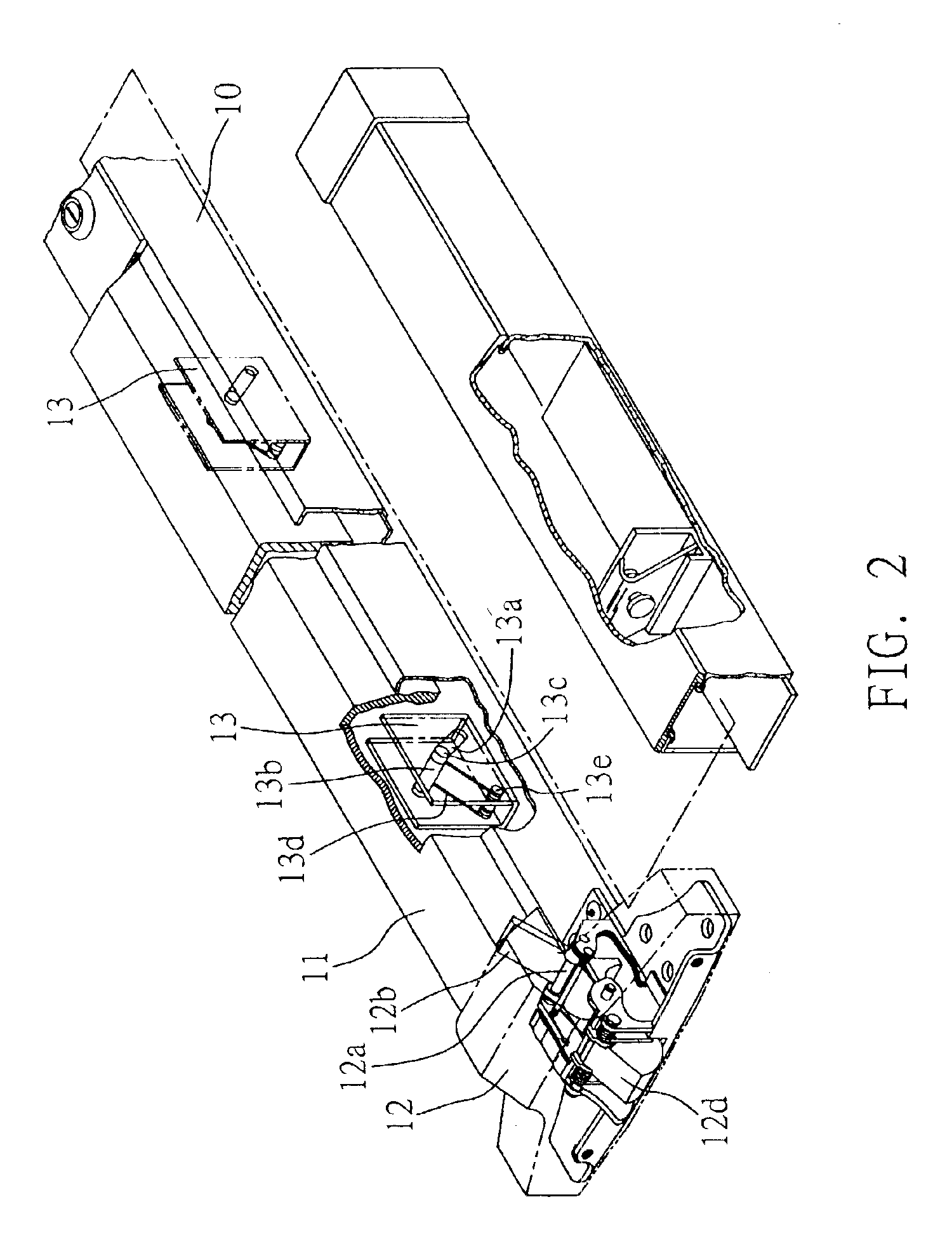

Fire door lock mechanism

InactiveUS6854773B2Prevent hurting and spreadingBuilding locksFastening meansLocking mechanismEngineering

A fire door lock mechanism is provided. A handlebar is coupled to one end of an actuator whose the other end is connected with a push rod. A lock bolt is rotatably mounted in a lock cover mount which accommodates a glide mount used to drive the push rod to move horizontally. When the actuator receives a depression force from the handlebar, the actuator is driven to rotate and induces the push rod to move horizontally. By the movement from the push rod, the lock bolt is driven to rotate to engage or disengage the lock mechanism. A partition and a fire piece are coupled to the glide mount. The fire piece melts at a high temperature during a fire, making the partition moved by a force from an elastic member connected thereto and cause the lock bolt to be engaged with the partition and maintained in a locked state.

Owner:LIN CHING TIEN

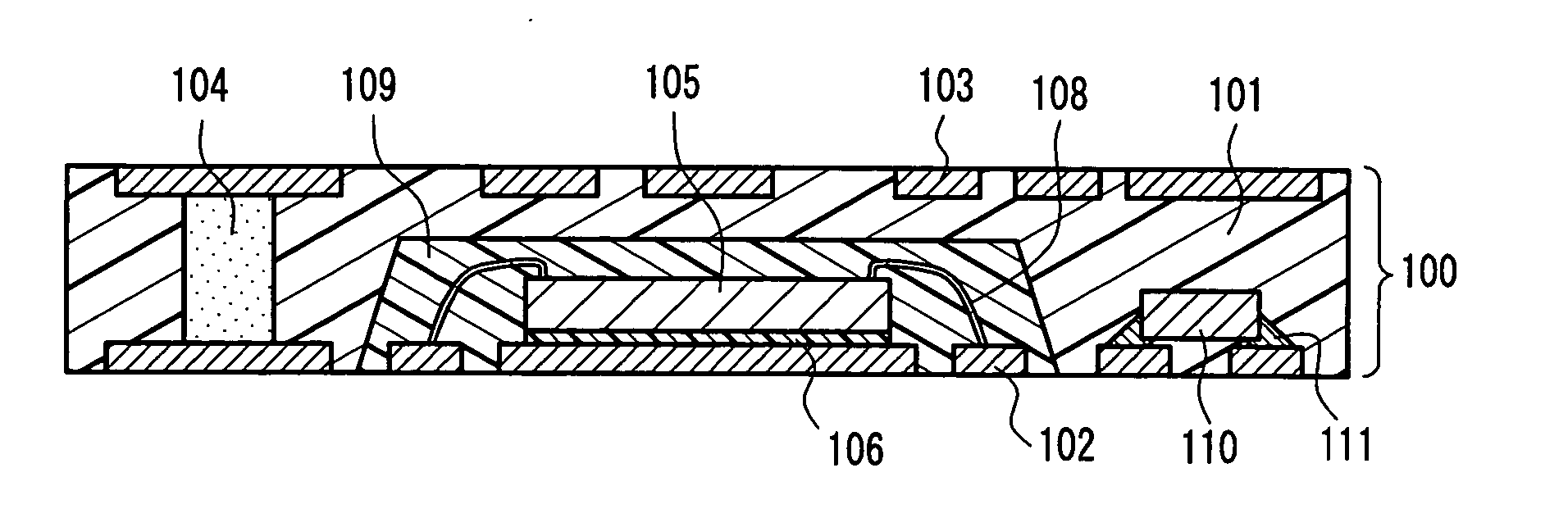

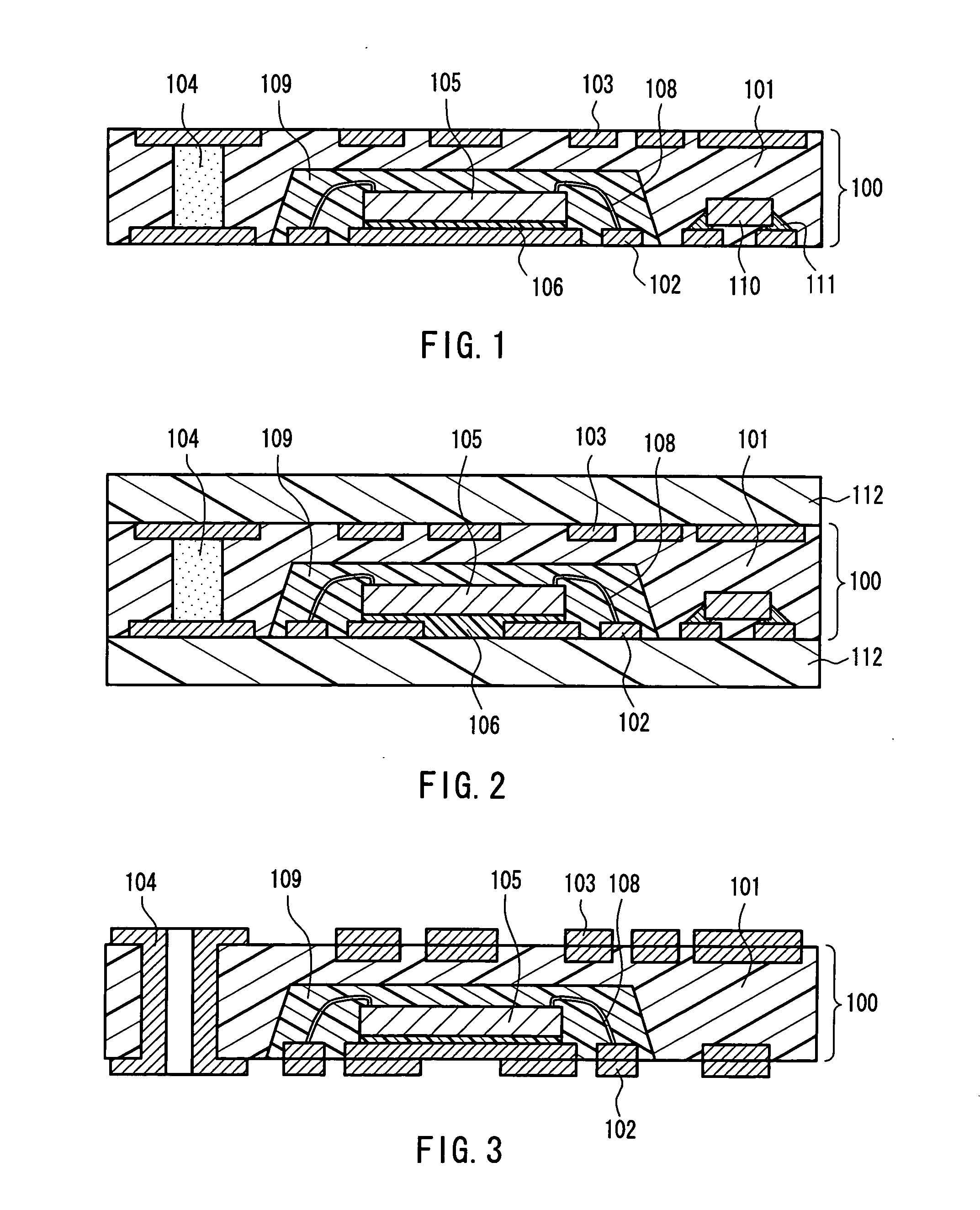

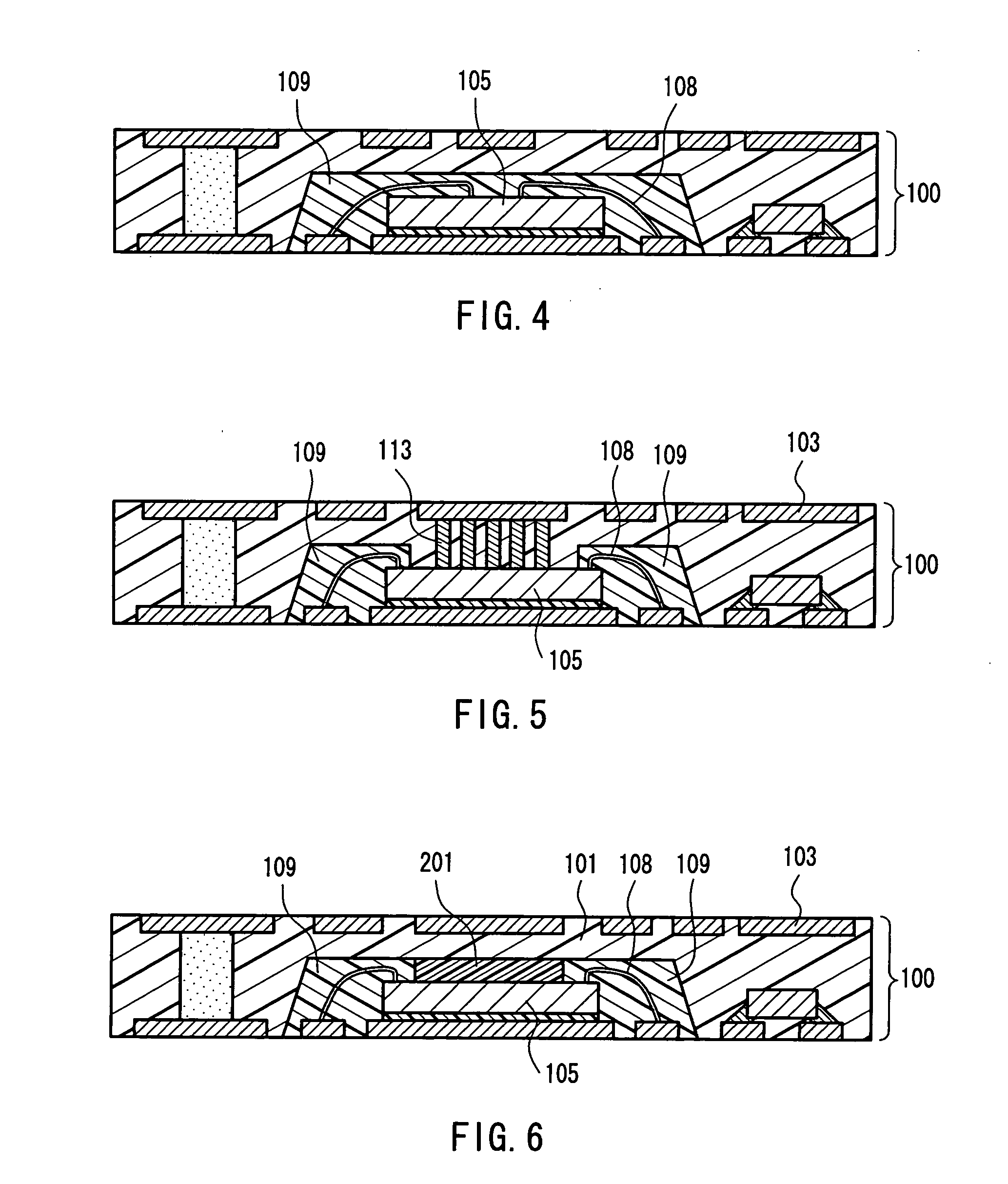

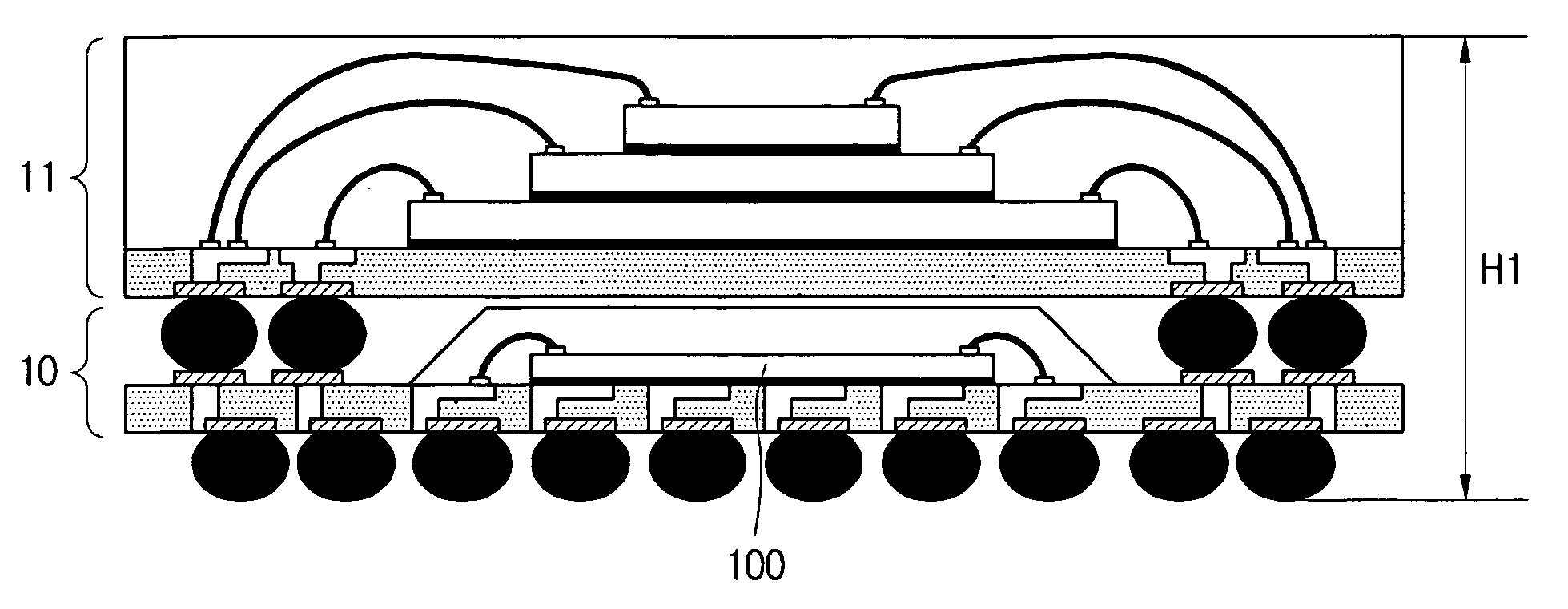

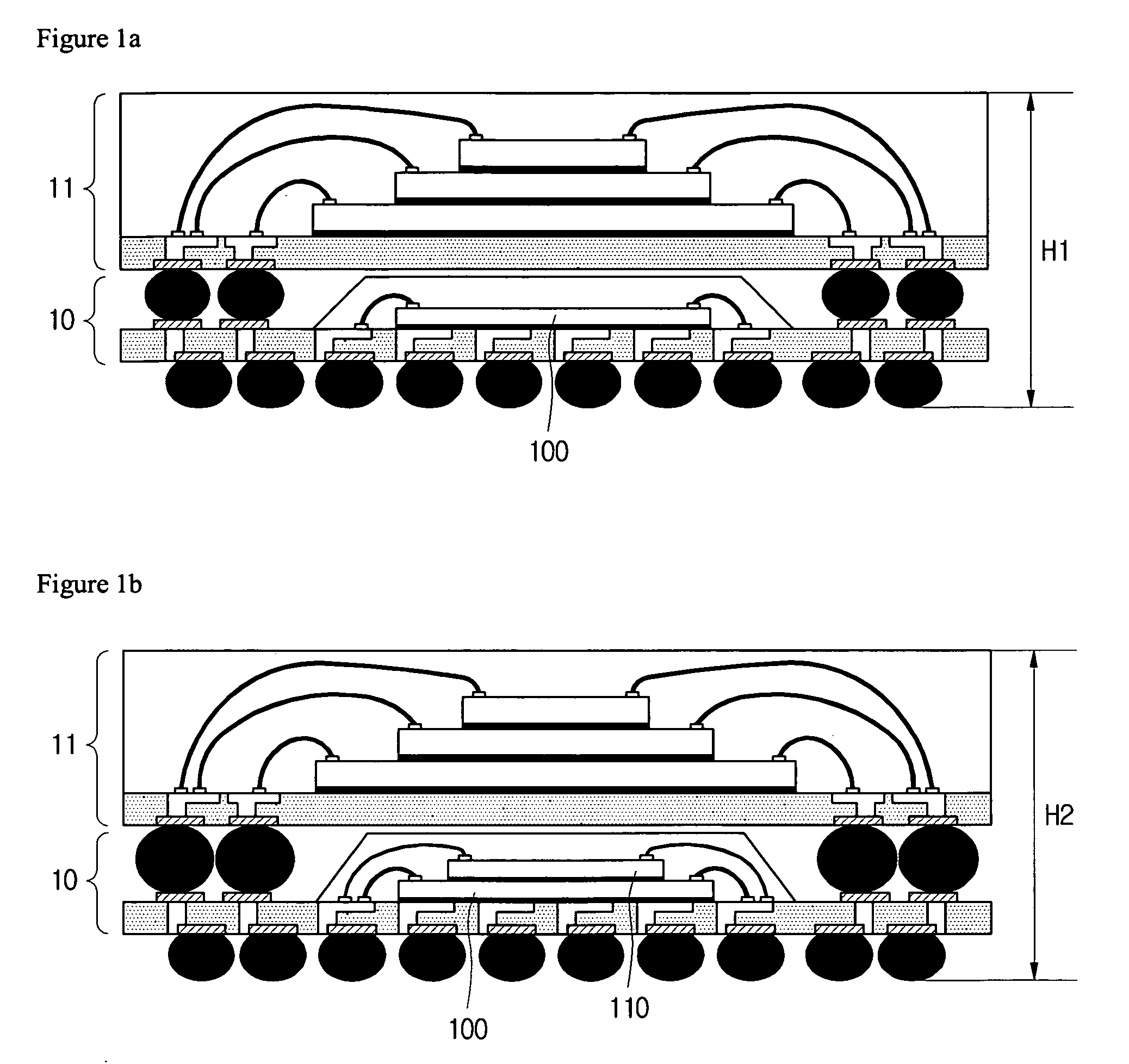

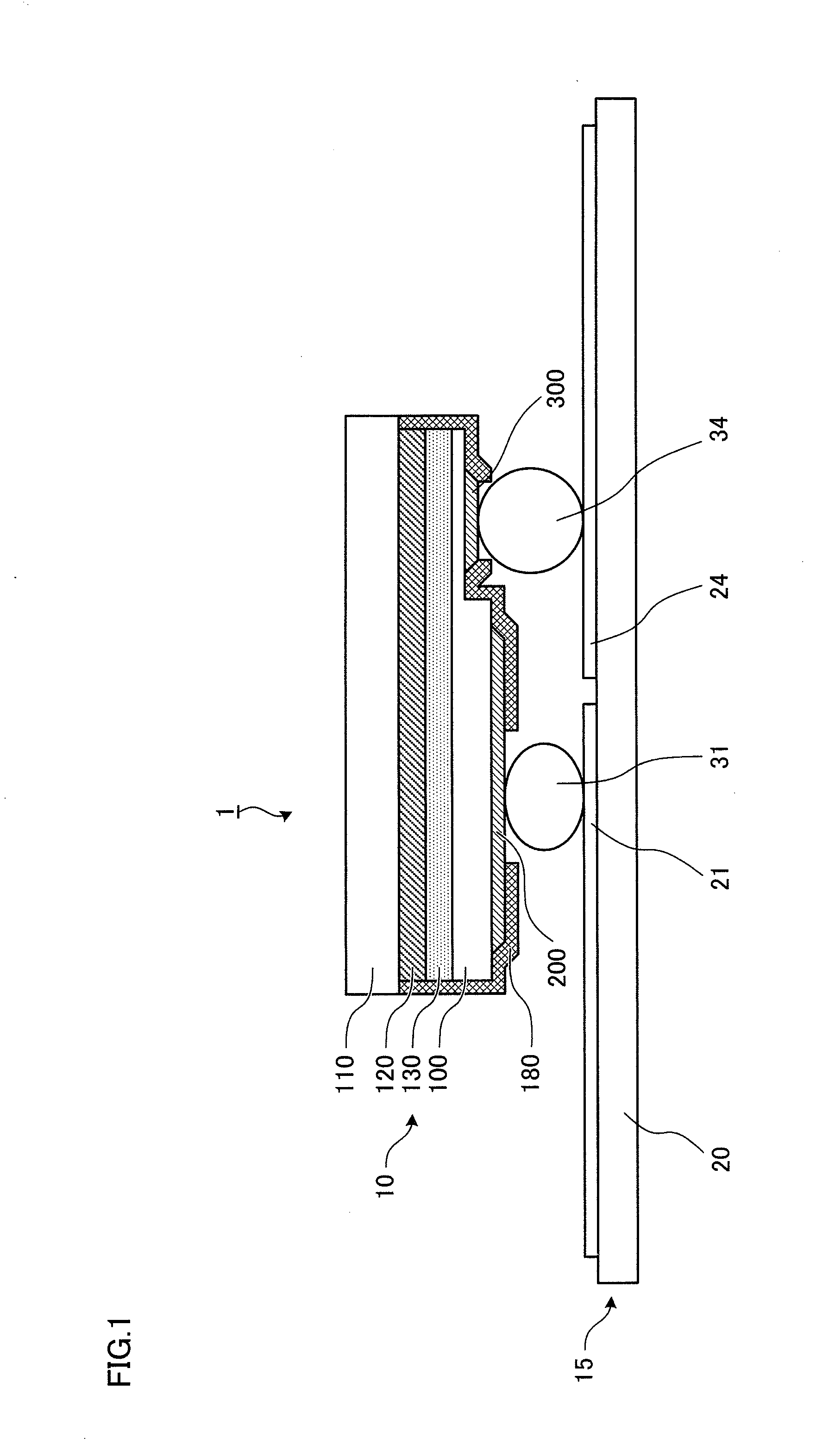

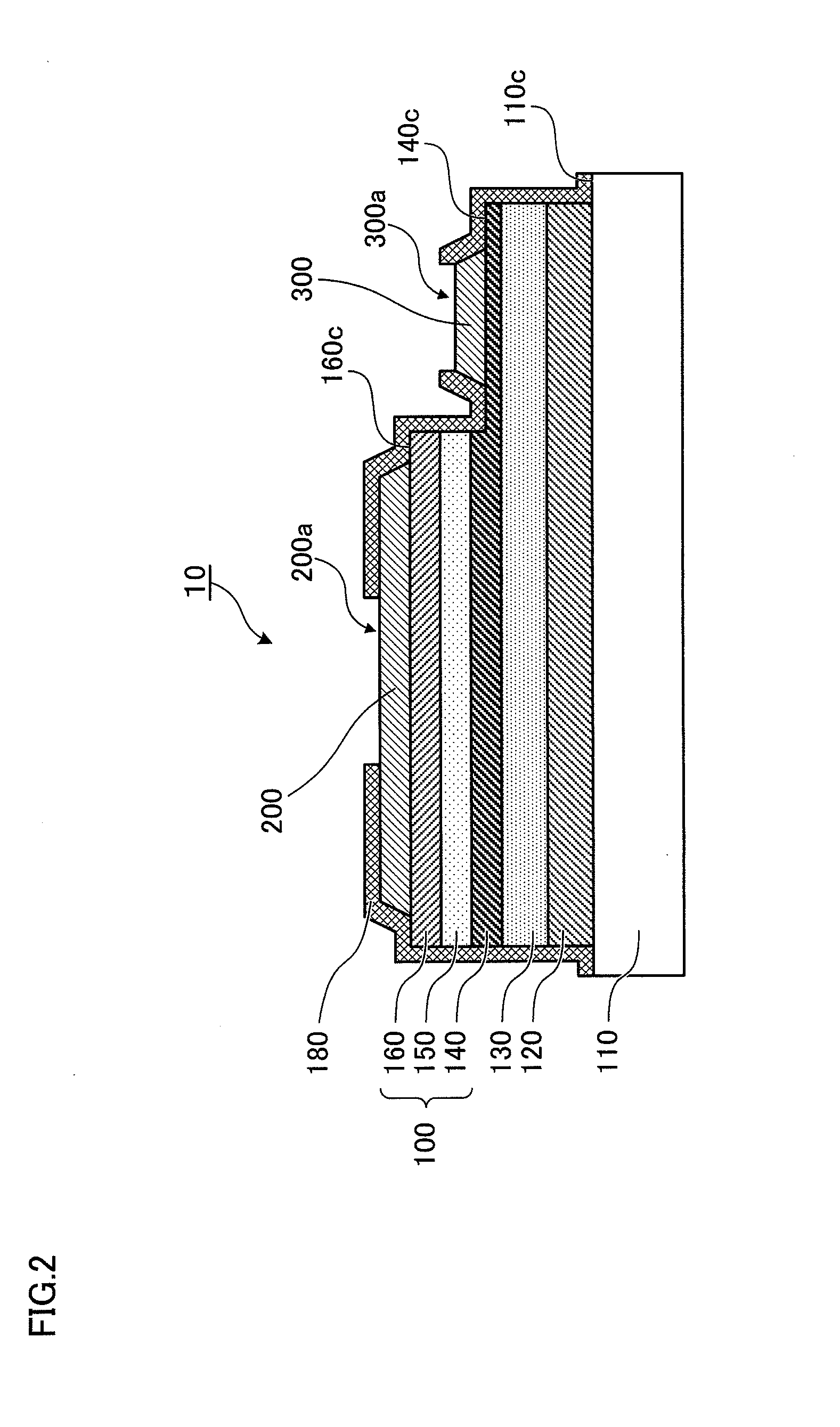

Circuit component built-in module and method for manufacturing the same

InactiveUS20050045369A1Low costEliminateSemiconductor/solid-state device detailsPrinted circuit aspectsLead bondingEngineering

A circuit component built-in module includes the following: an electrical insulating substrate made of a first mixture including a filler and a thermosetting resin; a wiring pattern formed on at least a principal surface of the electrical insulating substrate; circuit components that are arranged inside the electrical insulating substrate and connected electrically to the wiring pattern; and vias for electrically connecting the wiring patterns. At least one of the circuit components is mounted using wires. Part or all of the wires is sealed with a second mixture including a filler and a resin. This circuit component built-in module can eliminate a wire failure or short circuit while using a low cost mounting technique such as wire bonding.

Owner:PANASONIC CORP

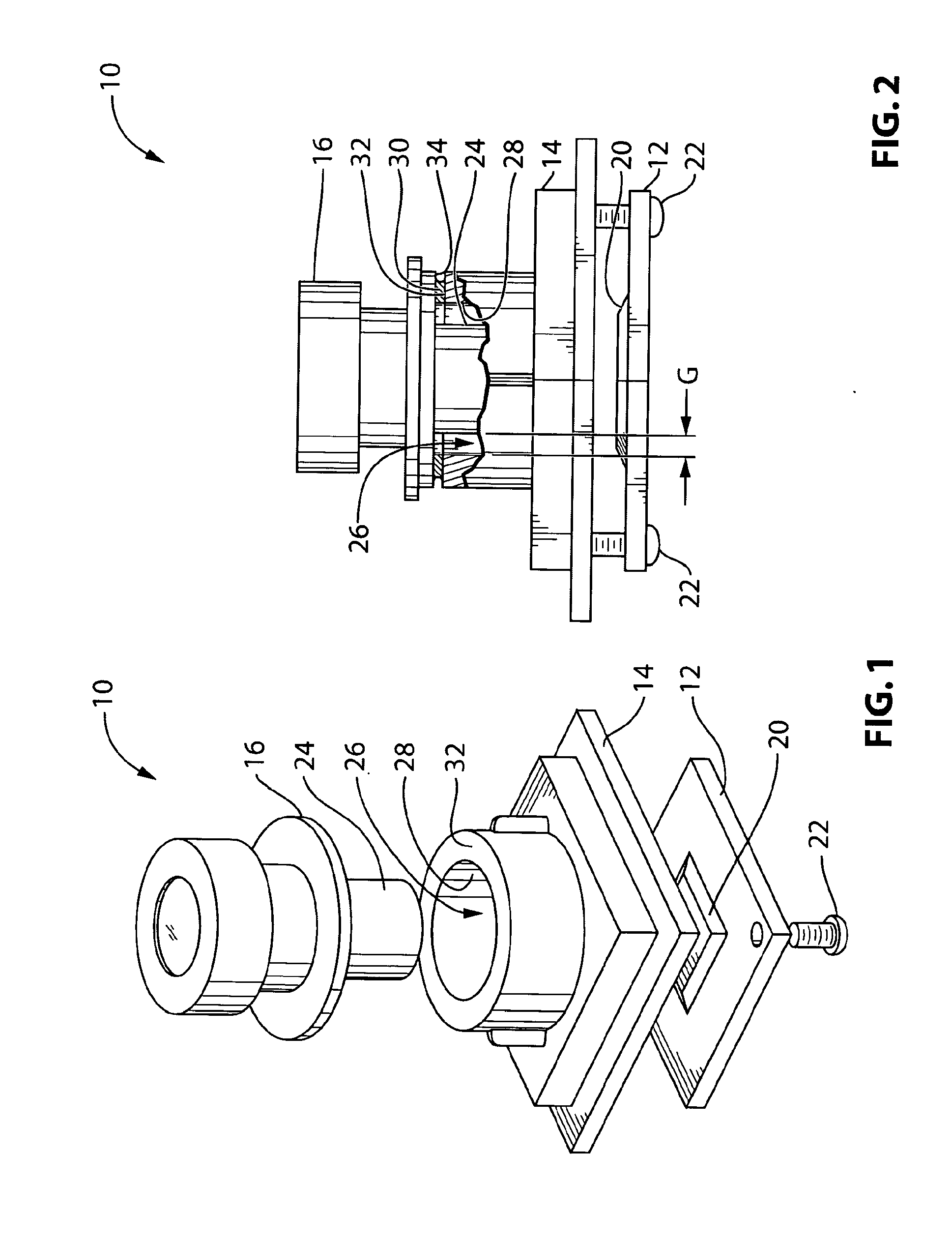

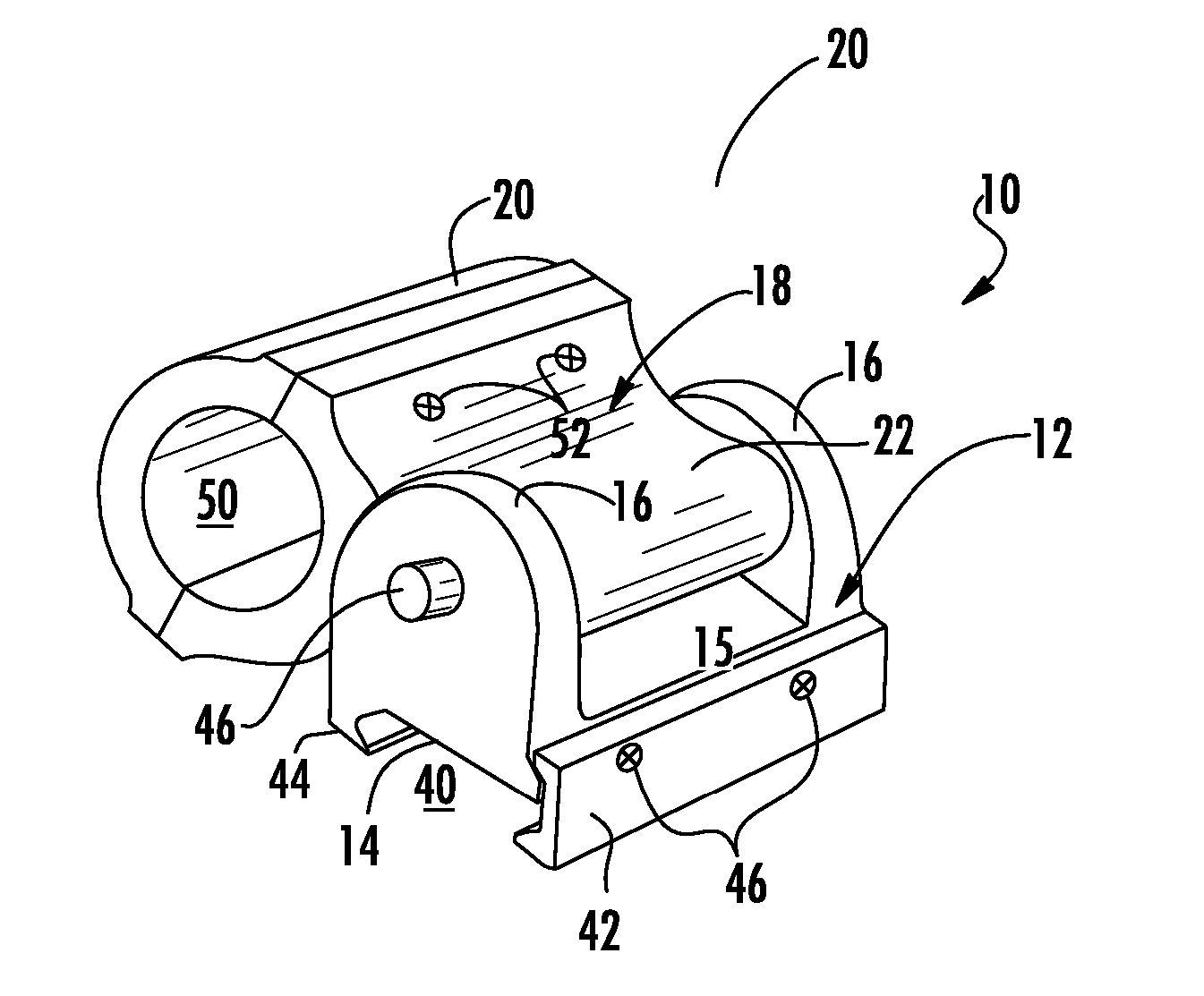

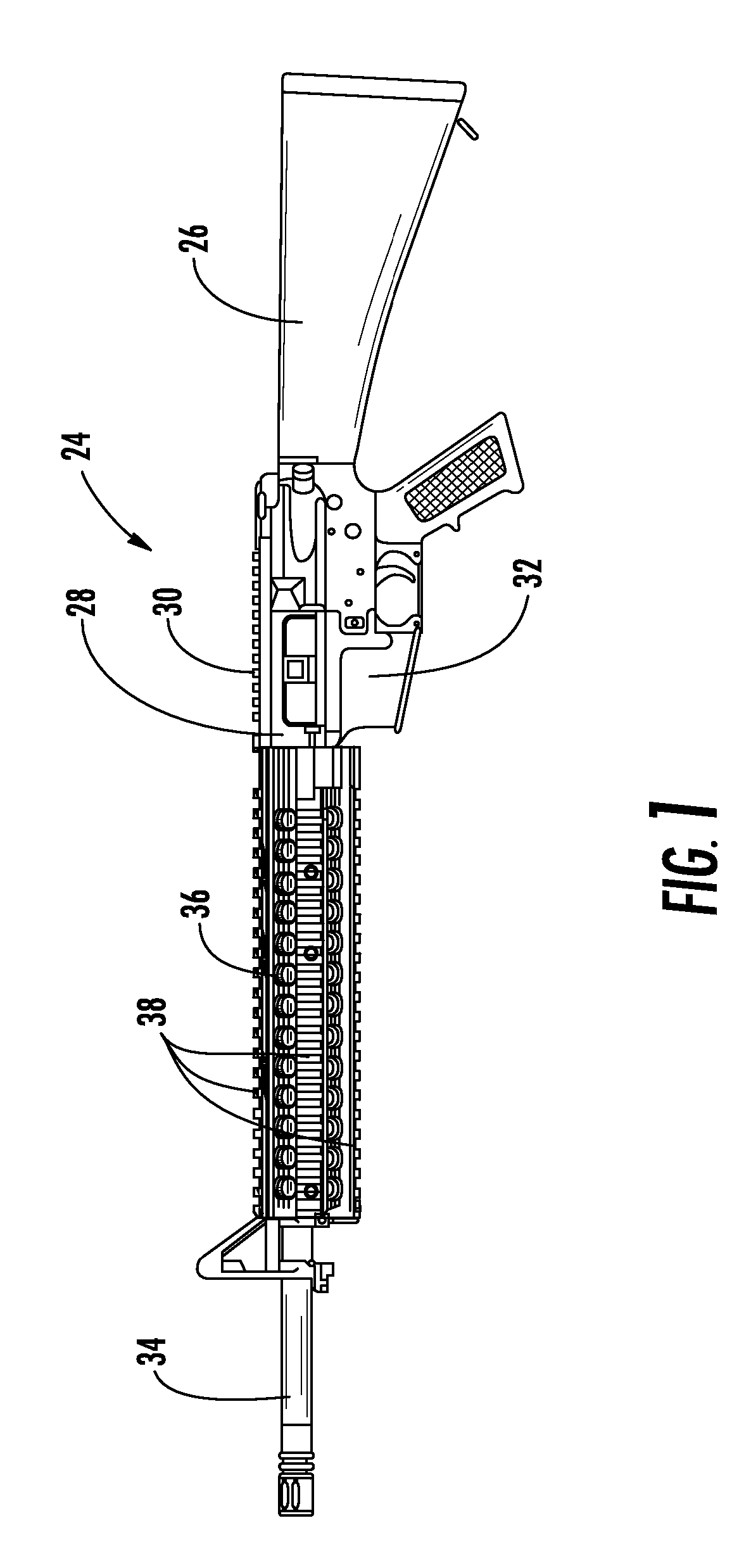

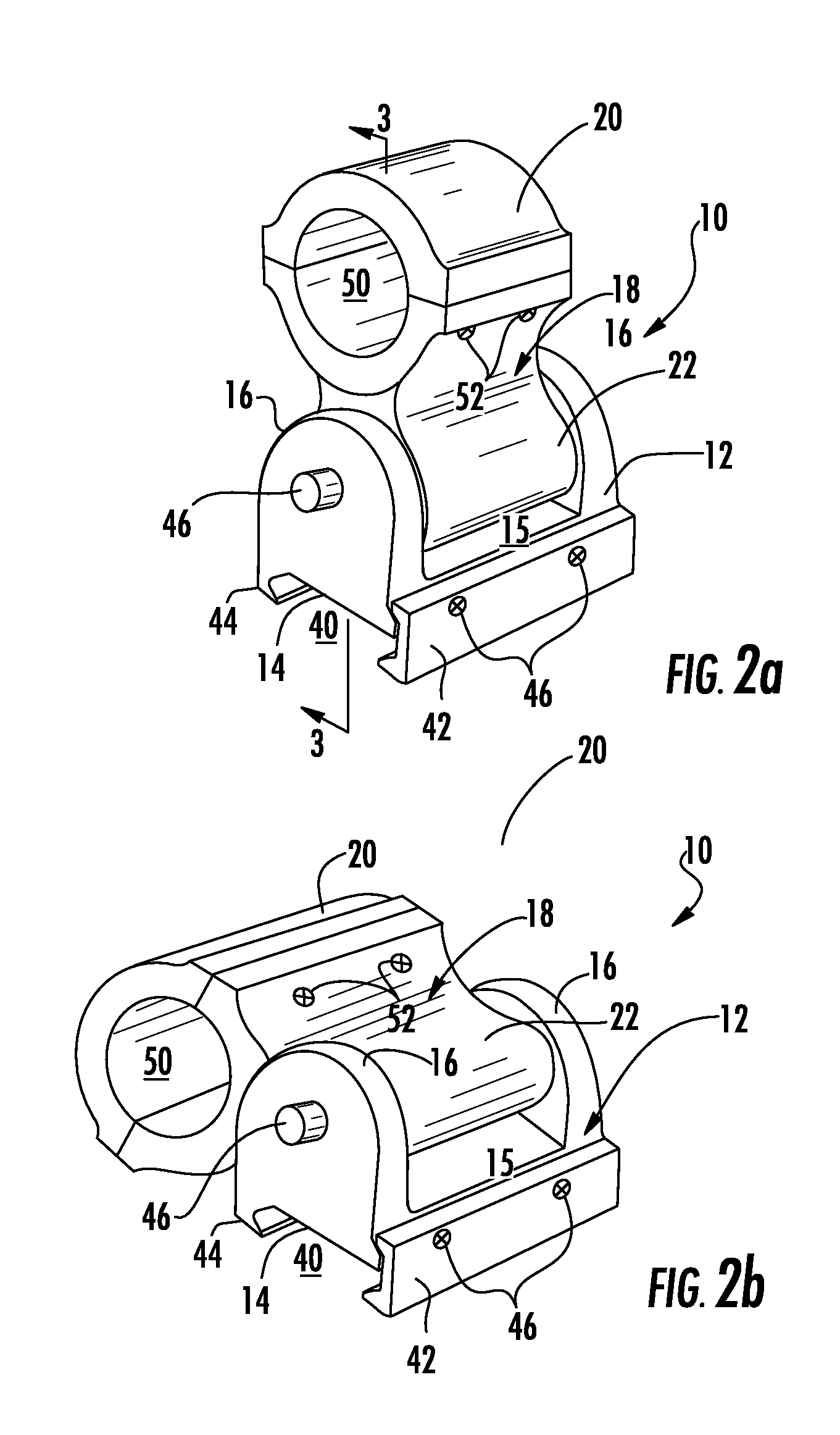

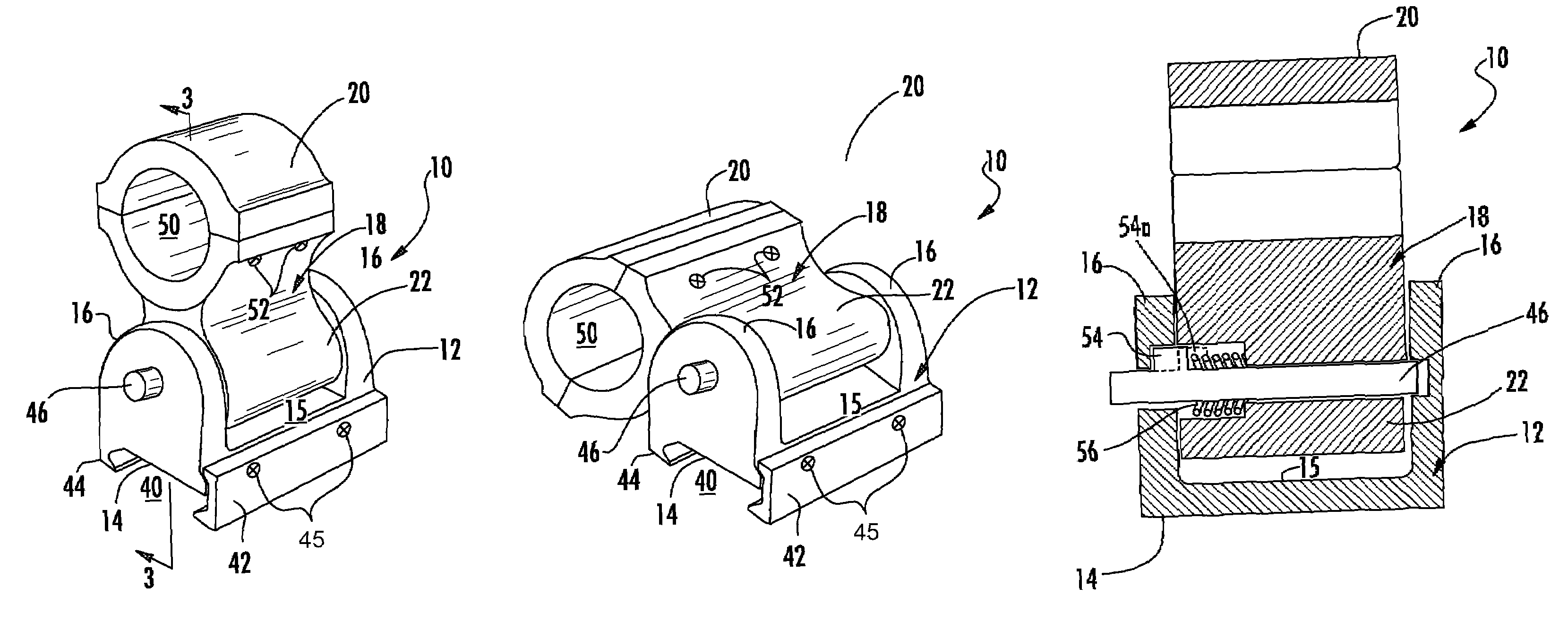

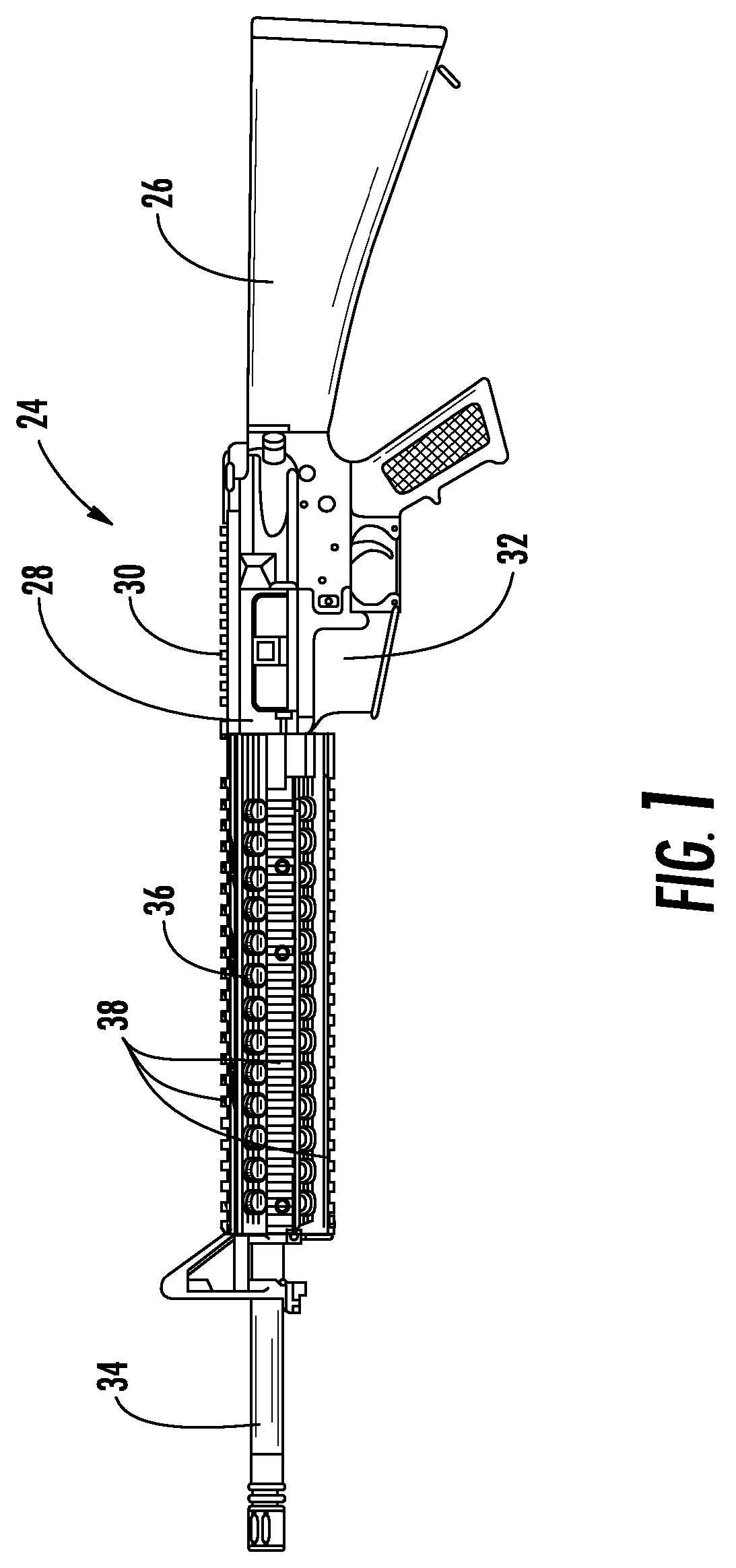

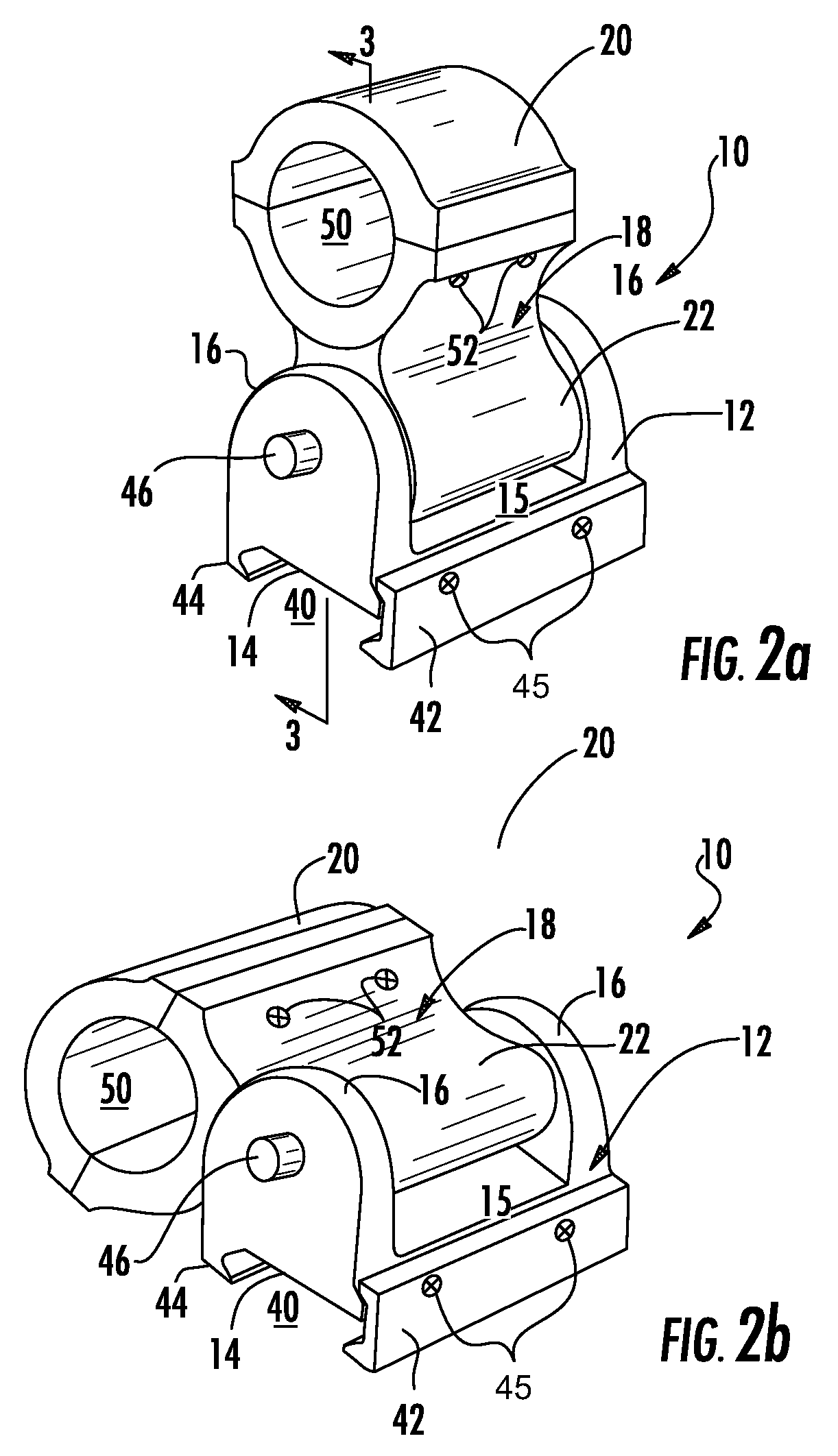

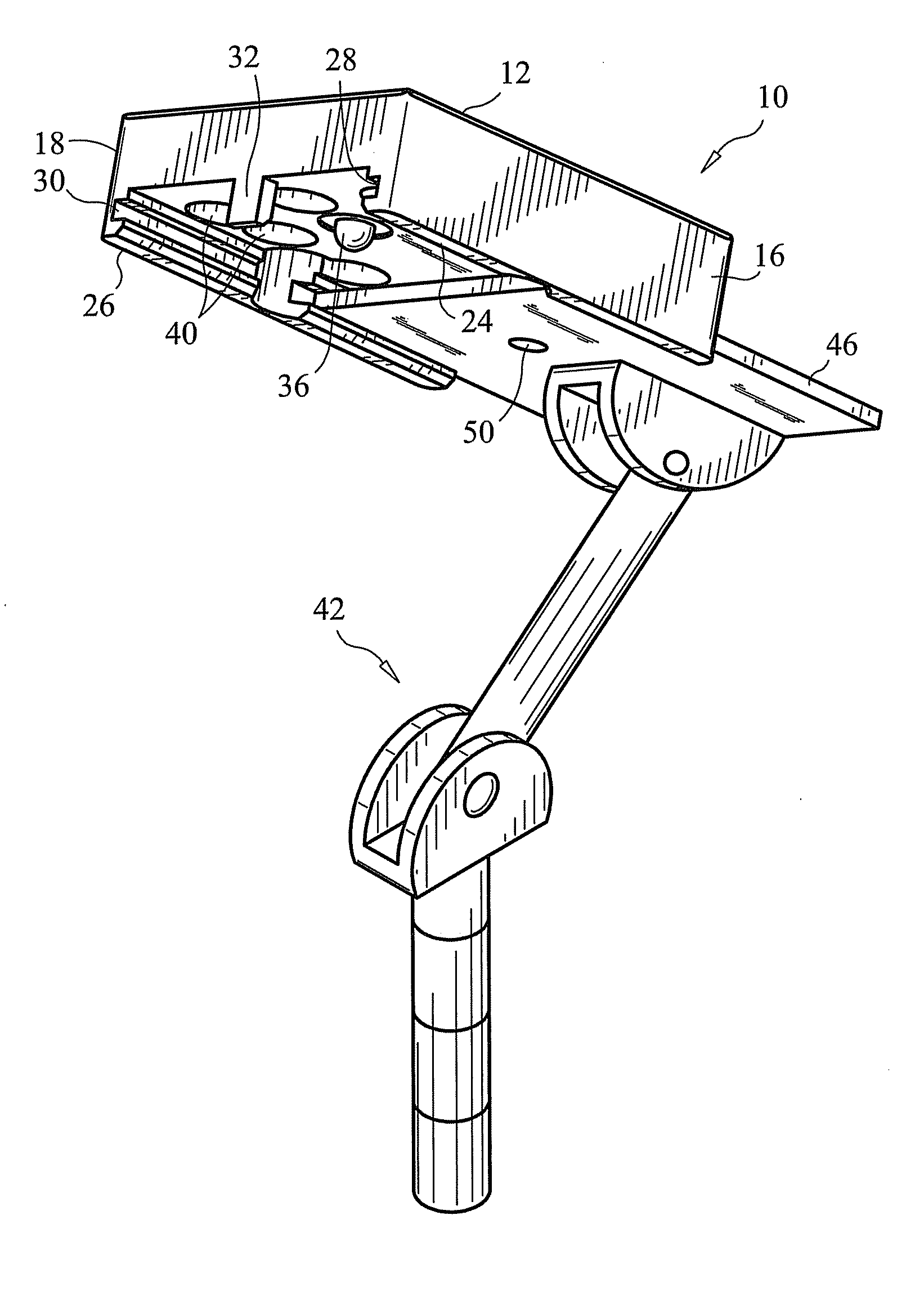

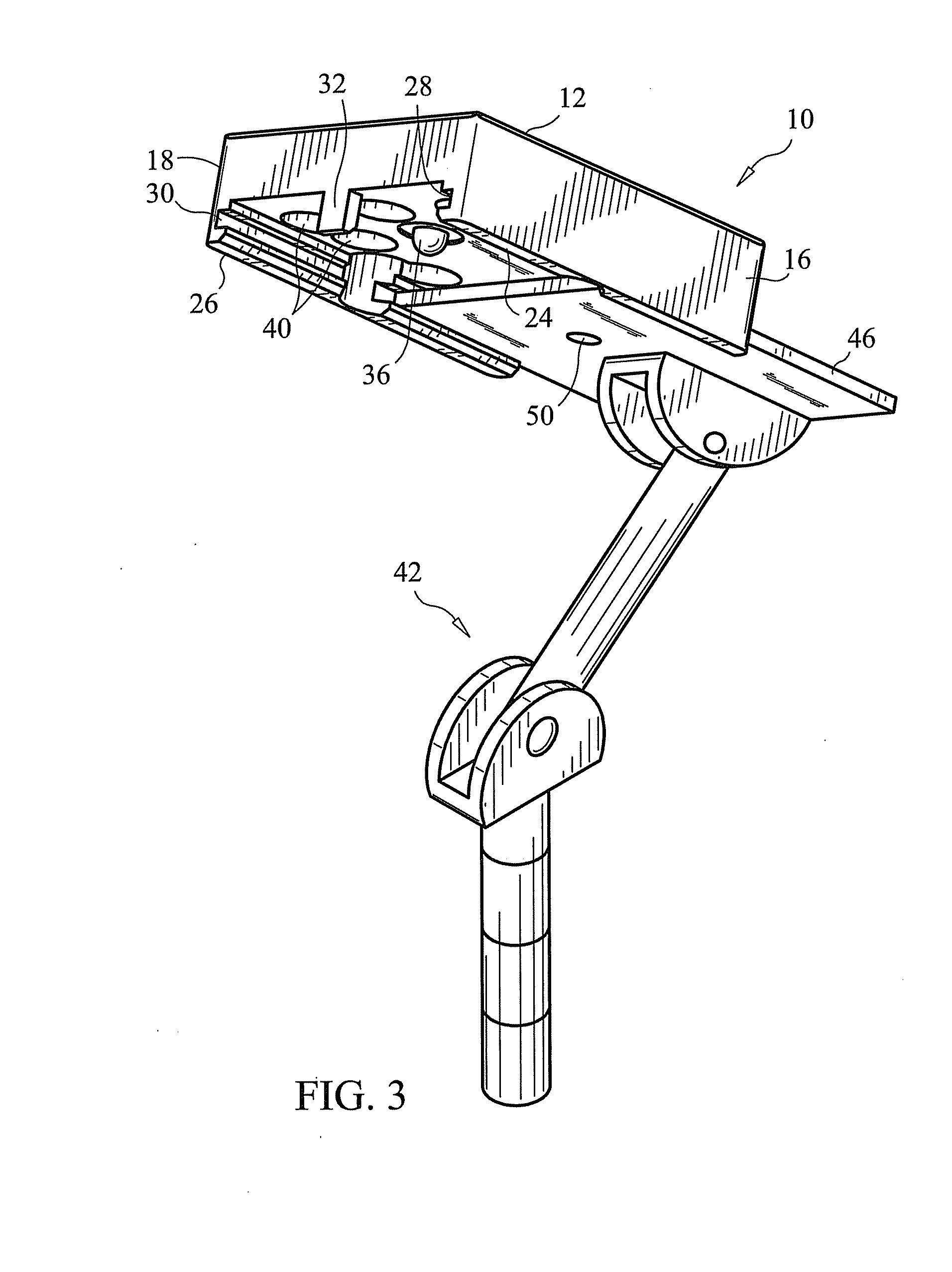

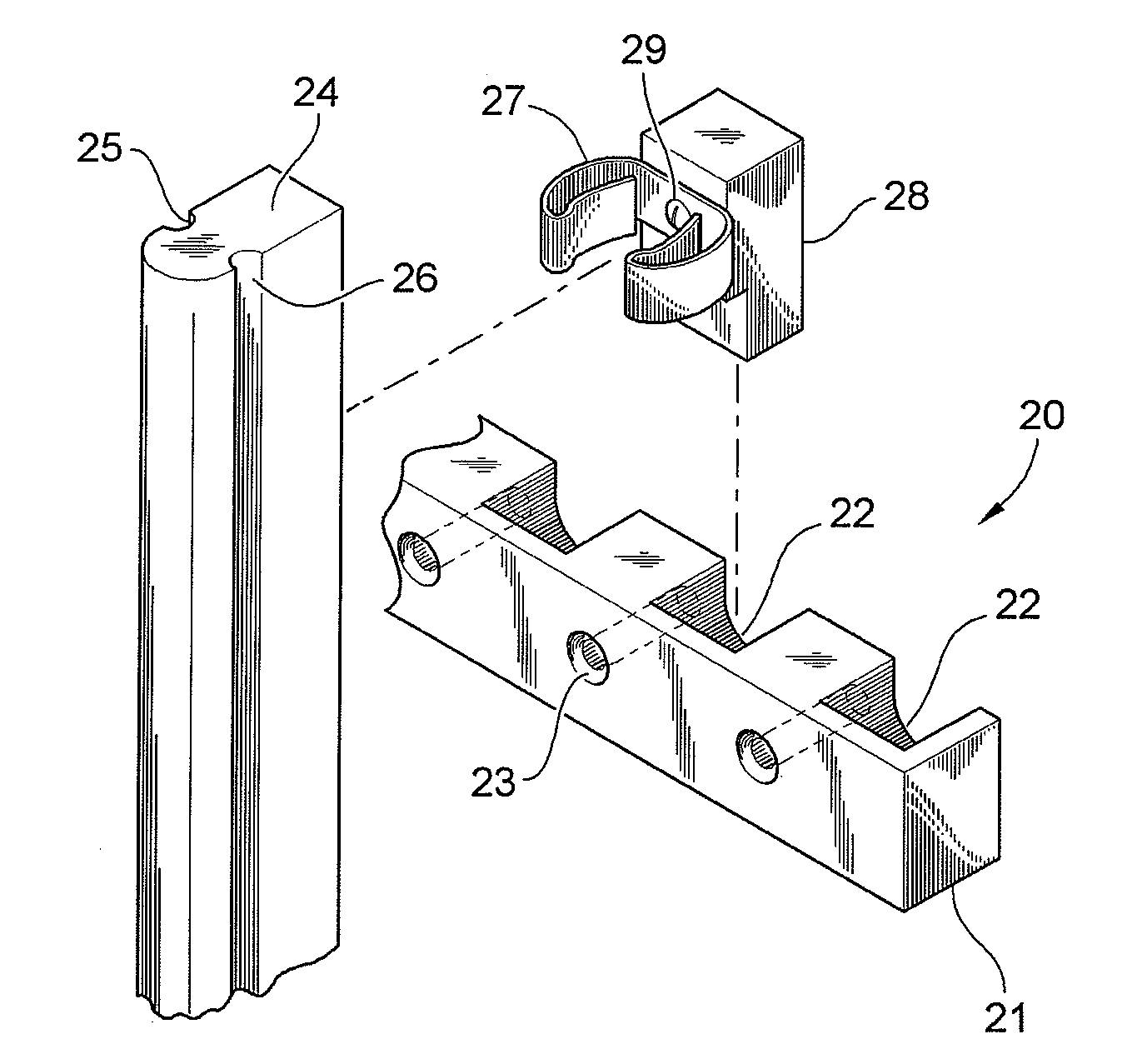

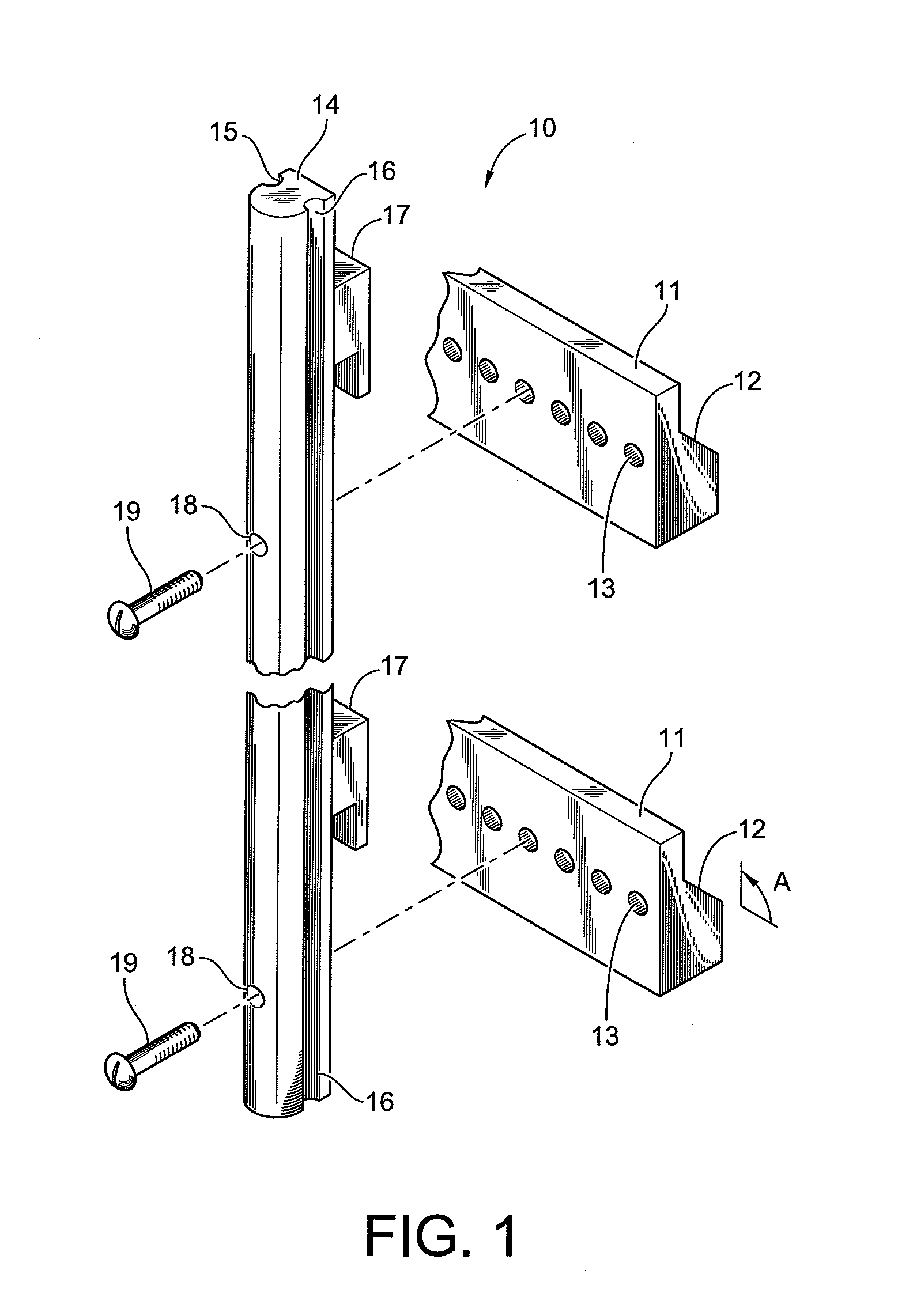

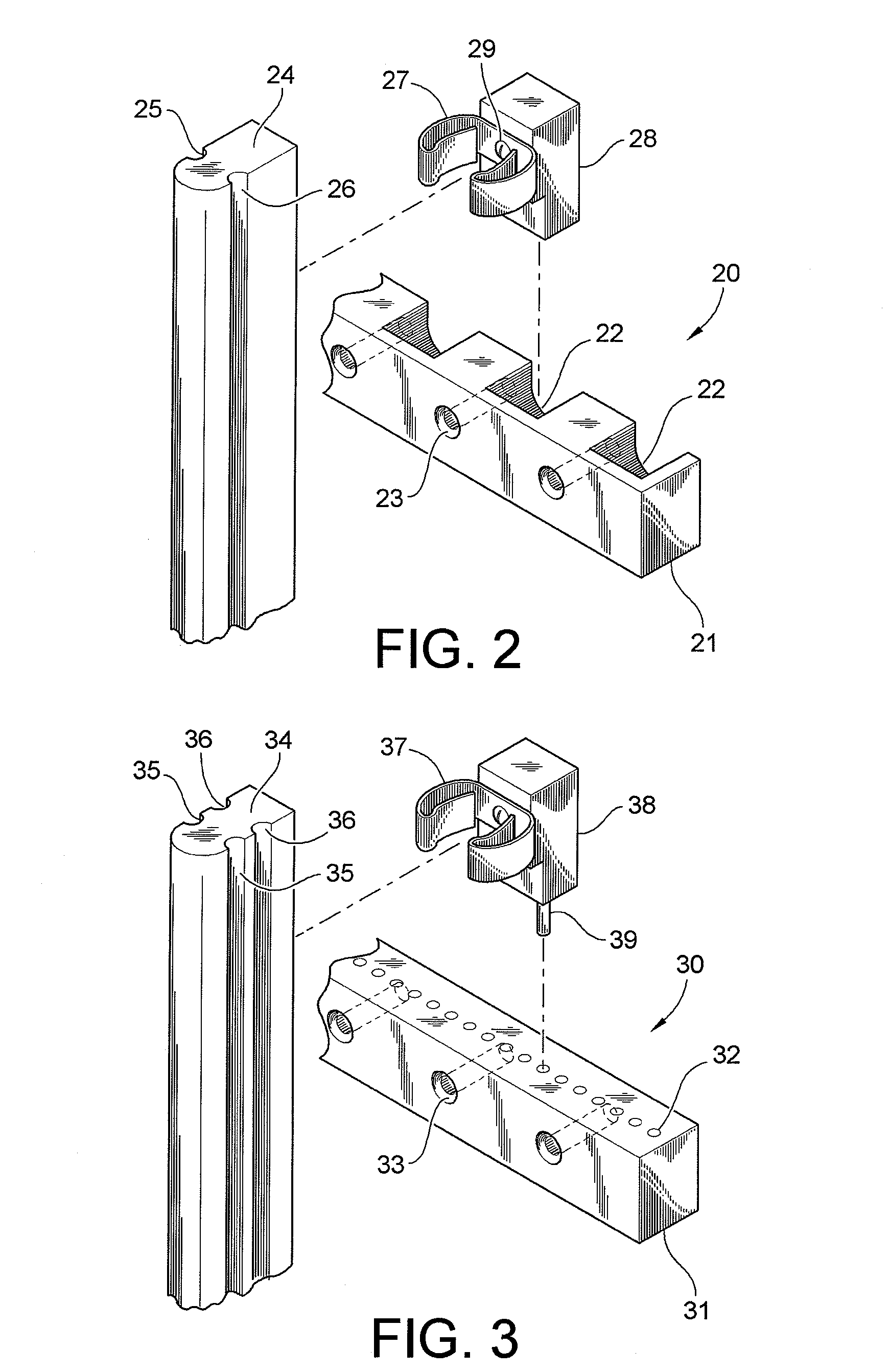

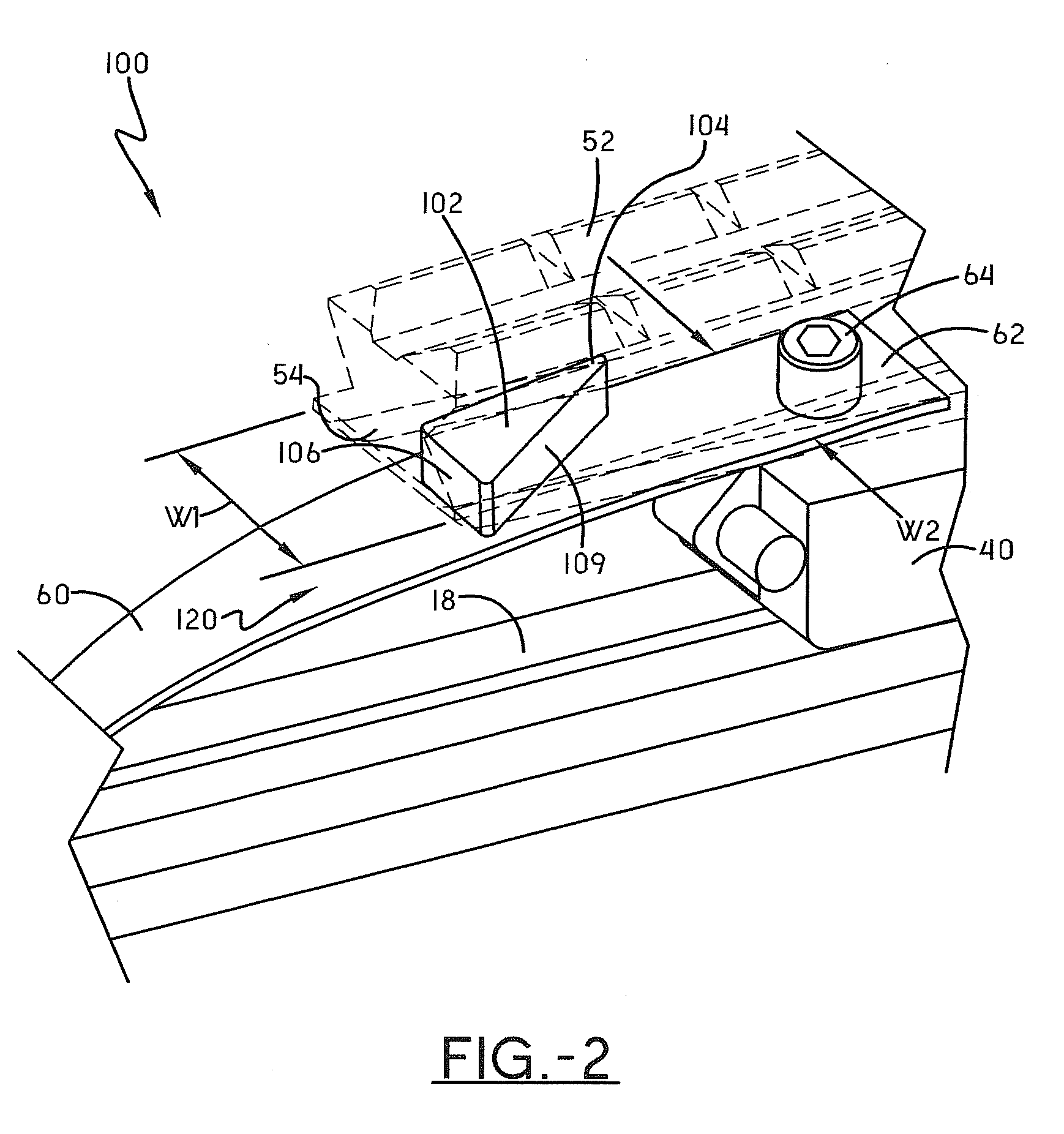

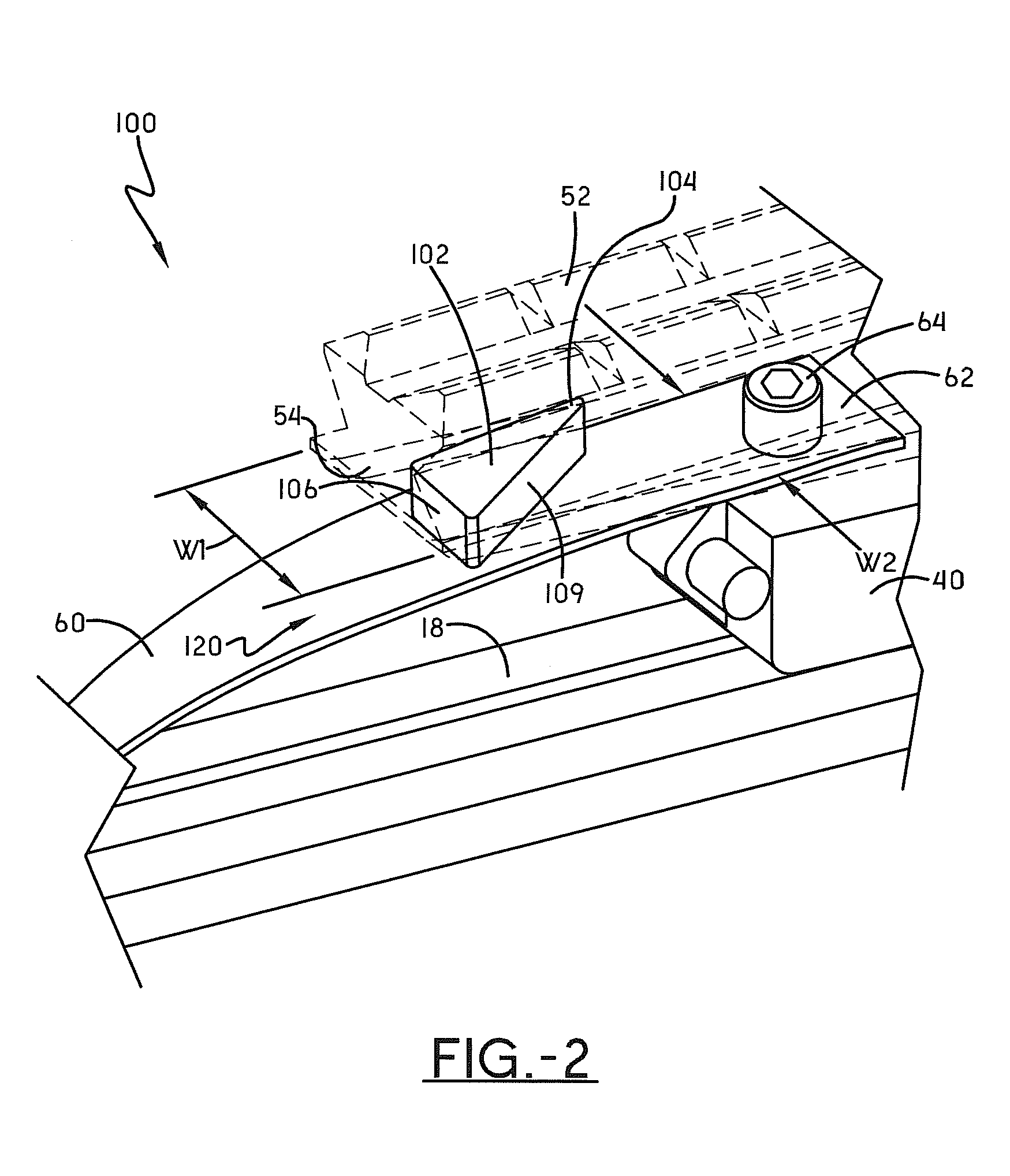

Pivoting mount for a firearm accessory

ActiveUS20060162227A1Rapid deploymentRapid positioningSighting devicesEngineeringElectrical and Electronics engineering

A pivoting accessory mount used for attaching auxiliary devices such as sighting devices to a firearm. The accessory mount includes a base member that attaches to the firearm and includes a mounting support and a shaft. An accessory receiver is pivotally received and retained about the shaft. The accessory receiver is pivotable between an inactive position along the side of the upper receiver of the firearm and an active position extending substantially vertically relative to and in alignment with the upper receiver of the firearm. The mounting shaft is linearly displaceable, thereby engaging the accessory receiver when in the active position to prevent accidental displacement of the accessory receiver.

Owner:SAMSON SCOTT W

Pivoting mount for a firearm accessory

A pivoting accessory mount used for attaching auxiliary devices such as sighting devices to a firearm. The accessory mount includes a base member that attaches to the firearm and includes a mounting support and a shaft. An accessory receiver is pivotally received and retained about the shaft. The accessory receiver is pivotable between an inactive position along the side of the upper receiver of the firearm and an active position extending substantially vertically relative to and in alignment with the upper receiver of the firearm. The mounting shaft is linearly displaceable, thereby engaging the accessory receiver when in the active position to prevent accidental displacement of the accessory receiver.

Owner:SAMSON SCOTT W

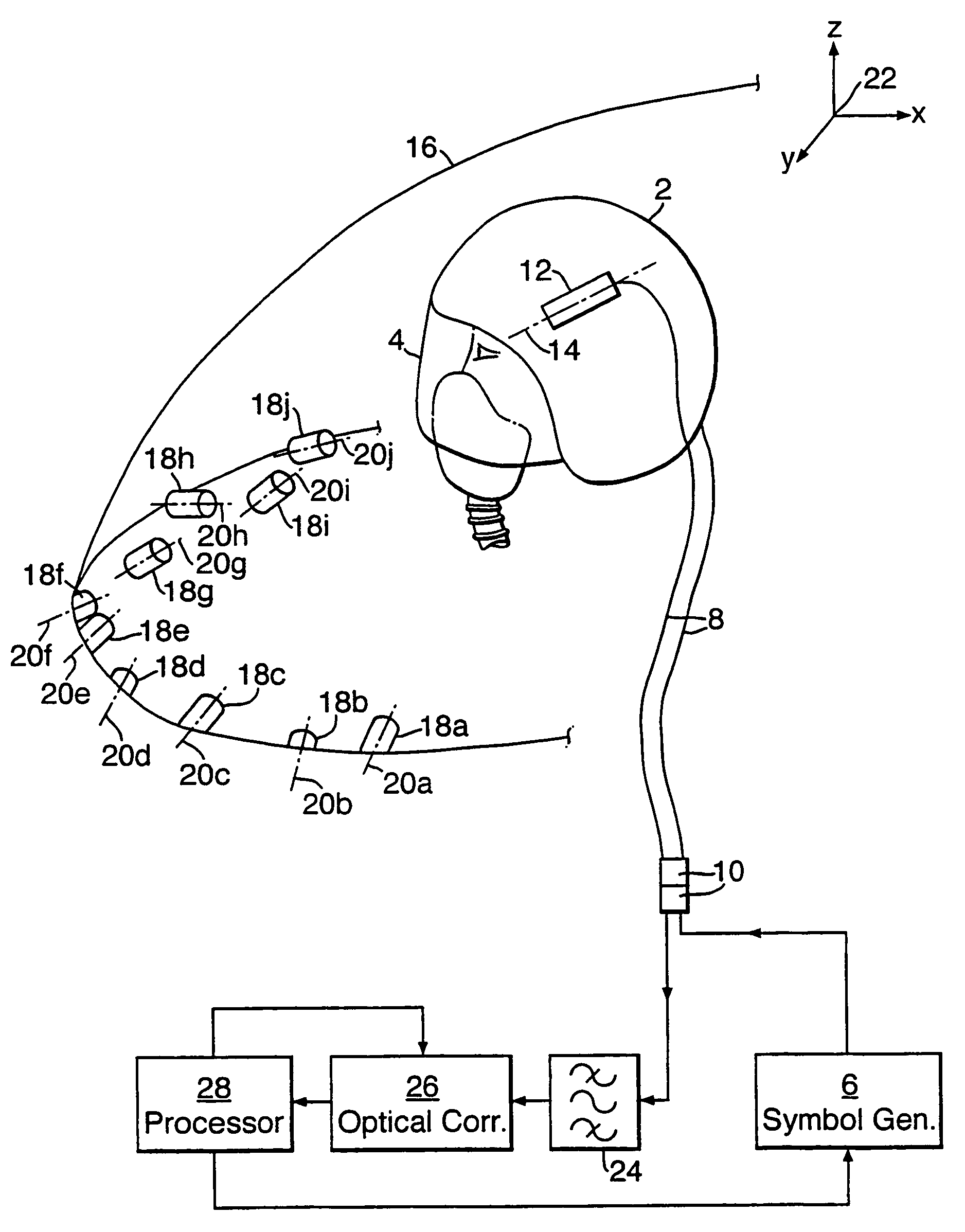

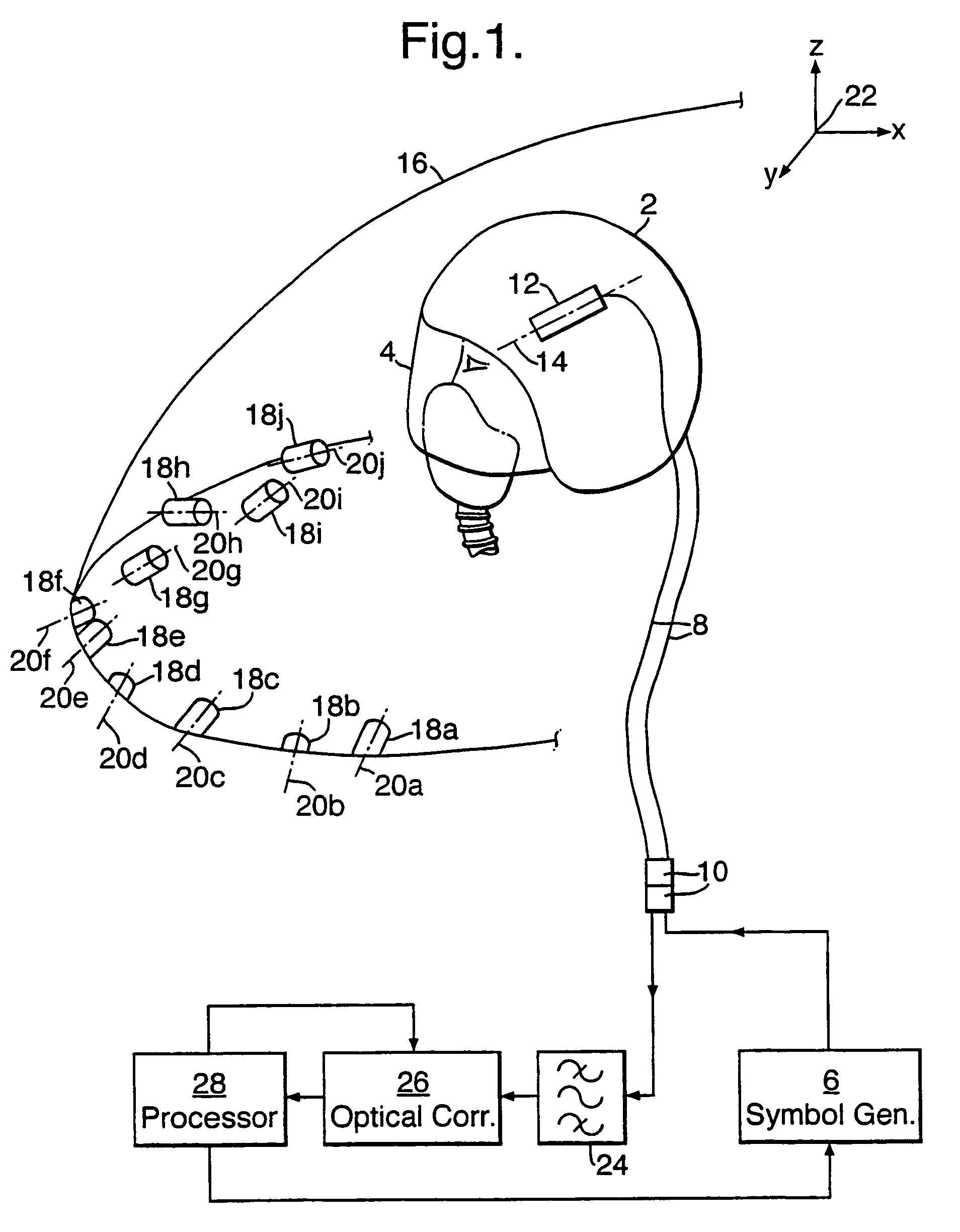

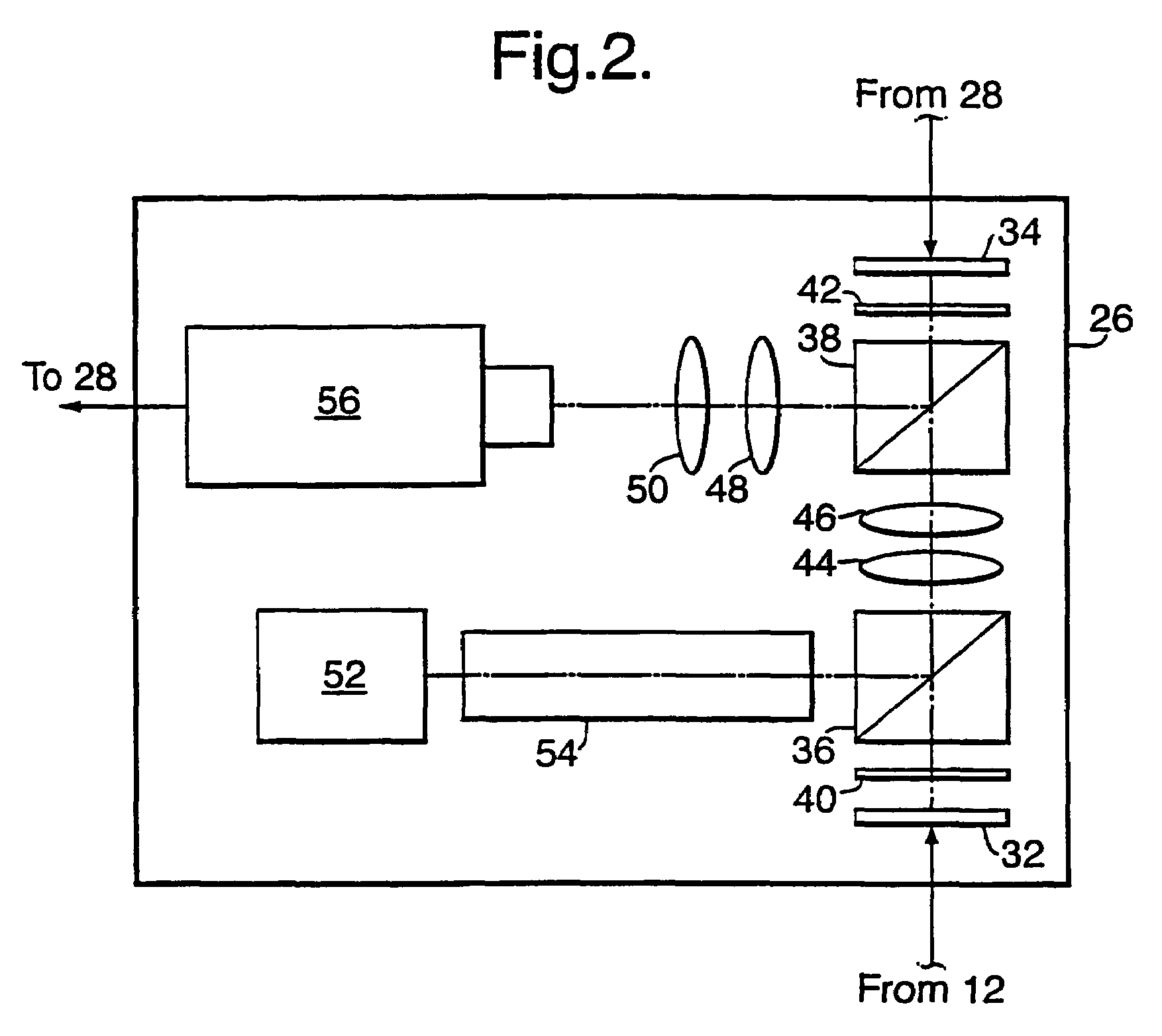

Head tracker system

InactiveUS7046215B1Increase awarenessReduce impactInput/output for user-computer interactionCosmonautic condition simulationsMount usedEngineering

A head tracker system for determining a user's head orientation relative to a datum (22) comprises: a head mounting (2) for attachment to the user's head; an optical sensor (12) which in use is located in fixed relation with a known fixed point relative to the head mounting (2) and a plurality of distinguishable markings (18a–18j) each of which when in use is located in fixed relation with a respective known point which is fixed relative to the datum (22). The head tracker further comprises an optical correlator (26) for optically correlating the optical image from the optical sensor (12) with an optical image representative of at least one of said markings (18a–18j); and means (28) for determining the orientation of the head mounting using the output from the optical correlator when it detects that there is correlation between the images.

Owner:BAE SYSTEMS PLC

Adaptor for vehicle mounts

InactiveUS20080179478A1Improve adaptabilityEasy and quick connectionStands/trestlesKitchen equipmentIn vehicleEngineering

An adaptor for securing portable devices to mounts used in vehicles such as motorcycles comprises a top wall, a bottom wall, opposed end walls and opposed side walls each having a lower portion that projects outwardly from the bottom wall and is formed with a channel extending from one end wall to the other. A support plate of the vehicle mount slides into these channels, and a spring-biased pin carried by the bottom wall of the adaptor secures the adaptor in place onto the vehicle mount by extending into a locking bore formed in the support plate of such mount.

Owner:LEE MICHAEL

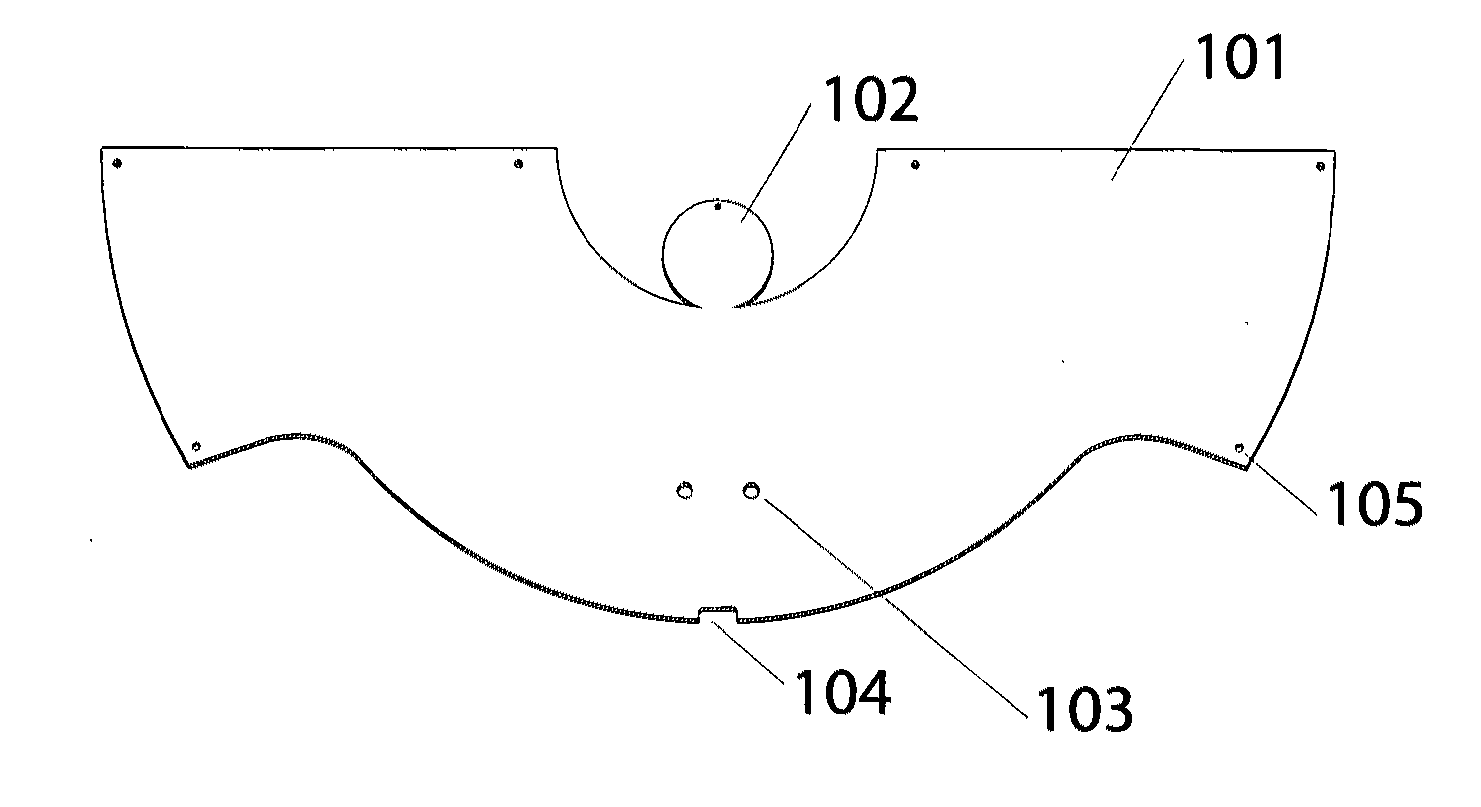

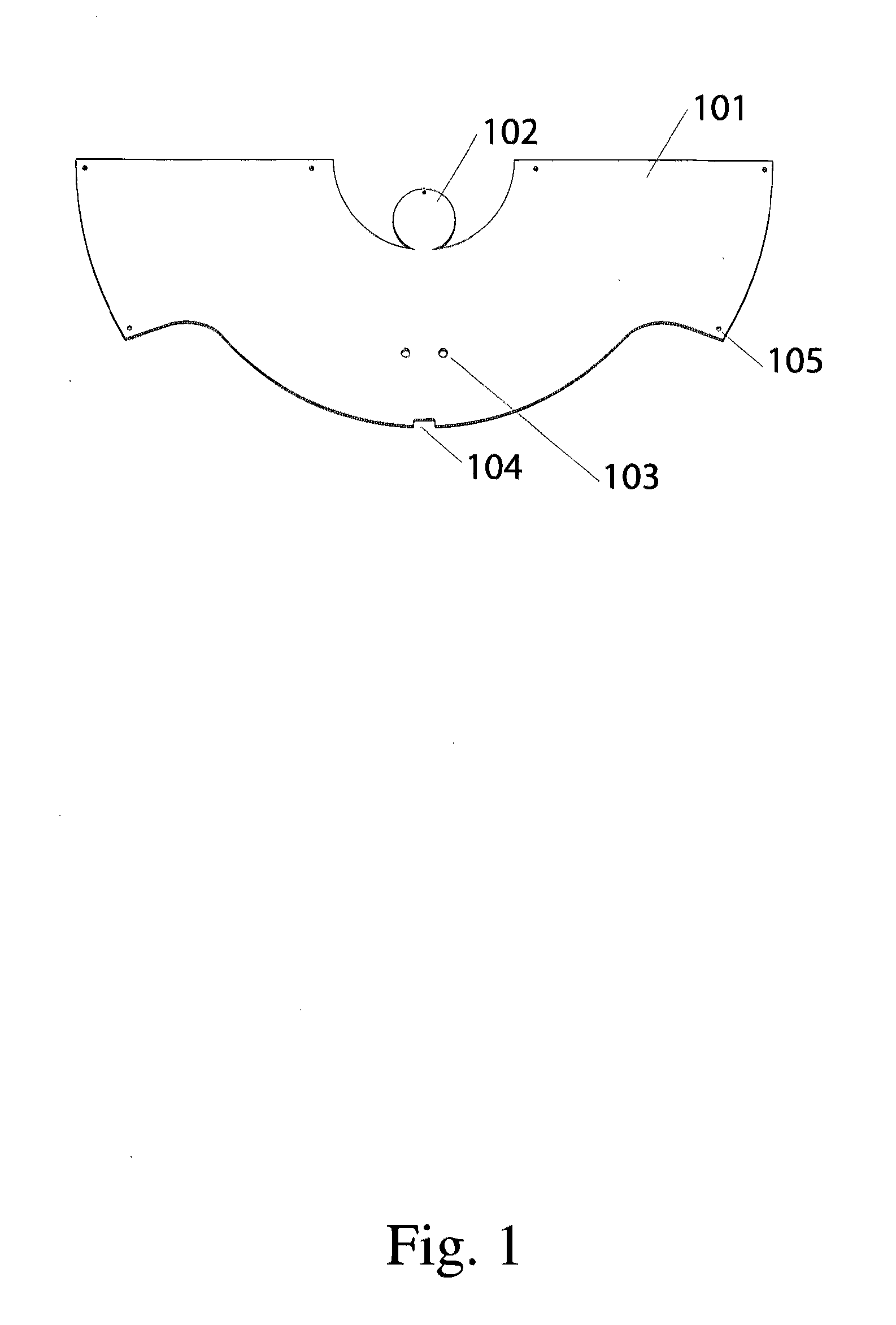

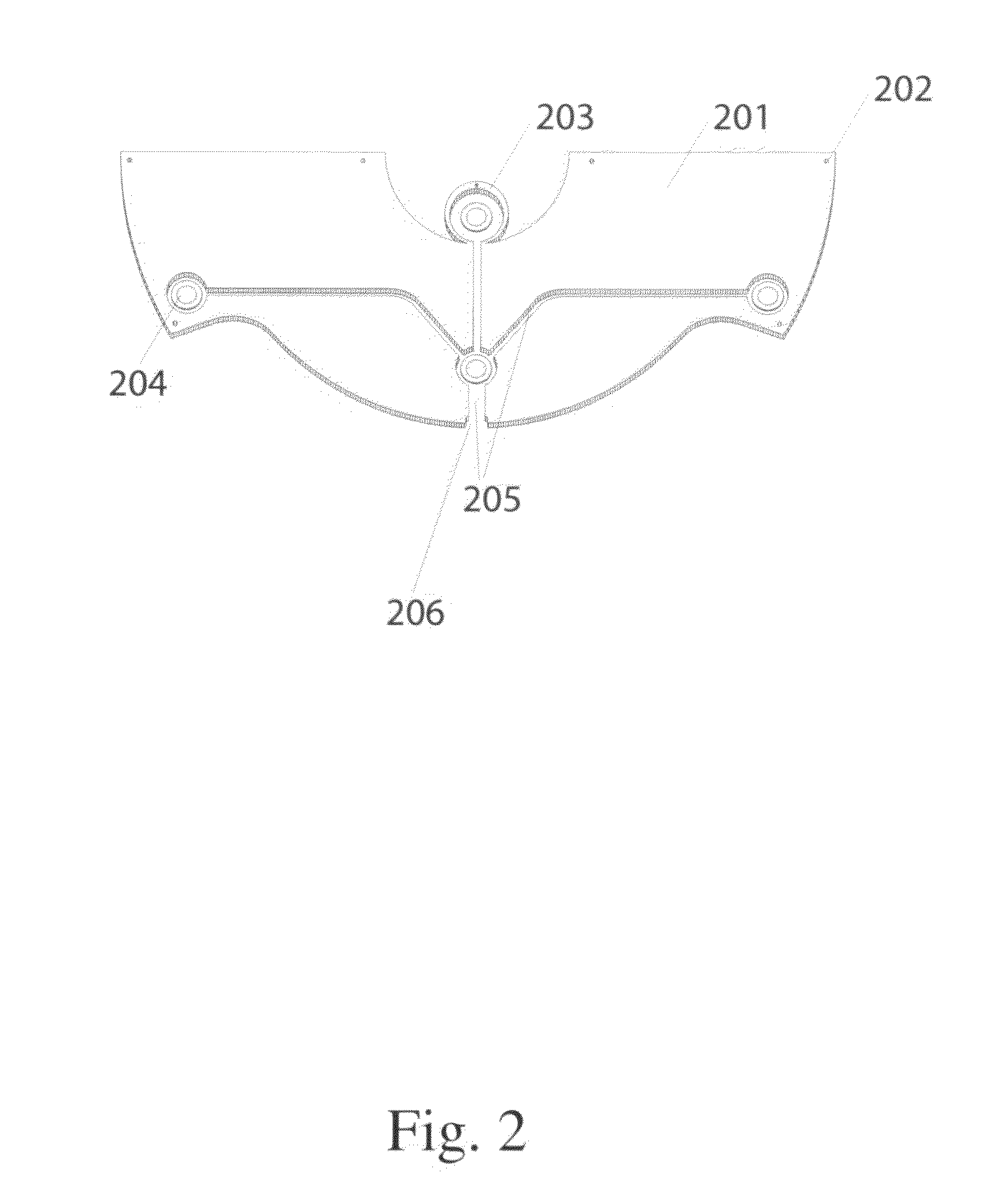

Electronic cymbal assembly with modular self-dampening triggering system

ActiveUS20120118130A1Easy maintenanceHighly accurate conversionElectrophonic musical instrumentsPercussion musical instrumentsThreaded rodClutch

The present invention includes an electronic cymbal assembly including a hi-hat clutch for mounting a hi-hat to a hi-hat stand post; a top cymbal; a self dampening trigger system attached to the underside of the top cymbal; a bottom cymbal; an input jack box mounted to the underside of the bottom cymbal; and a hi-hat cymbal mounting post. The cymbal assembly may be mounted using a magnetic ring configuration or a threaded pole configuration.

Owner:FIELD ELECTRONICS DRUMS

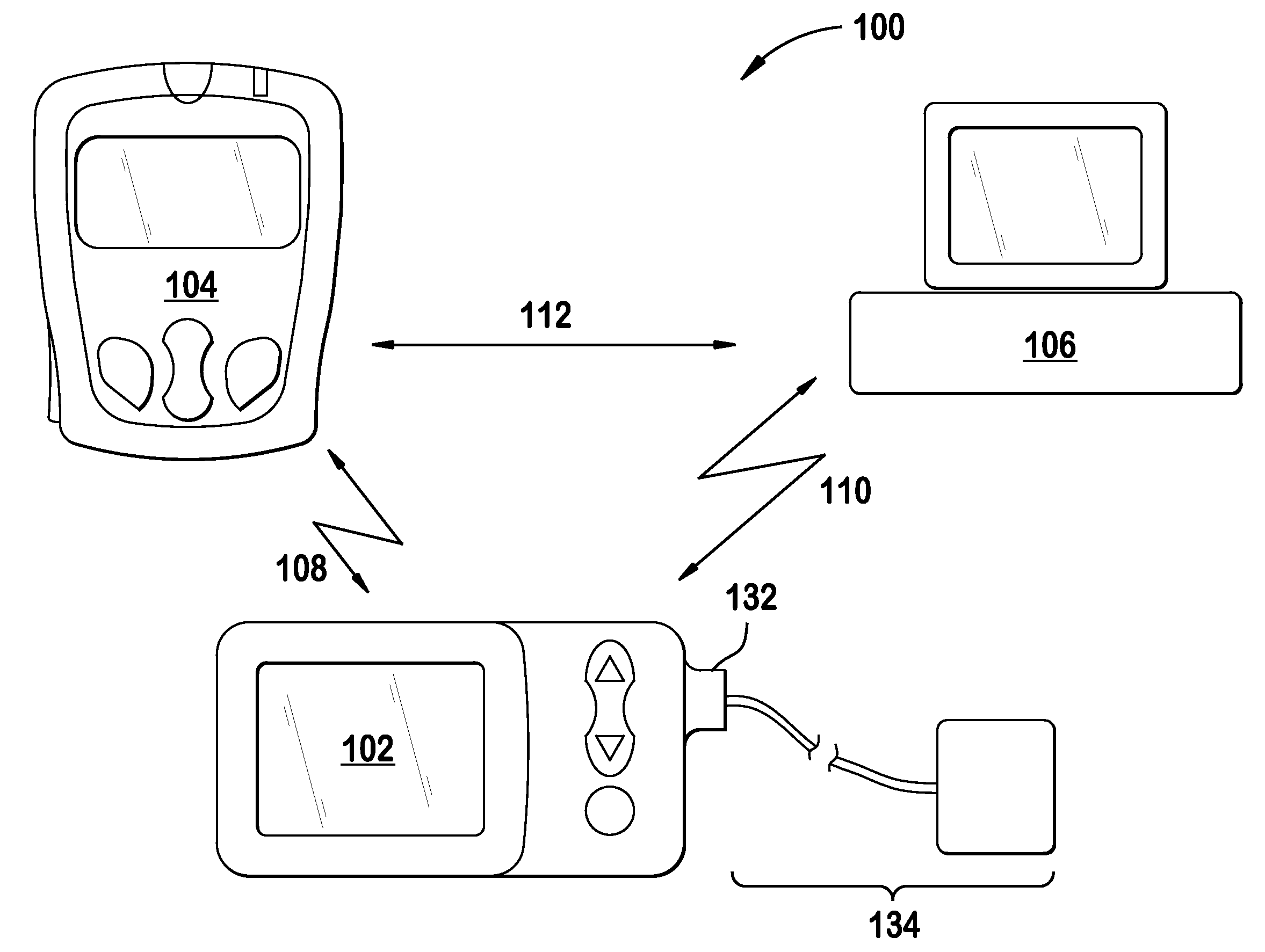

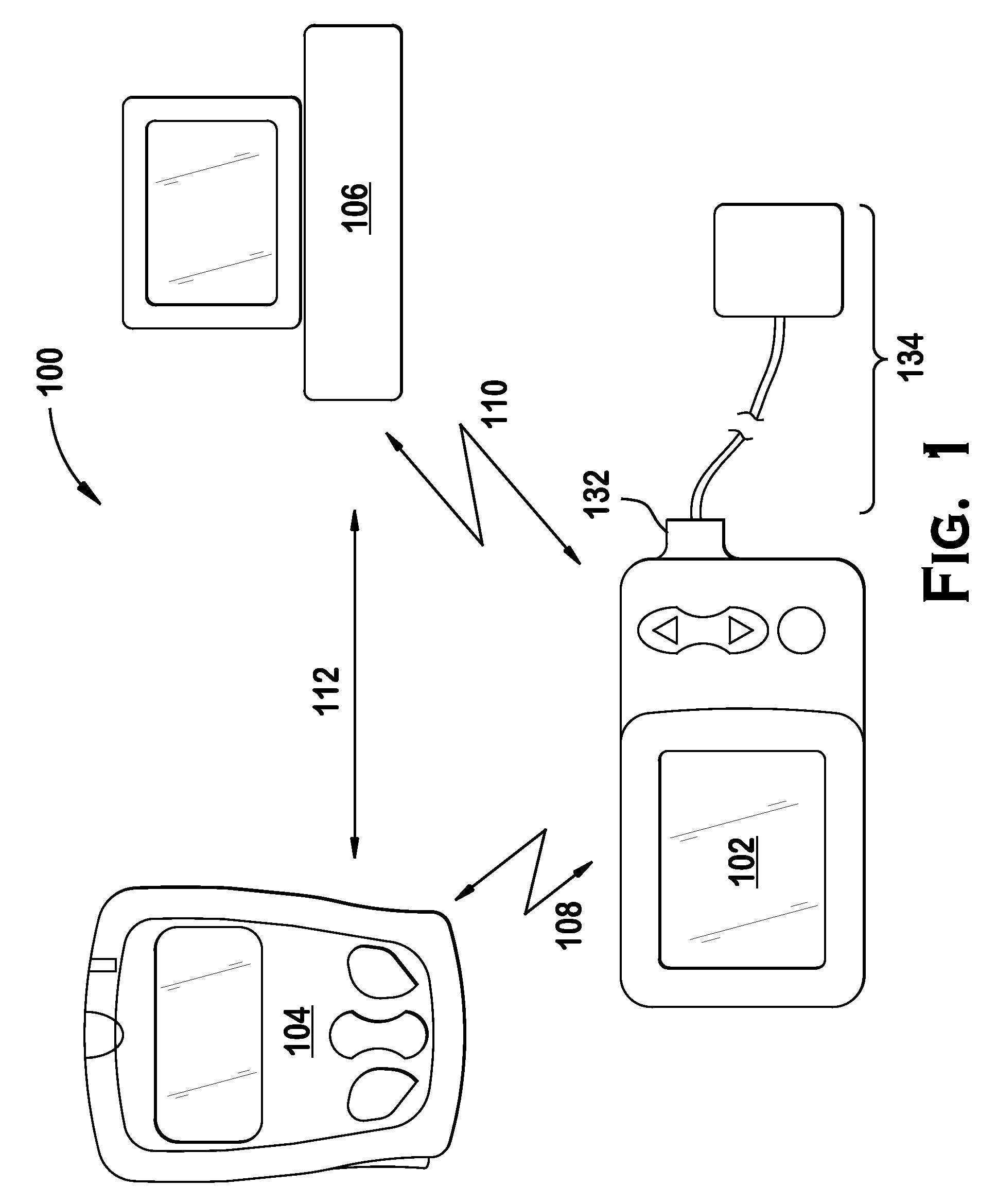

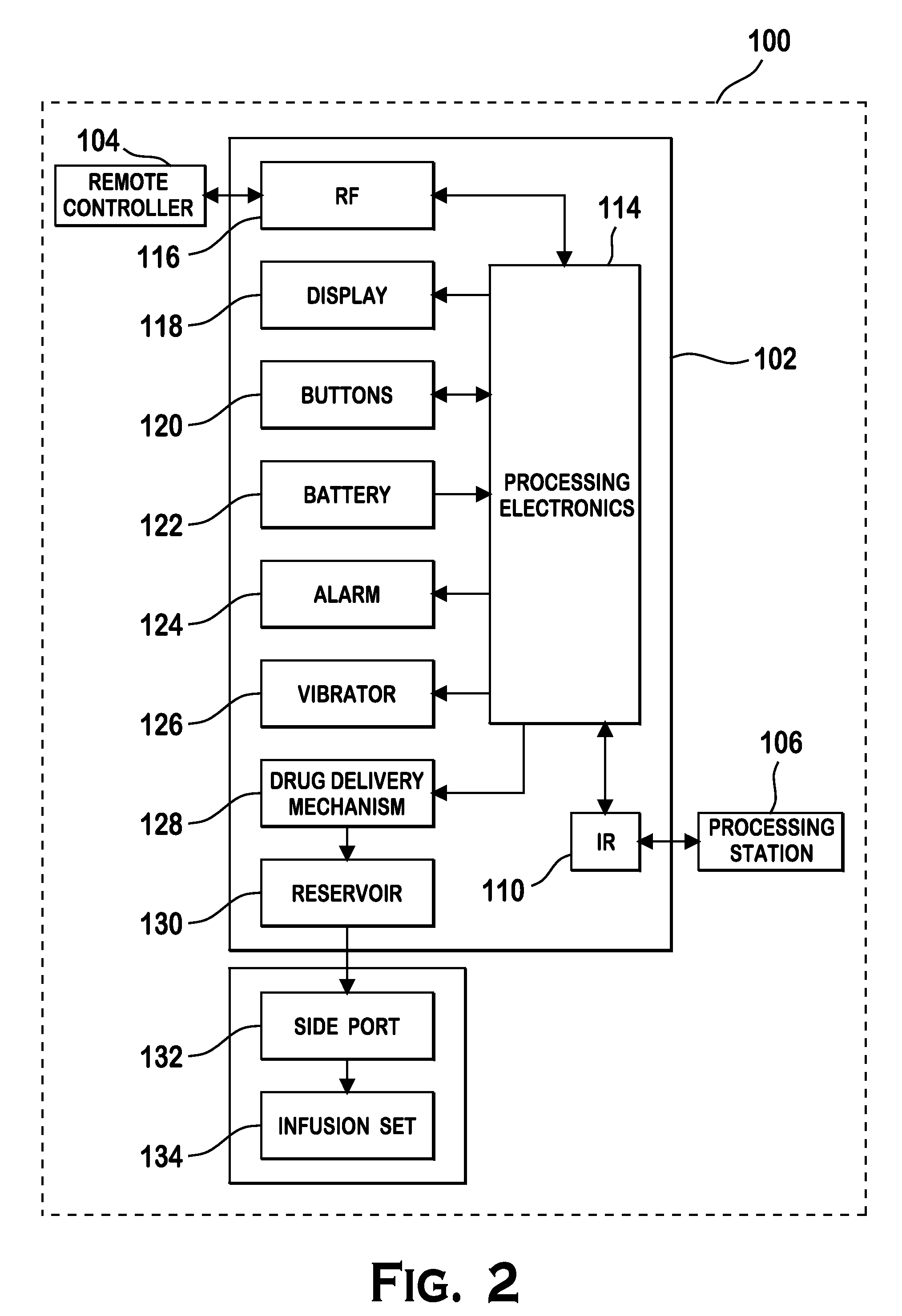

Multi-Frequency Communication System For A Drug Infusion Device

Disclosed is a medical infusion device, such as an externally worn insulin pump, capable of being in remote communication with a controller or data acquisition unit such as a blood glucose meter. The disclosed medical infusion device includes a dual frequency antenna to facilitate communication with the remote device and the antenna is mounted using a spring-design that inhibits transmission of vibration to the antenna.

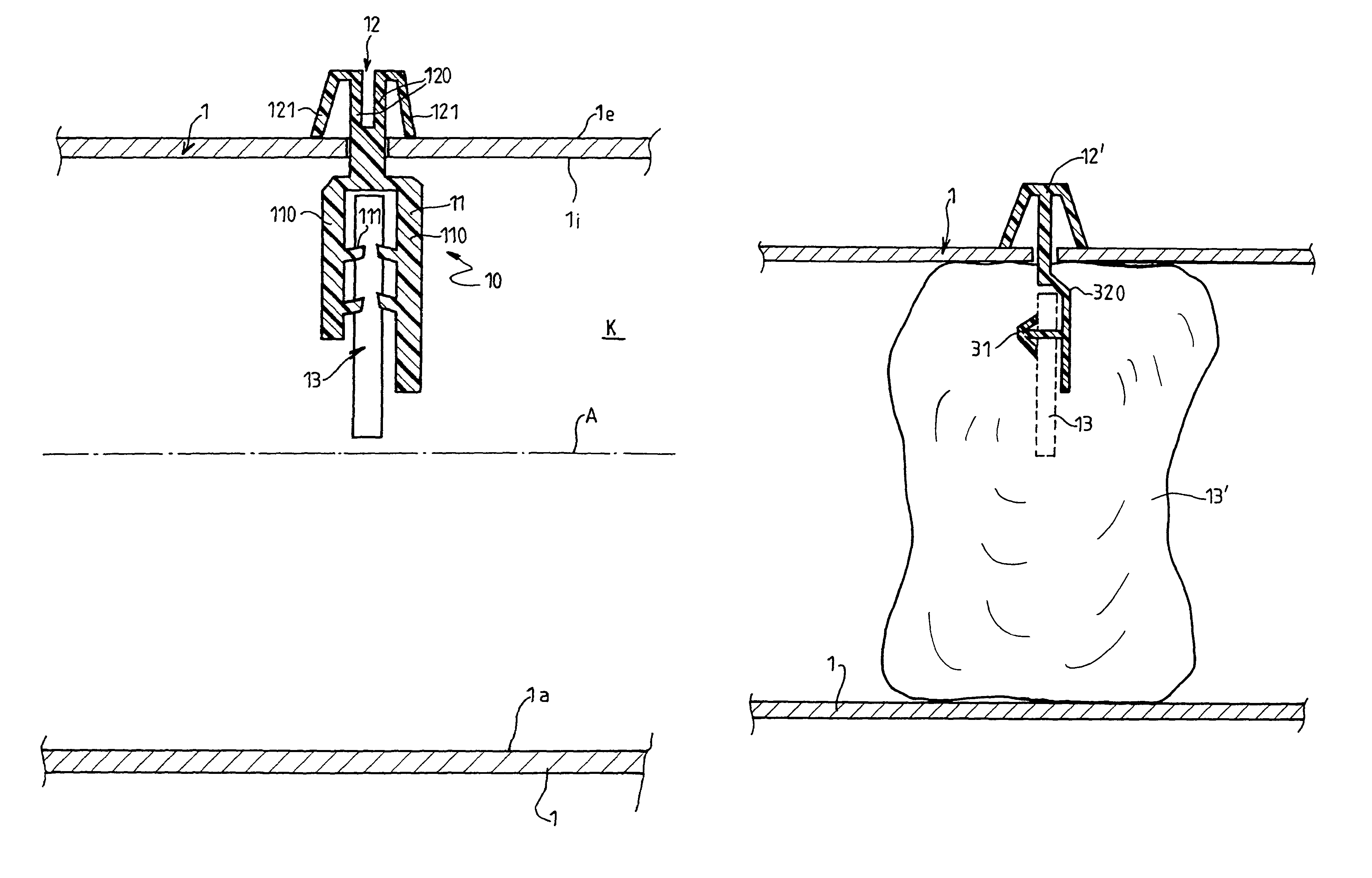

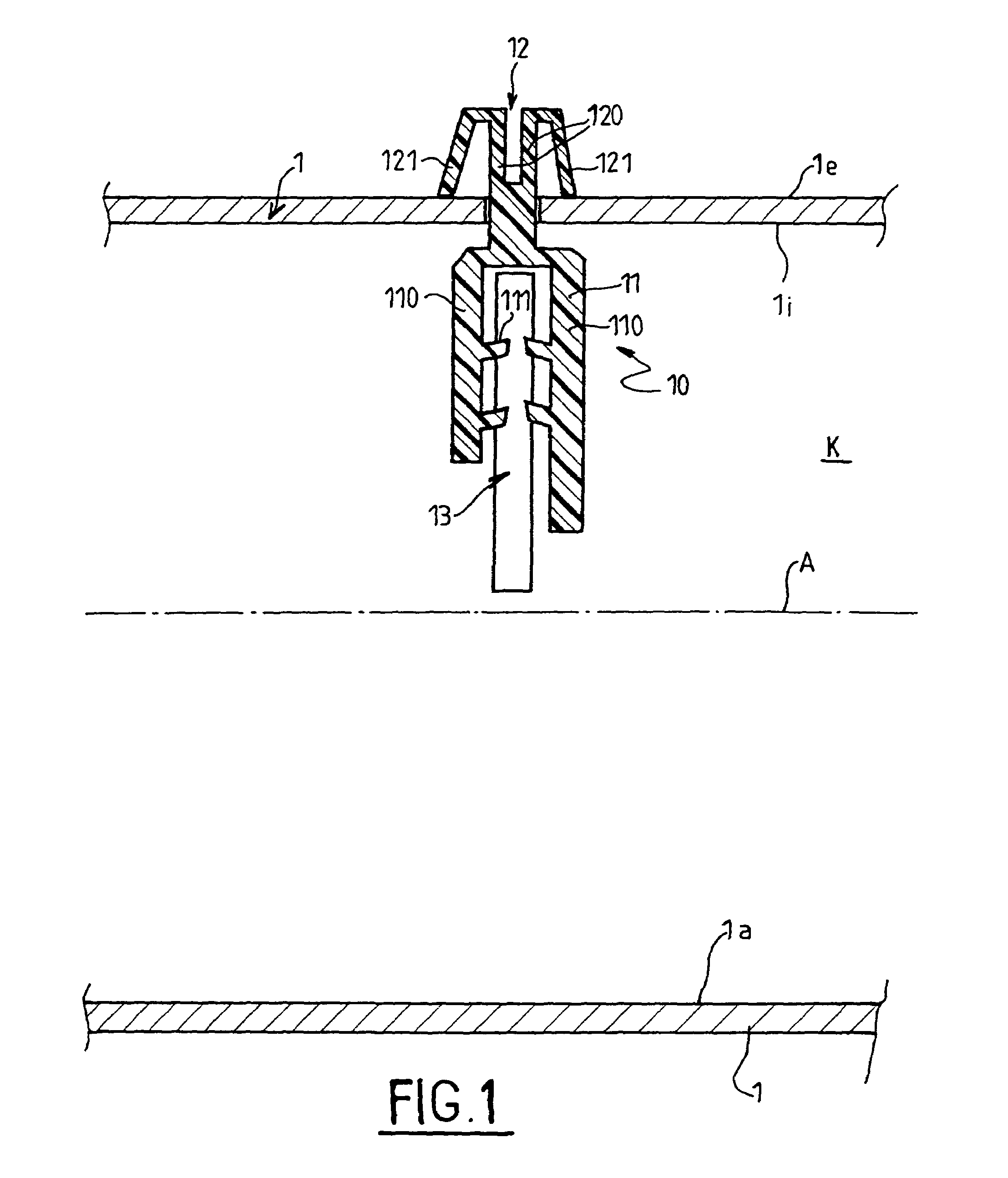

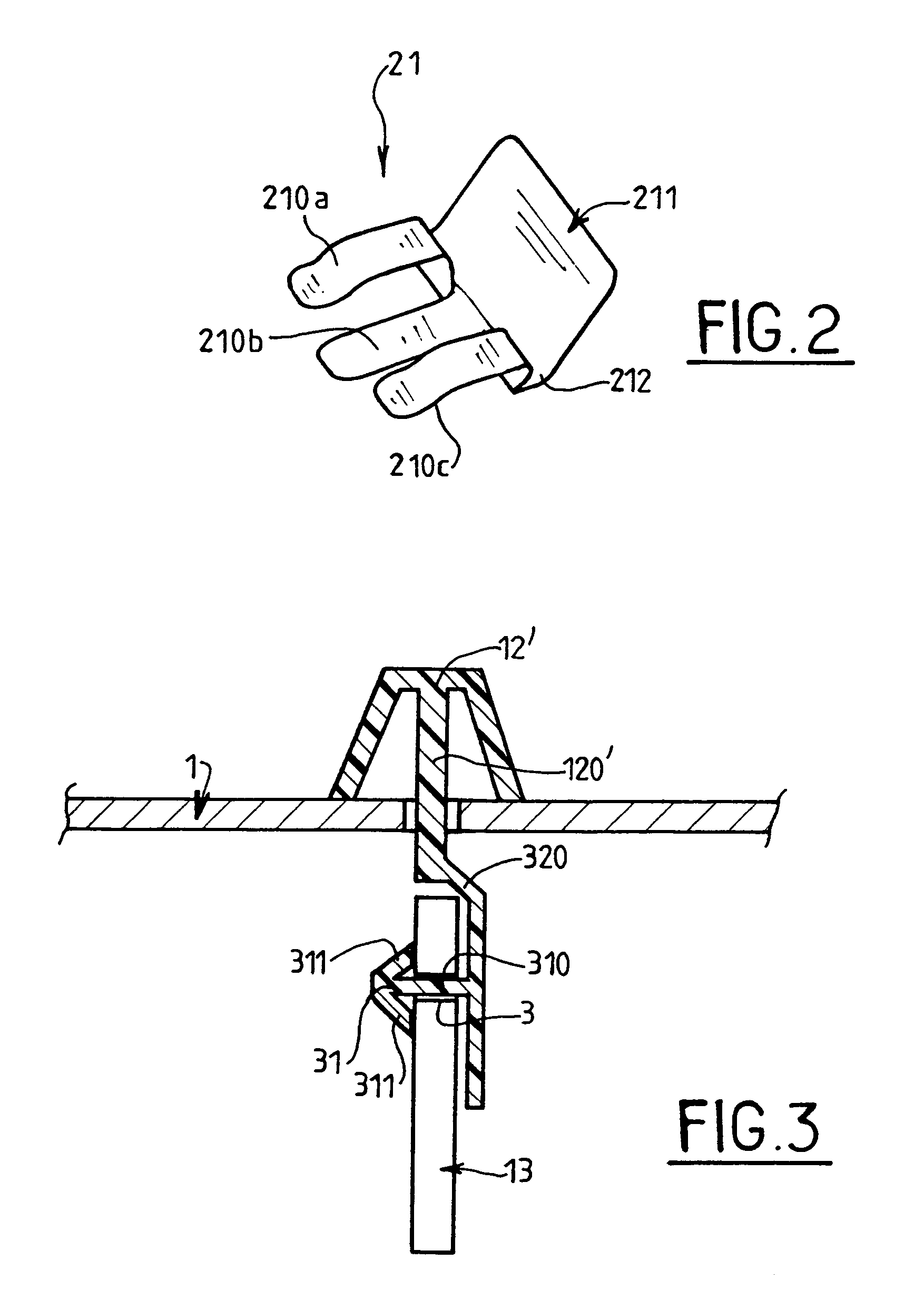

Sound insulation assembly for mounting in a tubular part, and a tubular part fitted with such assemblies, in particular a motor vehicle part

A sound insulation in tubular parts regardless of the section shape of the part, uses a piece of material that is suitable for expanding over the entire section of the section, which piece is mounted using a support suitable for fixing to the wall of the tube that is to be insulated. In a particular embodiment, a sound insulation assembly mounted in a part presenting a longitudinal direction and a tubular wall comprises a wafer that is thermally expandable to form a foam, said wafer having two parallel main faces and extending essentially along a main plane from a first wall portion towards the diametrically opposite wall portion, together with a wafer support comprising a clamp for retaining the wafer prior to expansion and coupled to fixing means in the form of a clip for fixing to the first wall portion of the part.

Owner:SEALANTS EURO SAS

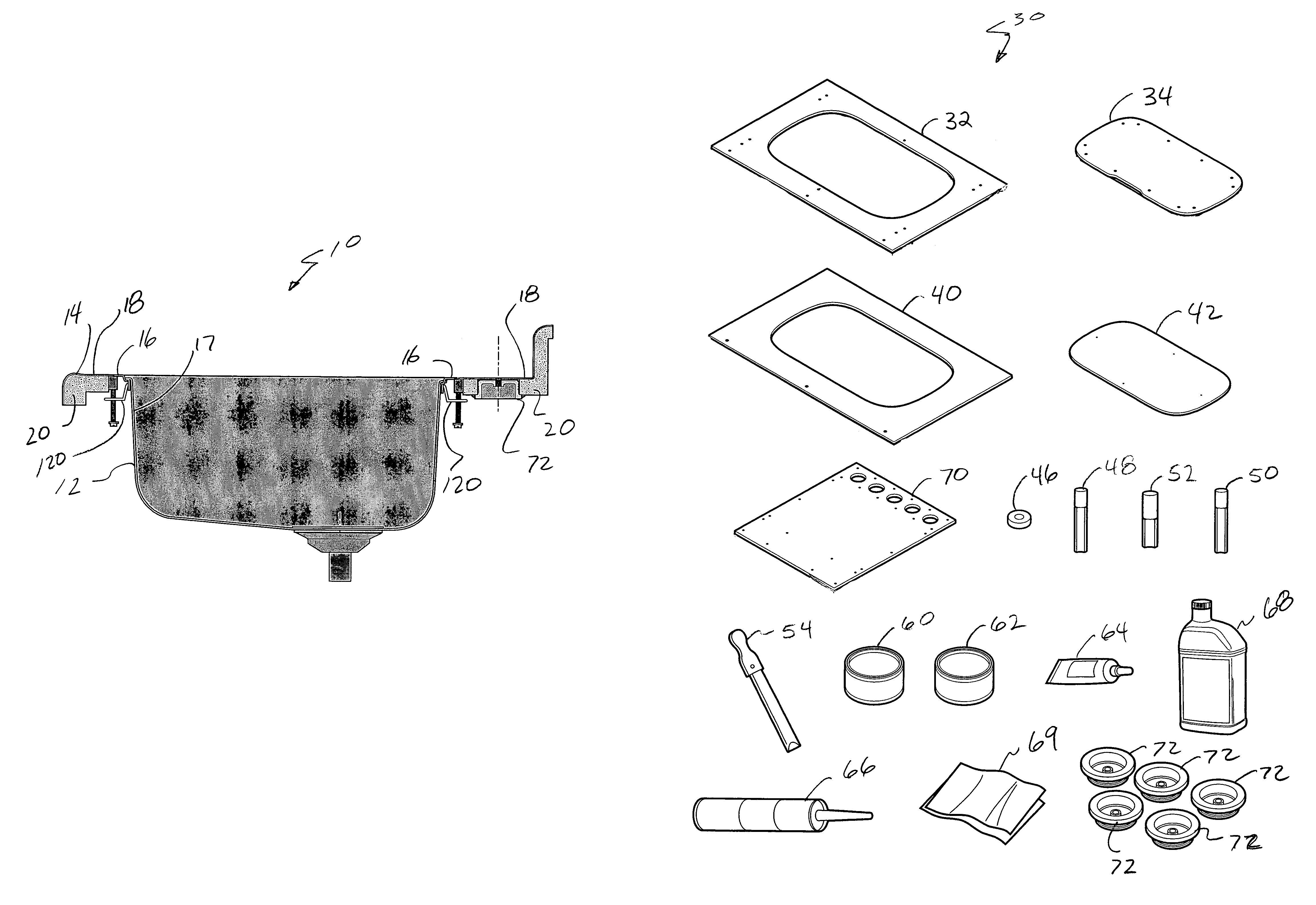

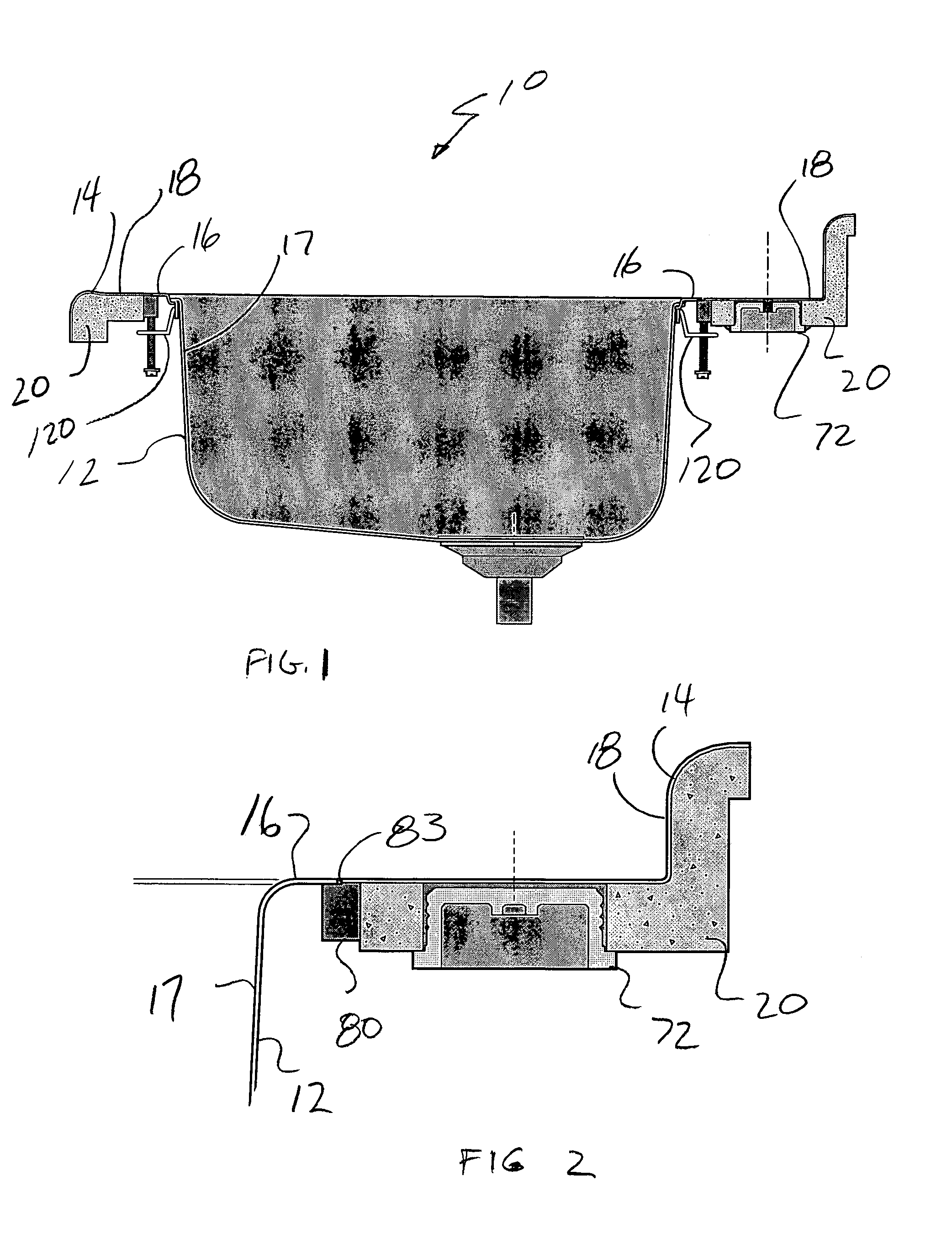

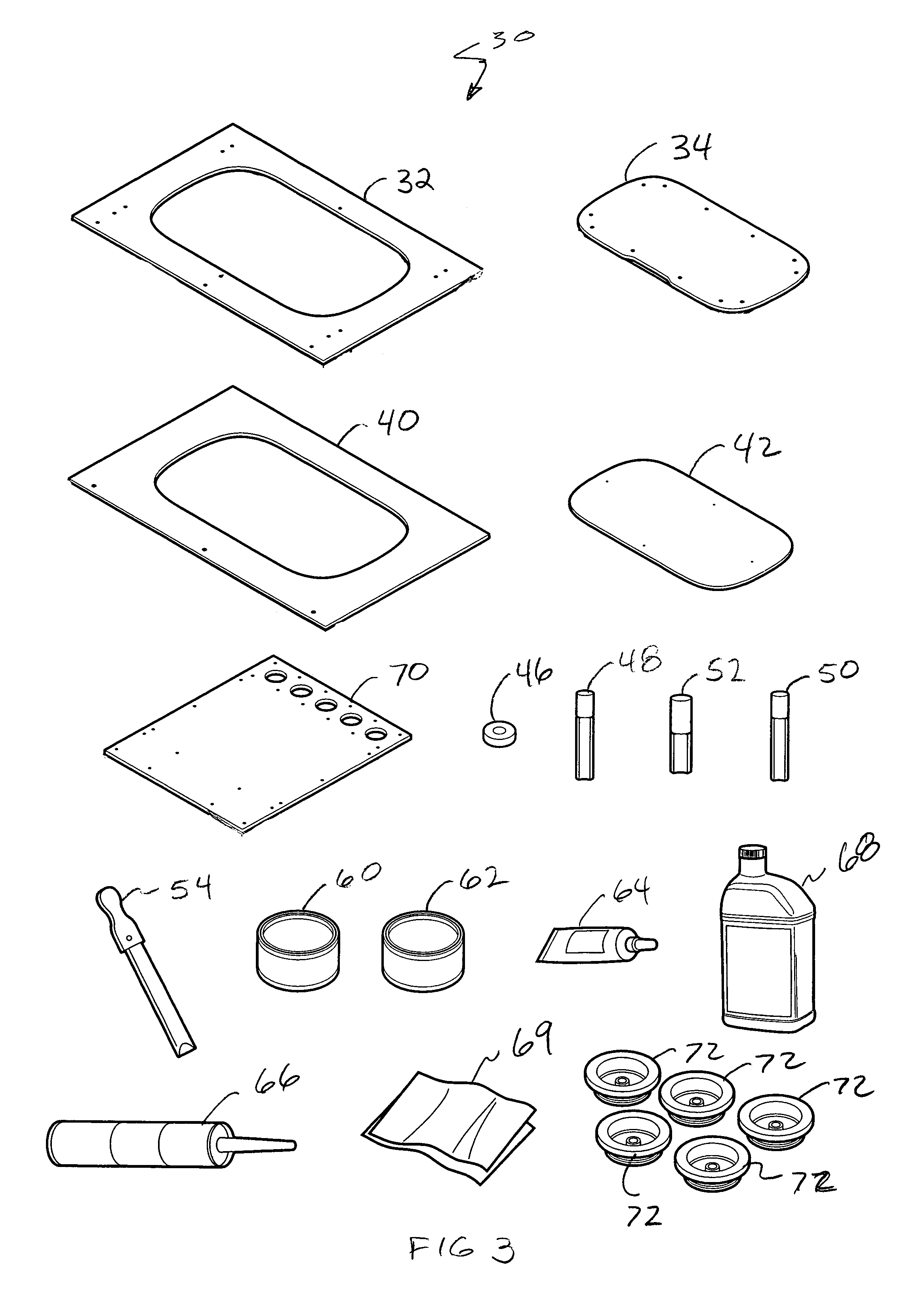

Sink/faucet flush mounting system

This invention deals with a sink having a flange can be flush mounted in a countertop where the countertop is made of a laminate upper layer supported by a wood based body such as particle board. The countertop is readied for sink mounting by ploughing out a sink channel in the supporting body of the countertop. The sink channel is filled with a hardenable plastic such as an epoxy. The upper surface of the epoxy and the laminate is machined such as by a router to create a rabbet to accommodate the flange of the sink. The sink channel is arranged so that the hardened epoxy extends under the laminate so that any water which passes under the flange of the sink will contact the epoxy and not the wood based structure. A faucet having holes to accommodate hot water, cold water, spigot and faucet accessories can be mounted using the same channel and epoxy system.

Owner:FRANKE TECH & TRADEMARK LTD

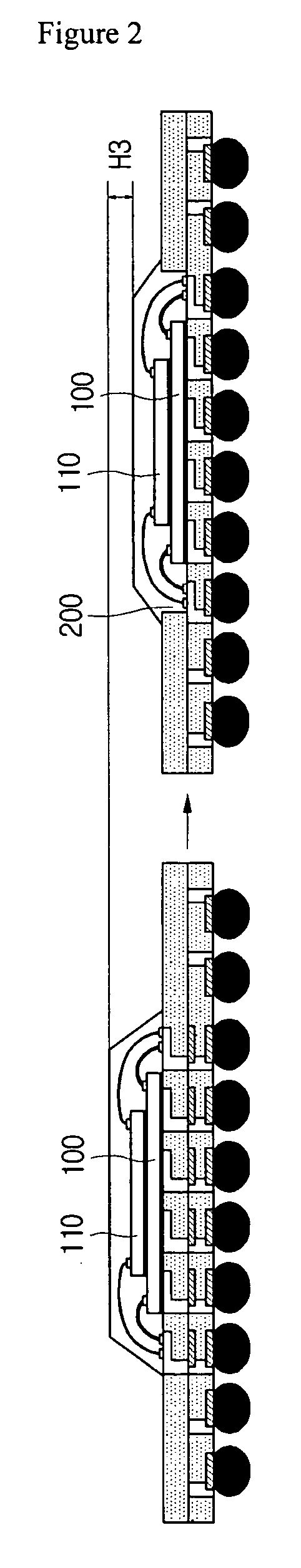

Rigid-flexible printed circuit board for package on package and manufacturing method

InactiveUS20070059918A1Package thickness is lowBoard warpageSemiconductor/solid-state device detailsPrinted circuit aspectsSemiconductor chipEngineering

The present invention relates to a rigid-flexible multi-layer printed circuit board comprising: a flexible substrate of which circuits are formed on both sides and which is bendable; a rigid substrate which is laminated on the flexible substrate and circuits are formed on both sides and a cavity within which a semiconductor chip is mounted is formed; and a bonding sheet adhering the flexible substrate and the rigid substrate and having a insulating property. According the present invention, when the same numbers of the semiconductor chips are mounted or the POP is embodied, the whole thickness of the package can be lower. Also, two more semiconductor chips can be mounted using the space as the thickness of the core layer, and the structure impossible when the number of semiconductor chip mounted on the bottom substrate becomes two from one in conventional technology can be embodied.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

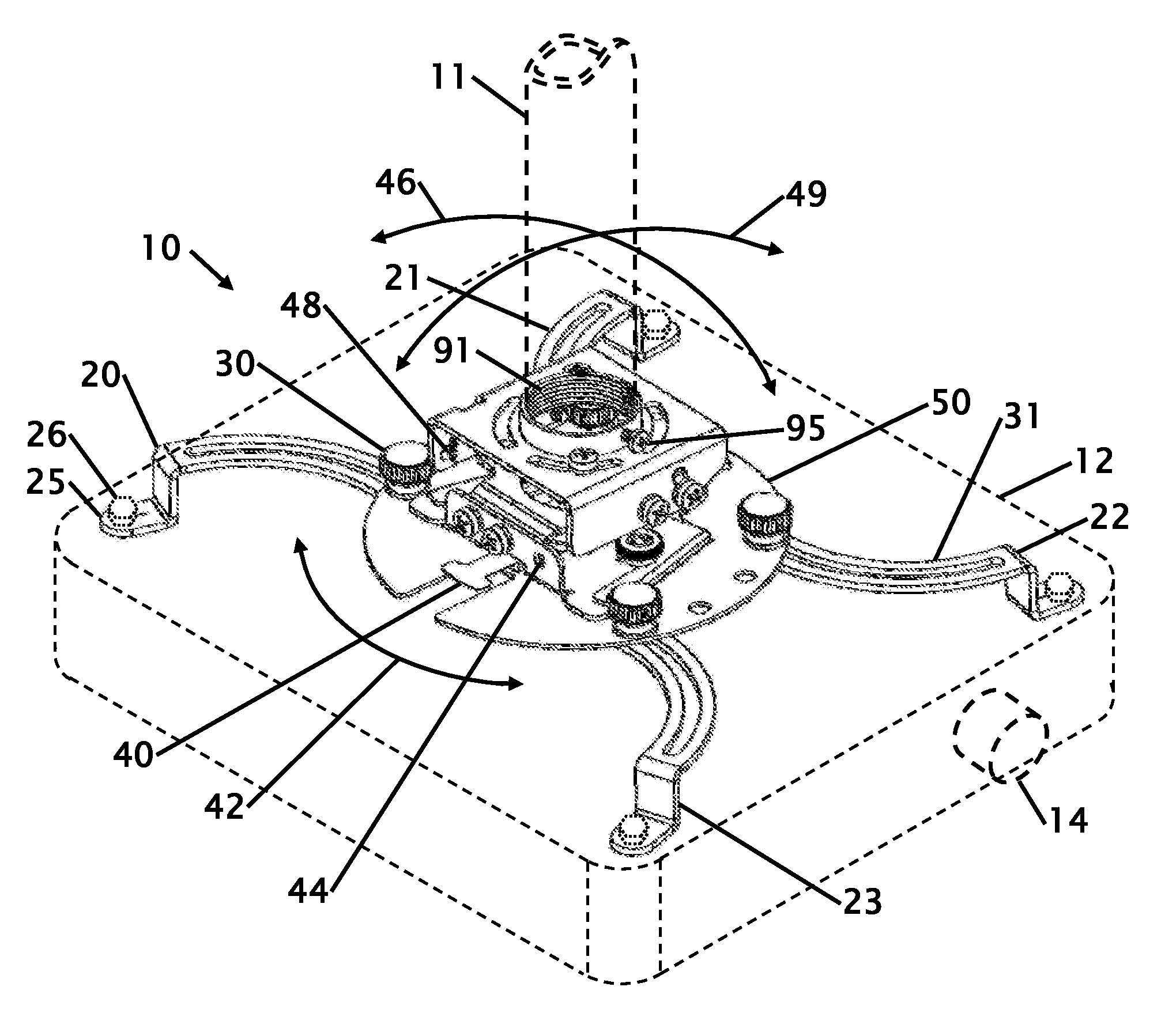

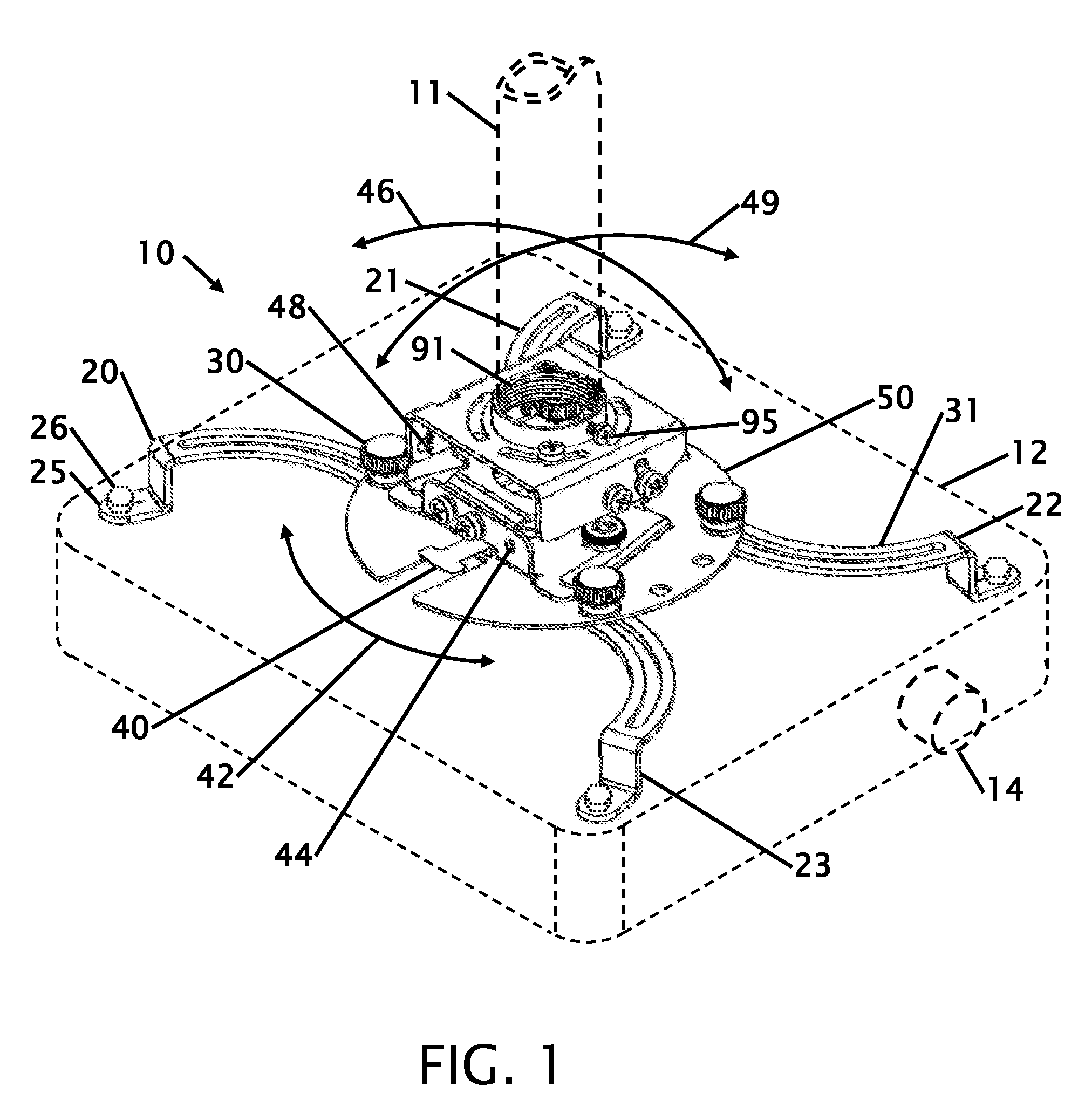

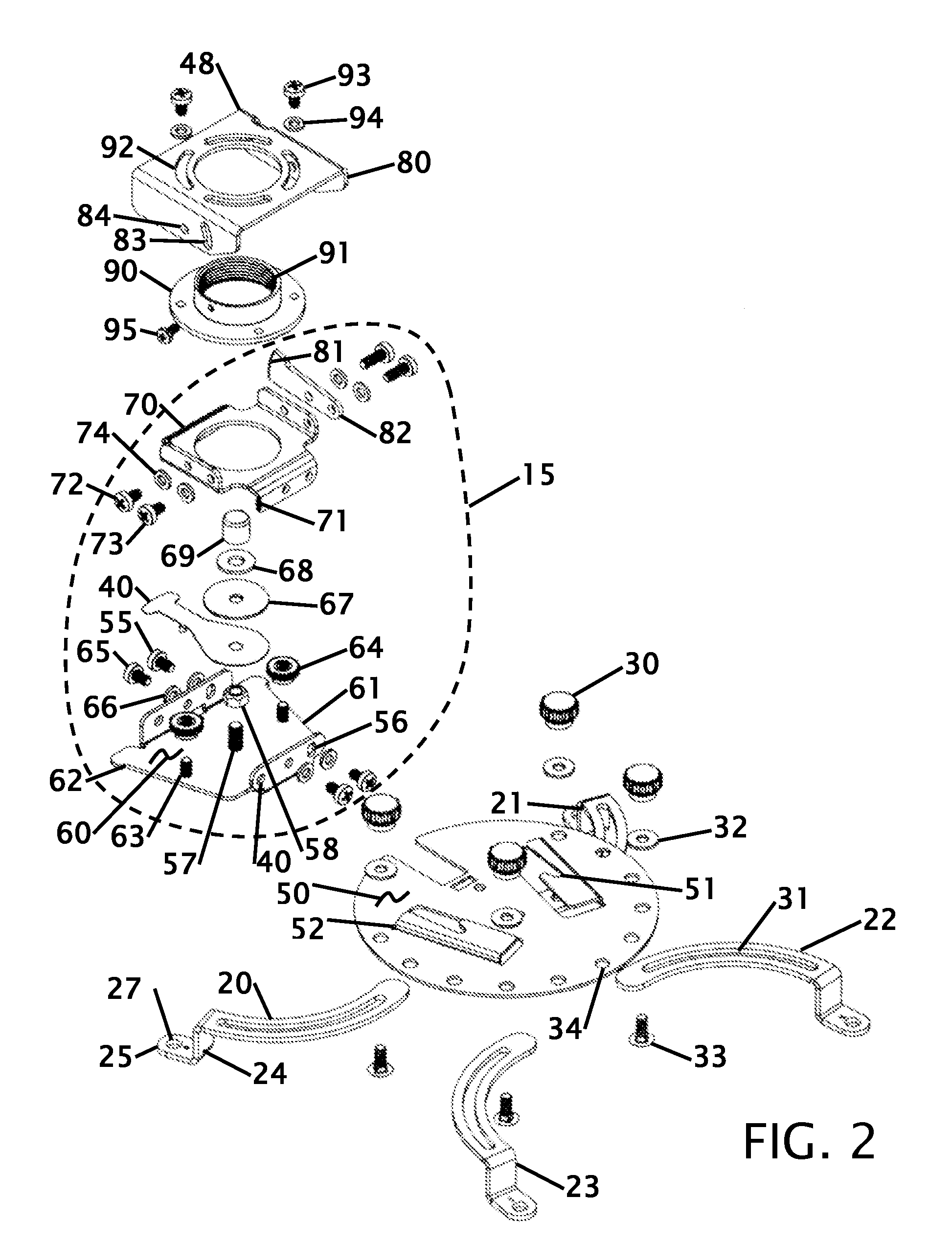

Projector mount with phillips screw driver angle adjustment

InactiveUS20090294619A1Low costReduce manufacturing costPortable framesCandle holdersRotational axisGear wheel

Improvements in a mount for attaching a television of projector to an overhead or ground structure is disclosed. The mount allows for spin, side to side and front to back angle adjustment. The adjustment components are formed from the present projector mount uses metal component having a rack comprising a plurality of formed teeth that are engageable in the recessed side of a crosshead screwdriver that is trademarked as a Phillips screwdriver. The recesses of the crosshead screwdriver act as a pinion gear in the rack to adjust the mounted angle of a projector on the projector mount. This configuration reduces parts count, size and cost without compromising functionality. The axis of rotation of both the side-to-side and front-to-back pass through the projector mount.

Owner:SPECIALTY FINANCE

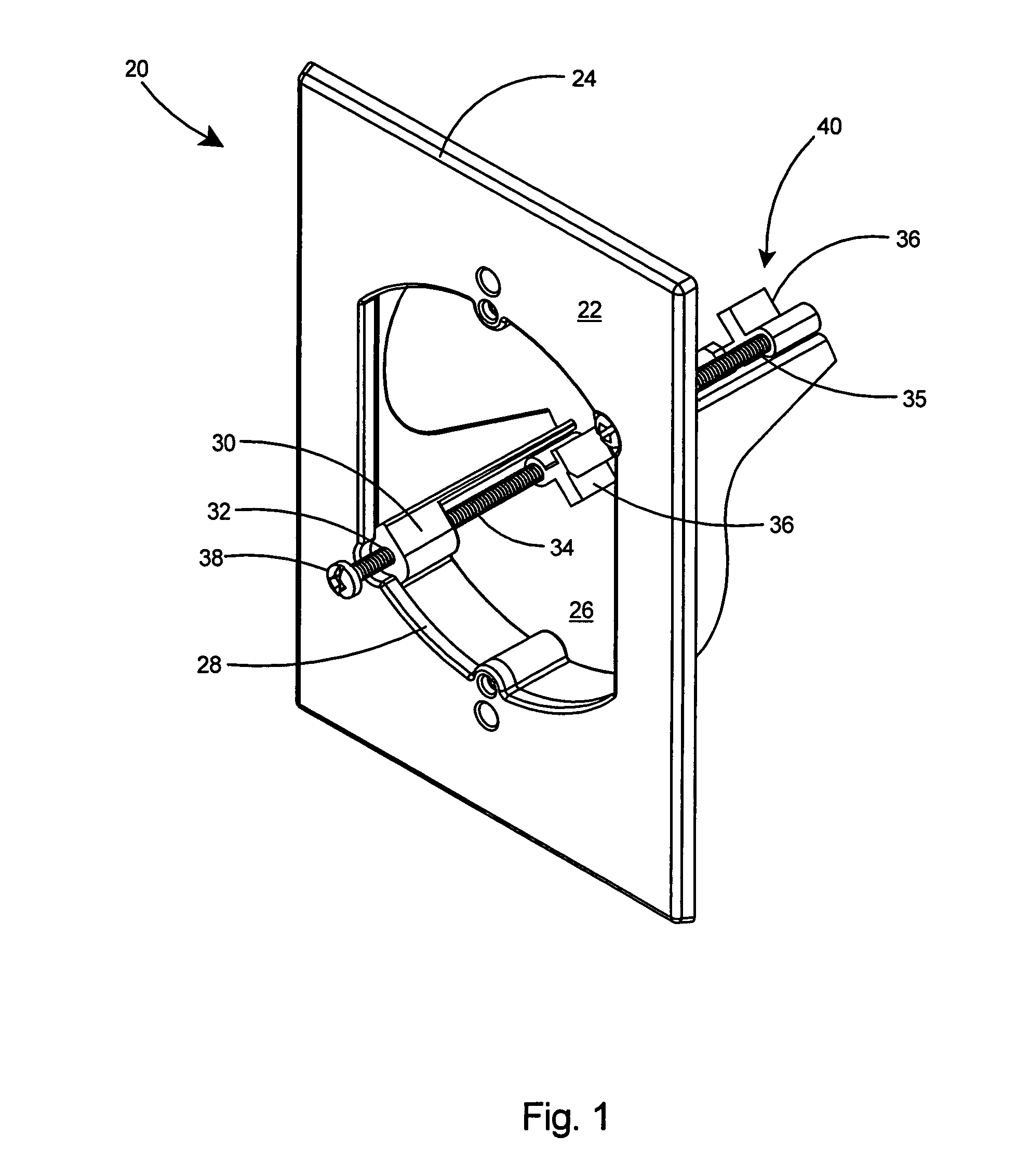

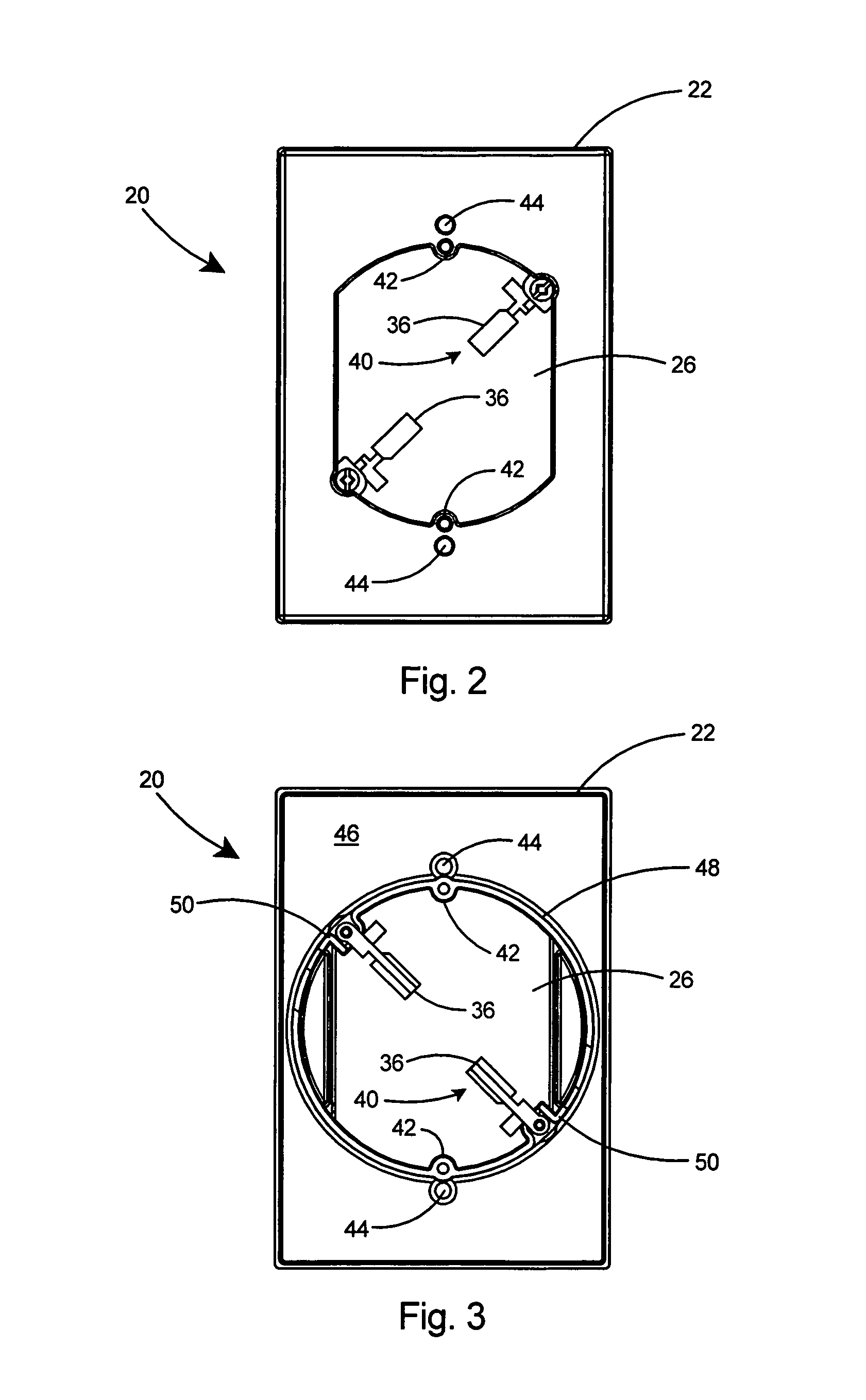

Two gang electrical box for rapid mounting using hole saw

ActiveUS8445779B1Amount of timeSubstation/switching arrangement detailsMachine supportsHole sawEngineering

A two gang electrical box that greatly reduces the time and effort required to mount one or two electrical components to a wall or similar surface. Wall preparation requires only the use of a standard hole saw thereby greatly minimizing installation time. The two gang electrical box includes a plate with an opening therein and a substantially circular sidewall extending from the plate at the periphery of the opening and terminating in a rear wall. Mounting fasteners extending through the plate include clamp arms thereon for securing the electrical box to a wall. The clamp arms can be rotated to either an inward position or an outward position. The sidewall is provided with open areas or recesses to fully accommodate the clamp arms when rotated to the inward position thereby enabling the peripheral wall and clamp arms to pass easily within the wall opening created by the standard size hole-saw.

Owner:ARLINGTON INDS

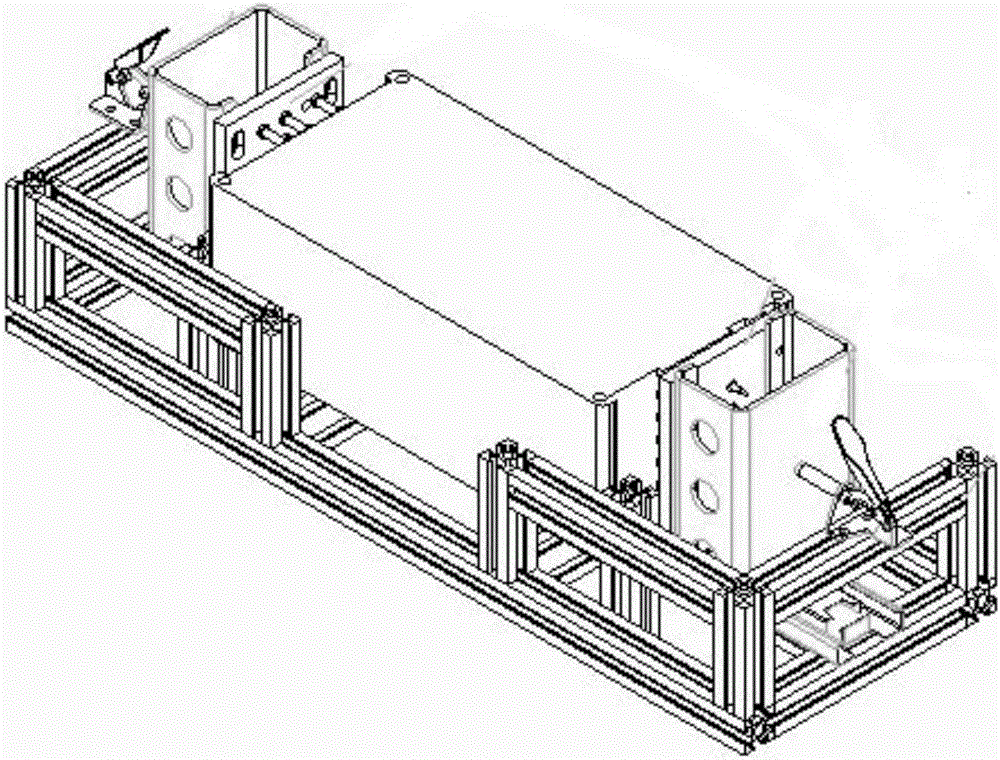

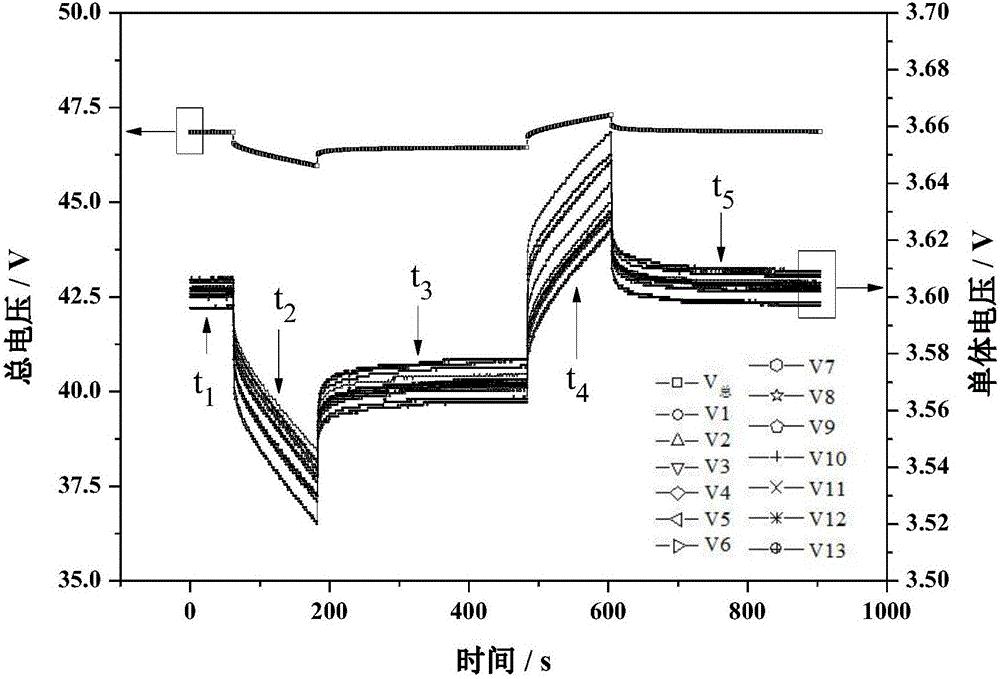

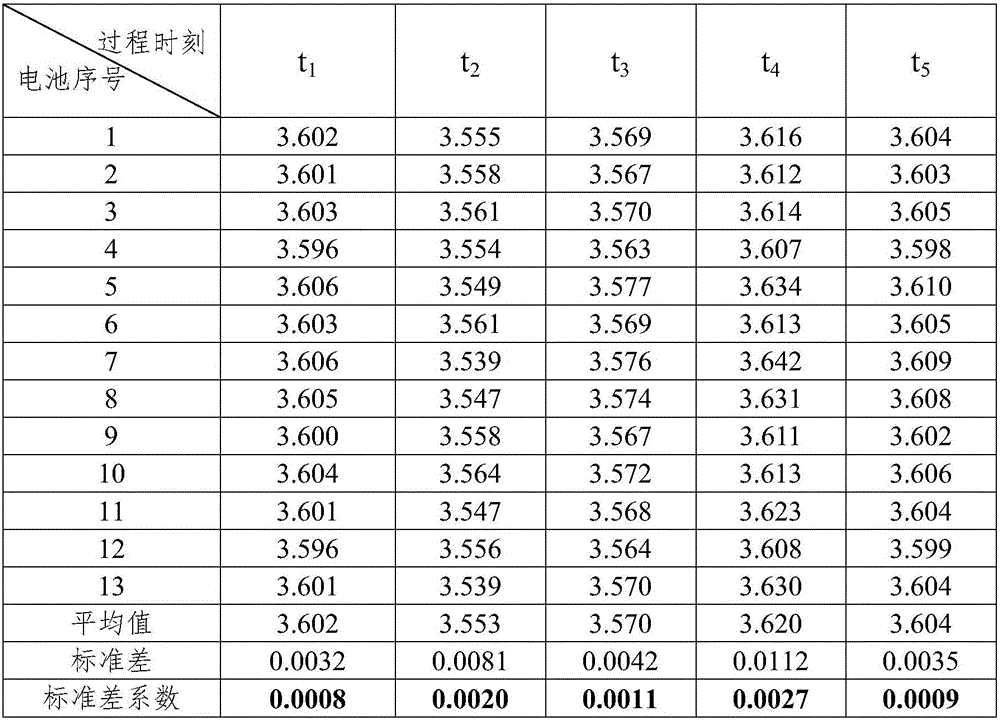

Method for detecting consistency of single battery in storage battery

InactiveCN106772085AEnsure consistencyImprove consistencyElectrical testingElectrical batteryVoltage range

The invention provides a method for detecting consistency of a single battery in storage battery. The method comprises the following steps: forming the storage battery by serially and / or parallelly connecting multiple single batteries; and in the discharging process of the storage battery, to obtain one or more of the data of the voltage range of each single battery in the storage battery, the voltage relative range and the voltage standard deviation of each single battery, and comparing the obtained statistics value for expressing the consistency of the single battery in the storage battery with the threshold value, and dynamically detecting the consistency of the storage battery in the quality testing process. The provided method is capable of, through setting the different charging-discharging systems in the quality testing process, detecting the consistency level of the internal single battery in the storage battery under the appointed use conditions. Through the quality testing by the system, the expression data of the consistency of the storage battery out of a factory is more convincing, and the consistency of the actual vehicle-mounted using process is more effectively guaranteed.

Owner:CHINA AUTOMOTIVE BATTERY RES INST CO LTD

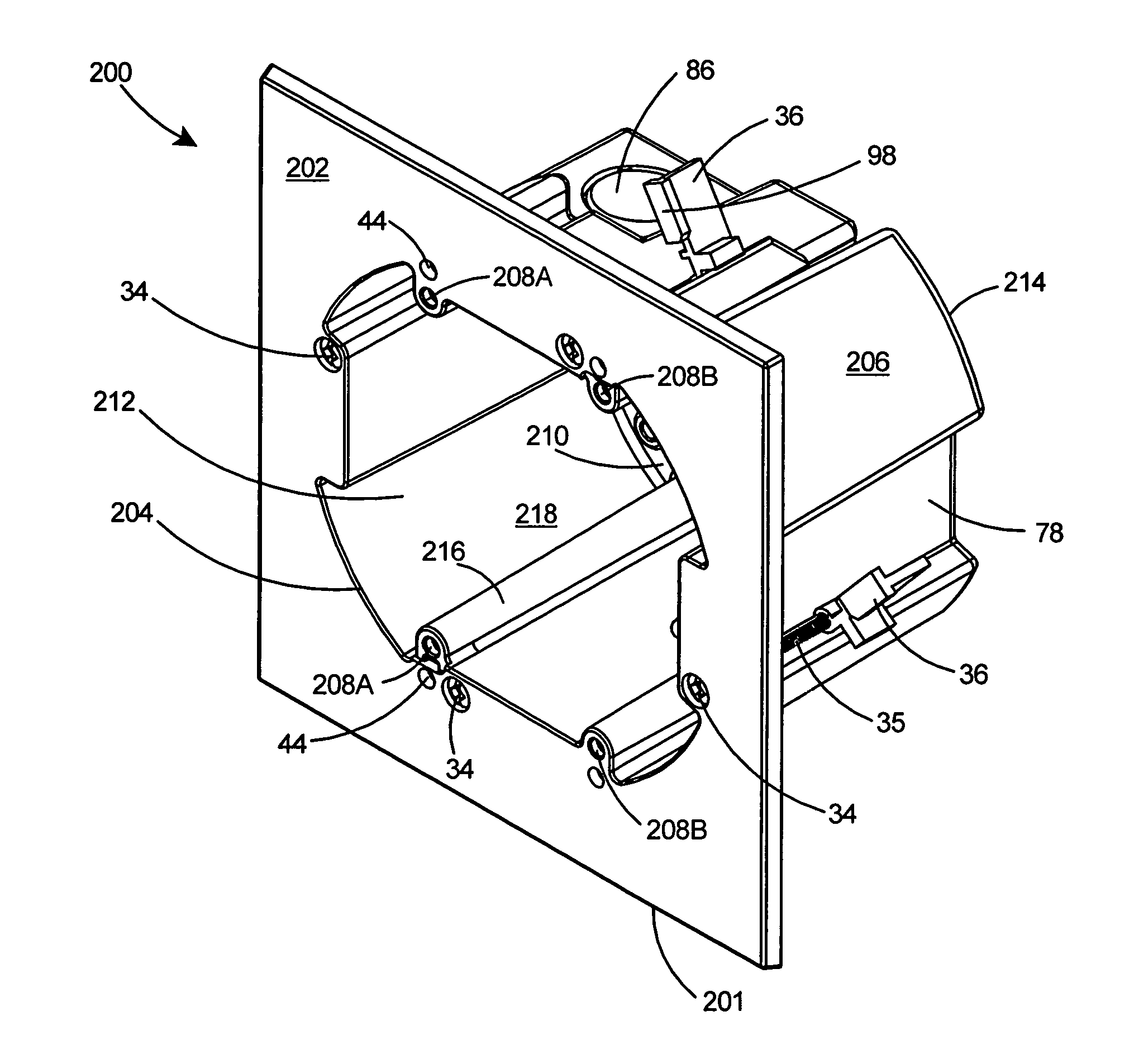

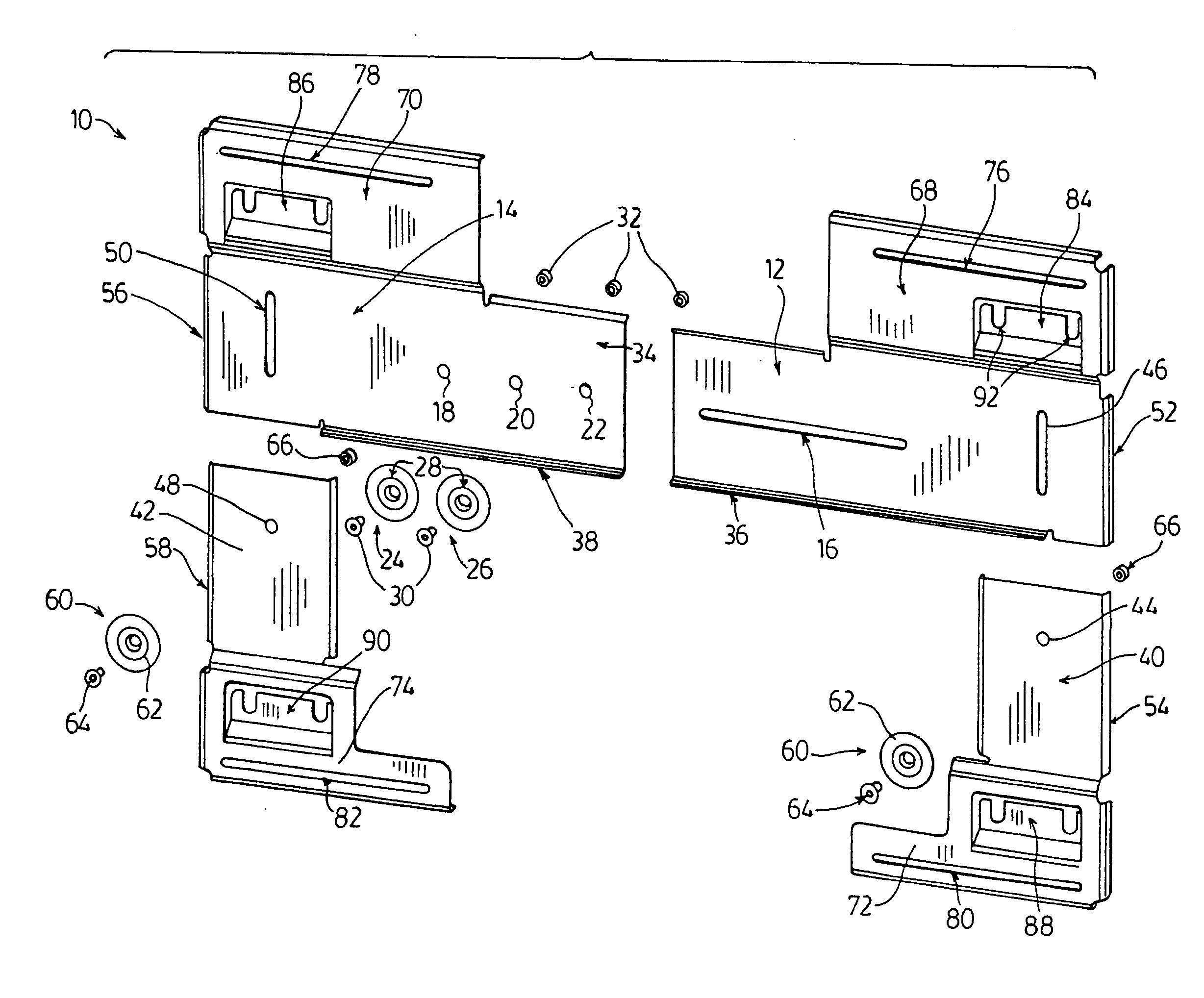

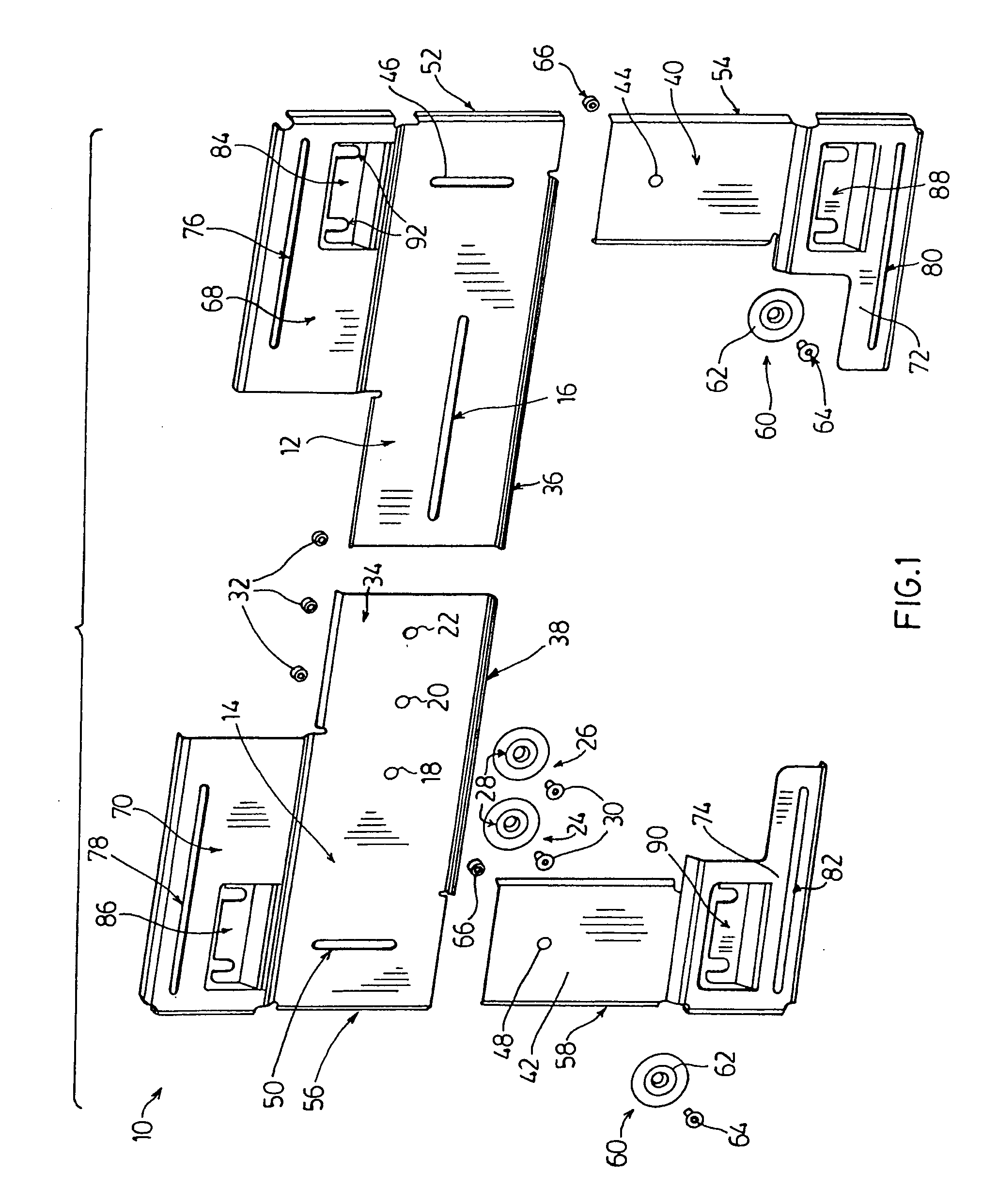

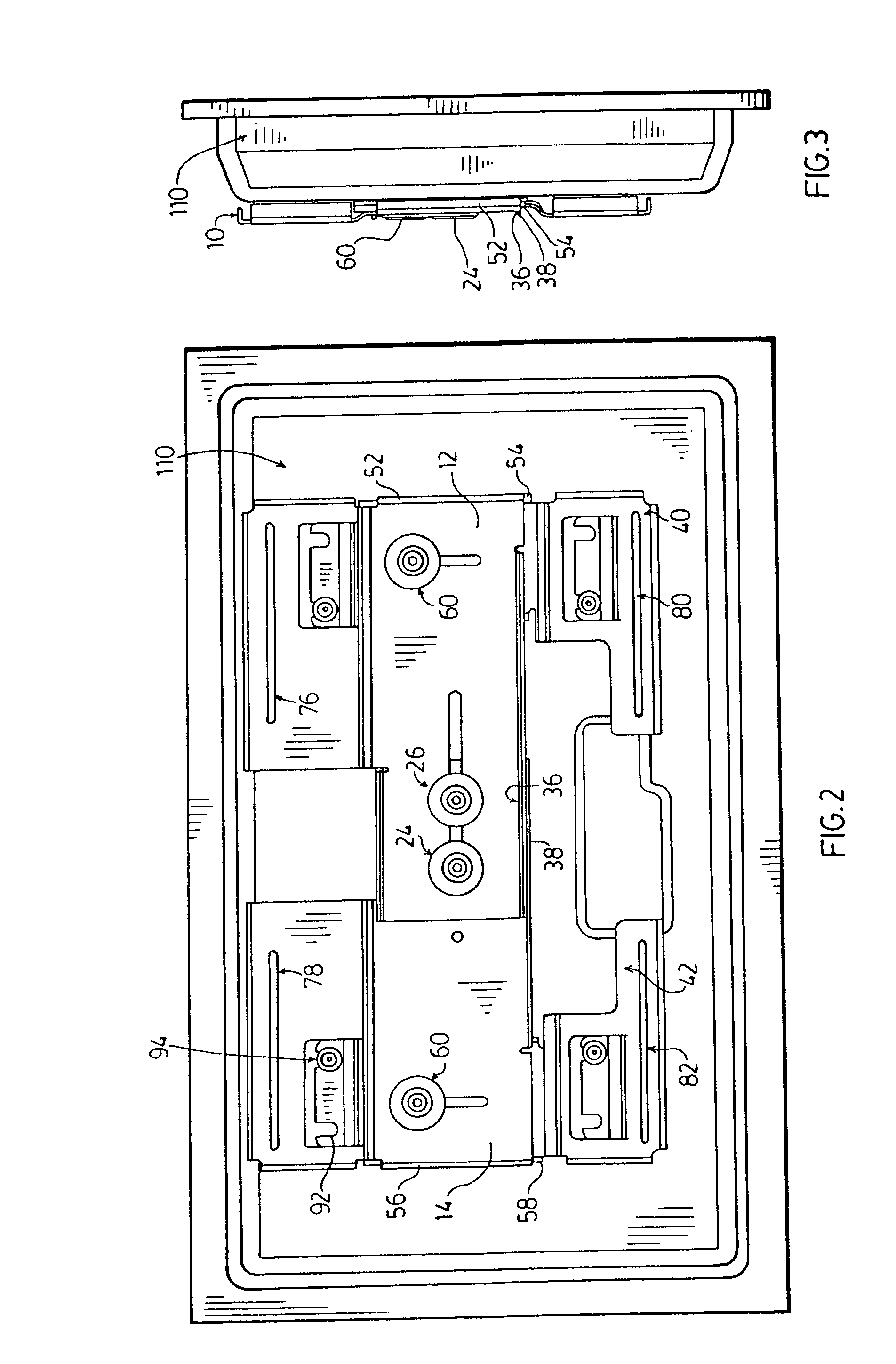

System for Displaying Photographs

A system for displaying photographs is disclosed. The system includes one or more horizontal members or bars that are secured to a wall, such as a wall of a house. The horizontal members are preferably immovably secured, as by wall anchors or nails. The horizontal members preferably include a profile, such as a shaped, hollow cross-sectional area, that is configured to mount two or more vertical members. Two or more vertical members or bars are then secured to the horizontal members. The vertical members may be mounted using the profiles, channels, or grooves of the horizontal members. They may be mounted using a tab or a clamp, such as a spring clamp. The vertical members preferably also include continuous, vertical grooves on their sides, for placing photographs into the grooves for display.

Owner:SNAP GALLERY +1

Universal wall mount bracket for displays

InactiveUS20070018062A1Clean and professional lookTelevision system detailsCandle holdersDisplay deviceEngineering

A universal display bracket suitable for mounting one of a variety of displays on a surface. The display bracket comprises a plurality of bracket portions slidable relative to one another permitting adjustment of the bracket in both horizontal and vertical directions. The bracket portions are lockable so as to maintain fixed relative positions. The bracket is adapted to mount using suitable fasteners upon a surface and each of the bracket portions are dimensioned to support the display to be mounted. The bracket may be provided with capture locks to prevent accidental dislodgement of the display, and the bracket may be further provided with a tilt assembly allowing a display to be tilted up to 15° from vertical.

Owner:CALINESCU THEODOR

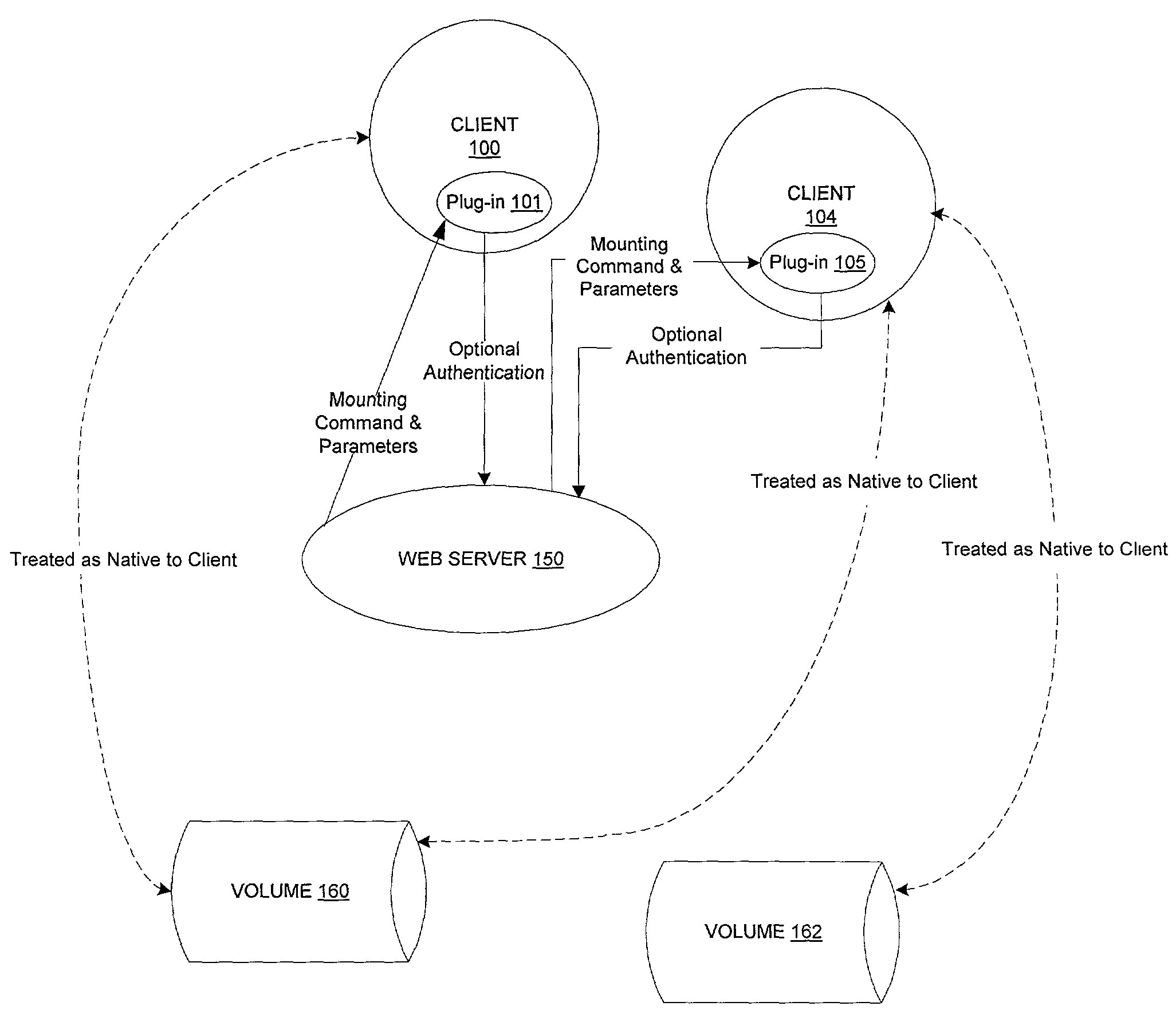

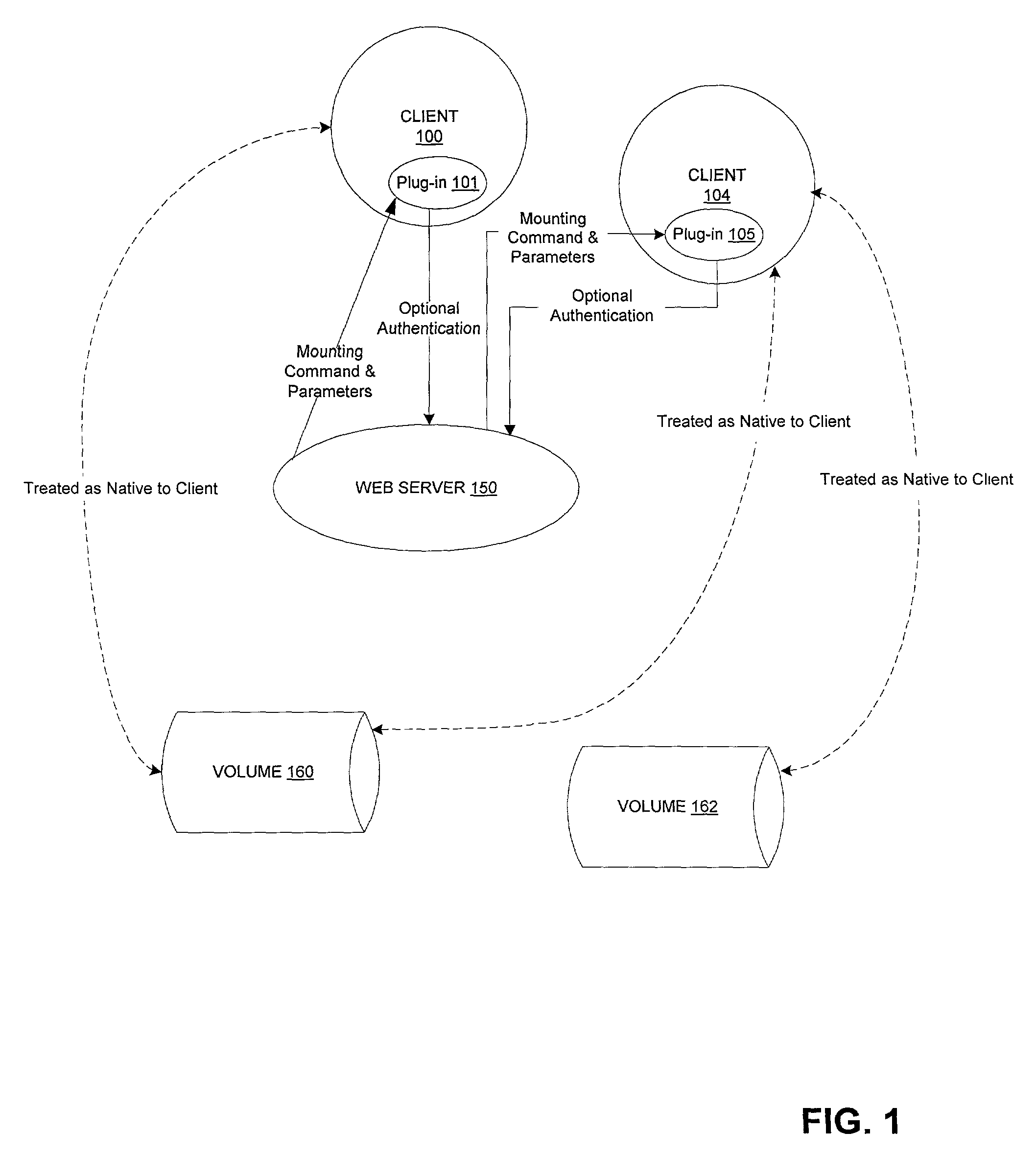

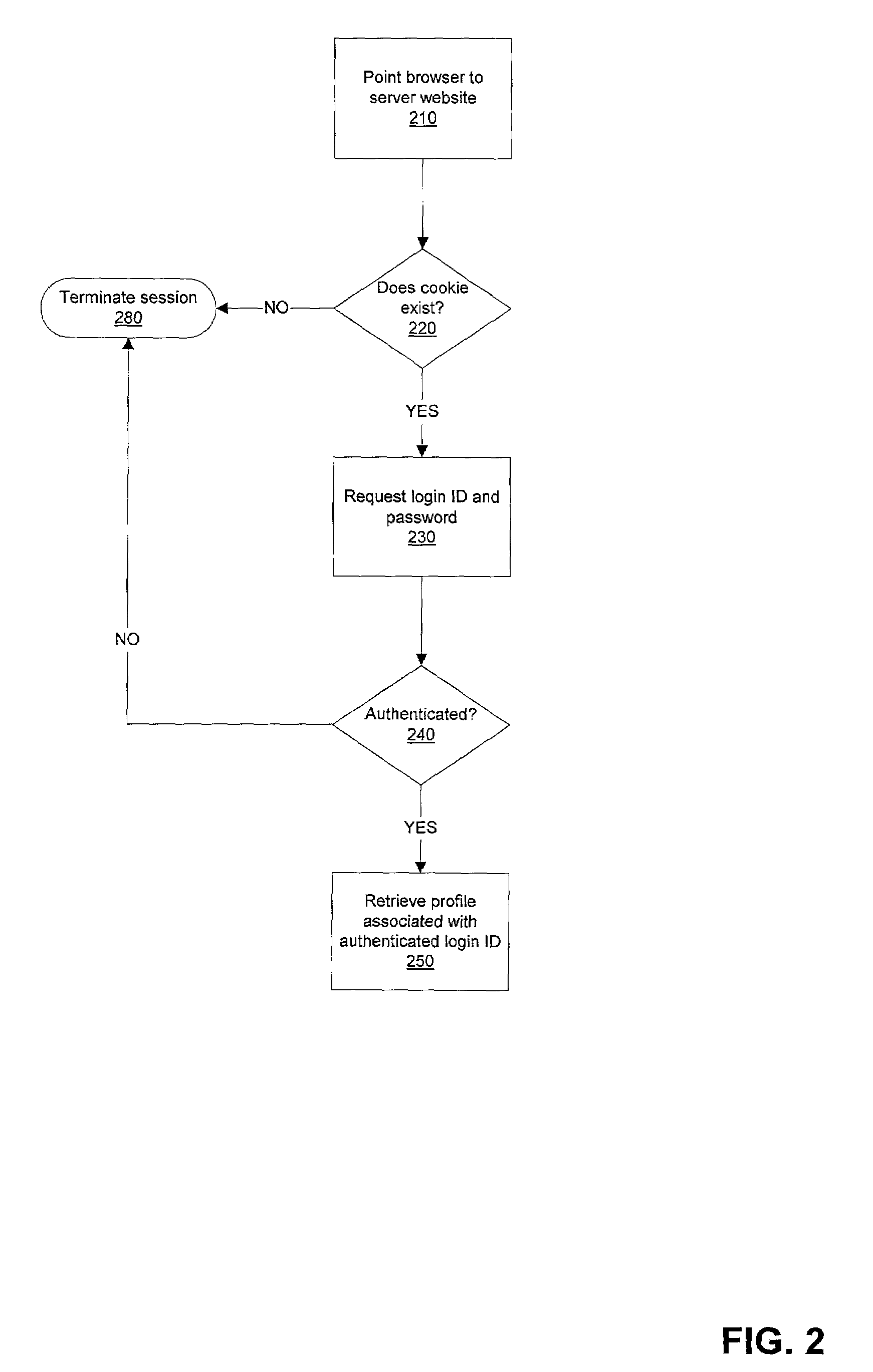

Method and apparatus for automated remote volume mounting using a plug-in installed on a client

ActiveUS7249168B1Computer security arrangementsMultiple digital computer combinationsWeb browserFile system

A method and apparatus for remotely and automatically mounting volumes over a network. The invention uses an interface, such as a web browser, to authenticate a client on a server. The server supplies volume mounting parameters specific to the authenticated client via a plug-in installed on the client. The plug-in then interacts, in one embodiment of the invention, with file system software on the client and automatically mounts the volume(s) in accordance with the supplied parameters.

Owner:APPLE INC

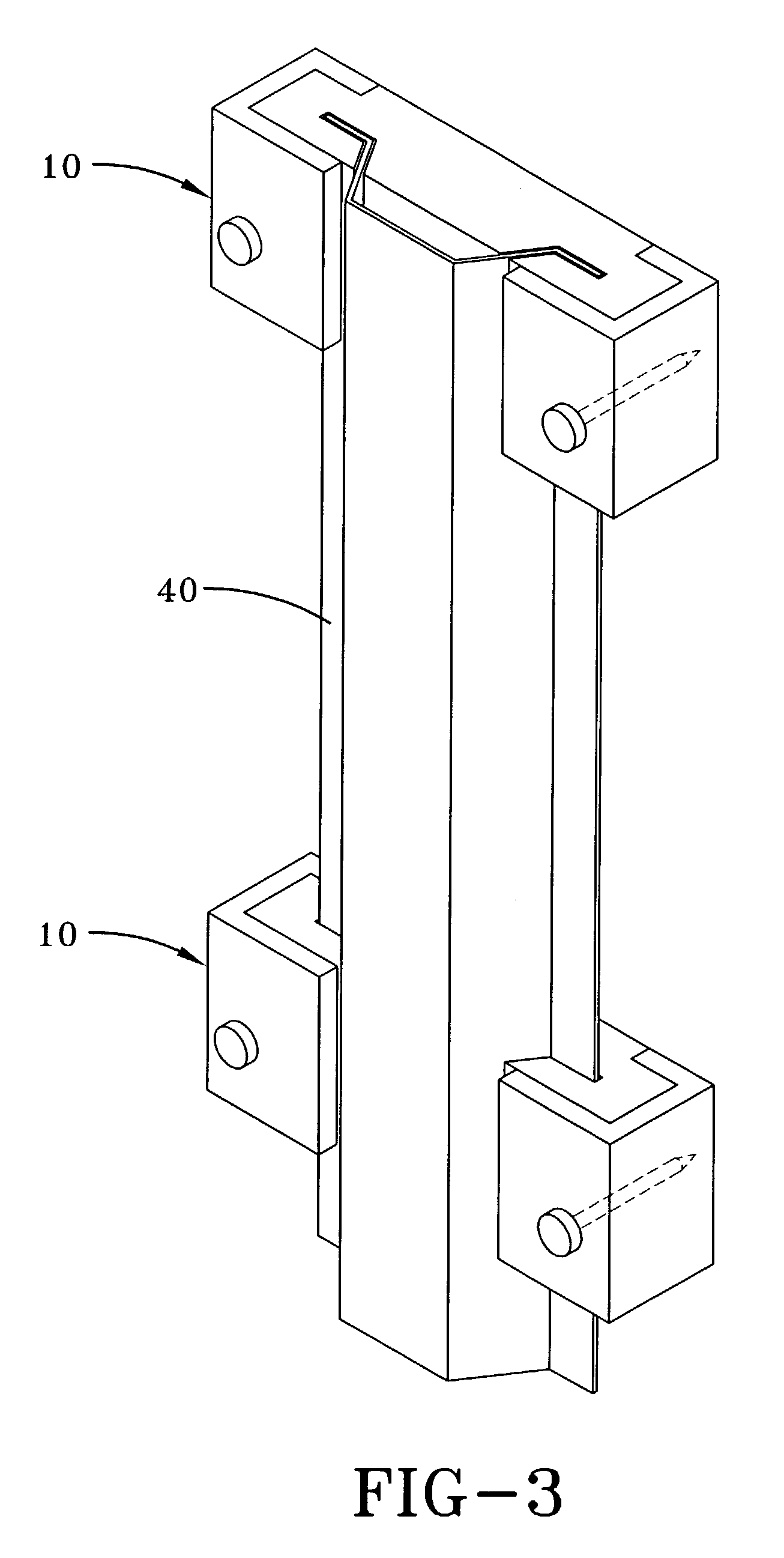

Vibration isolating mount

The present invention comprises a vibration isolating mount used to mount a furring channel to a mounting surface wherein the furring channel comprises a channel portion and two opposing furring channel flanges. The vibration isolating mount comprises a vibration isolator of a size and shape to fit snugly around the furring channel flanges, wherein the vibration isolator has opposing flanges extending away from the furring channel flanges; and mounting brackets, wherein the mounting brackets wrap around the vibration isolator flanges, and wherein the mounting brackets are isolated from the furring channel by the vibration isolator.

Owner:KINETICS NOISE CONTROL

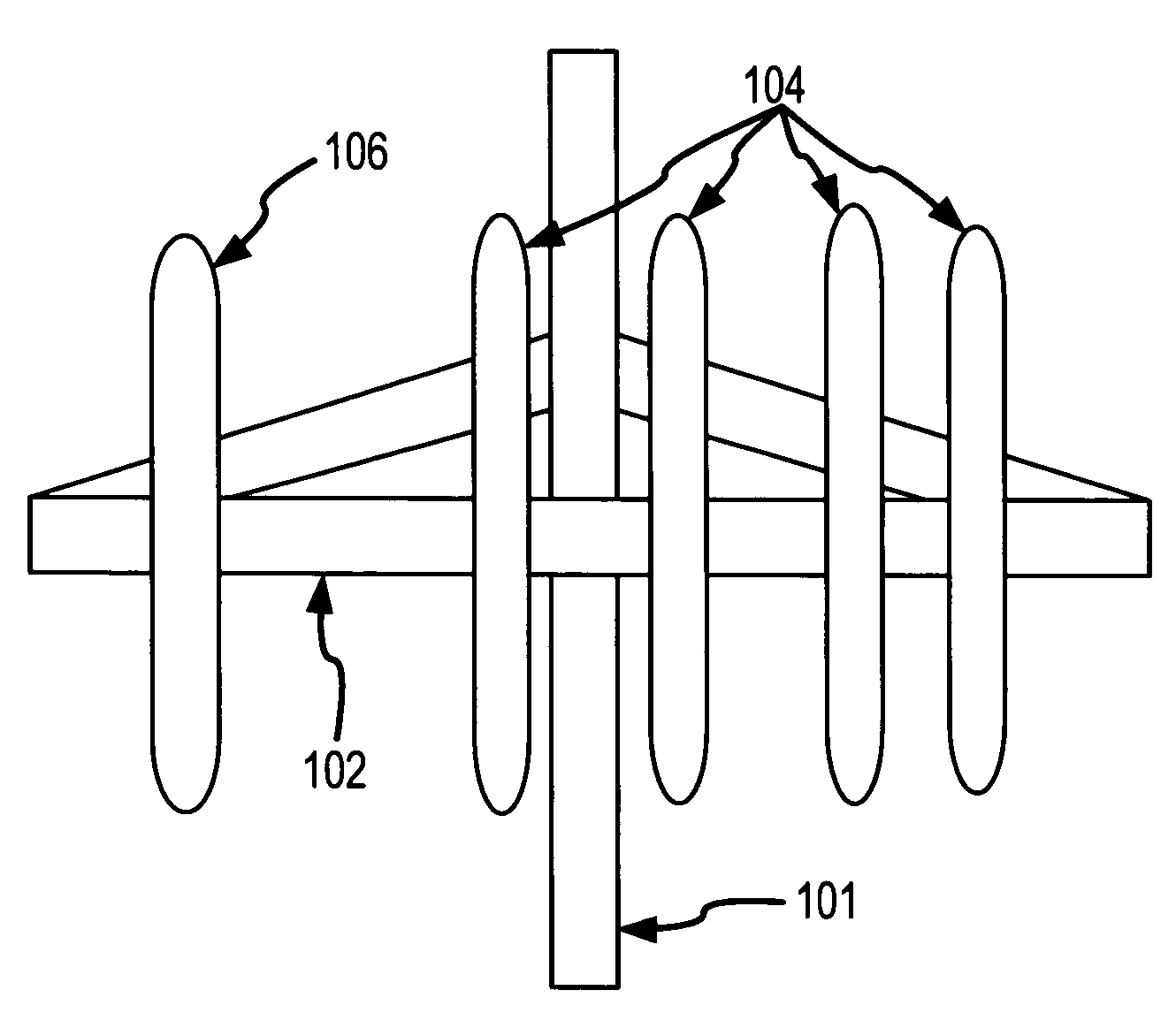

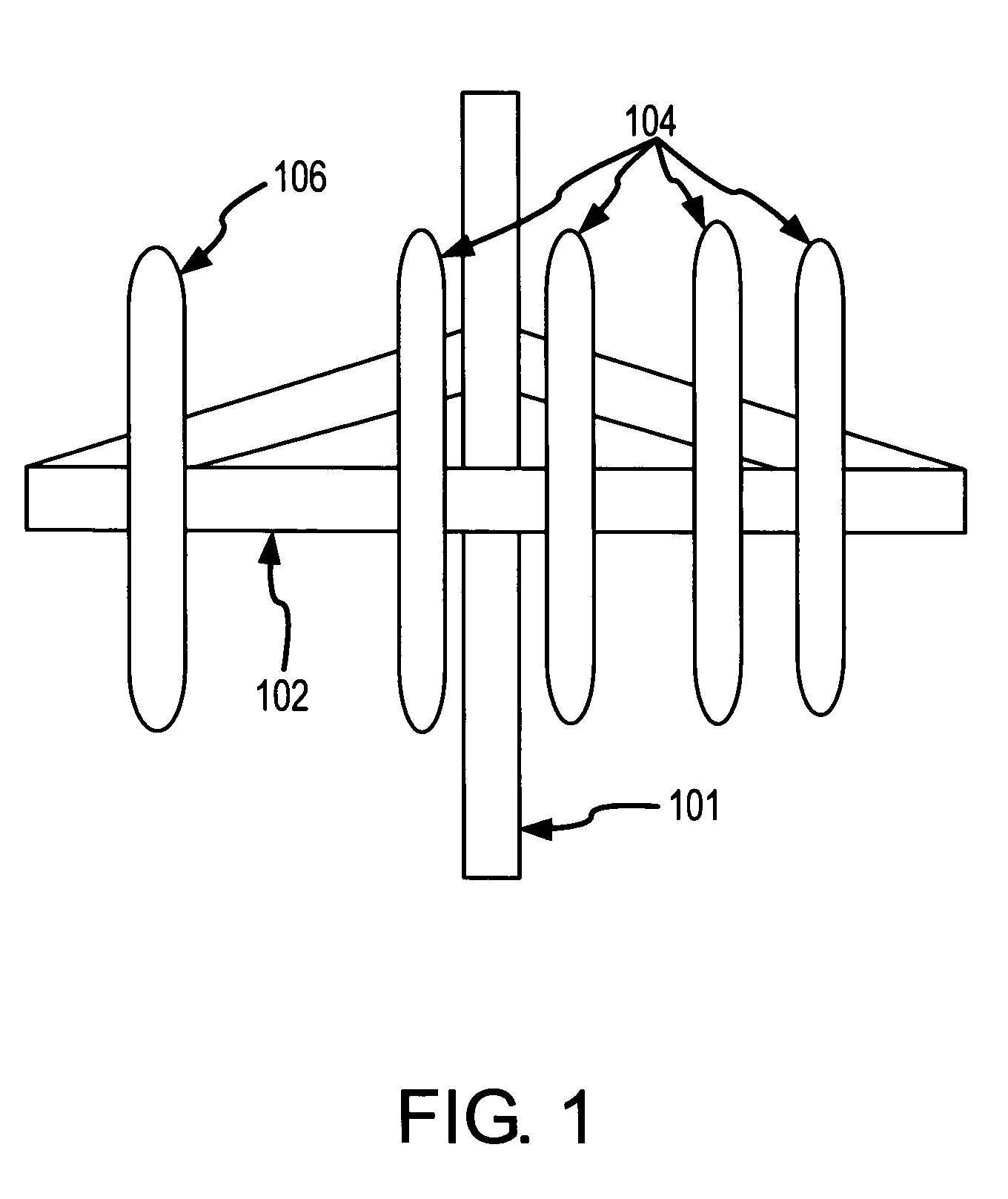

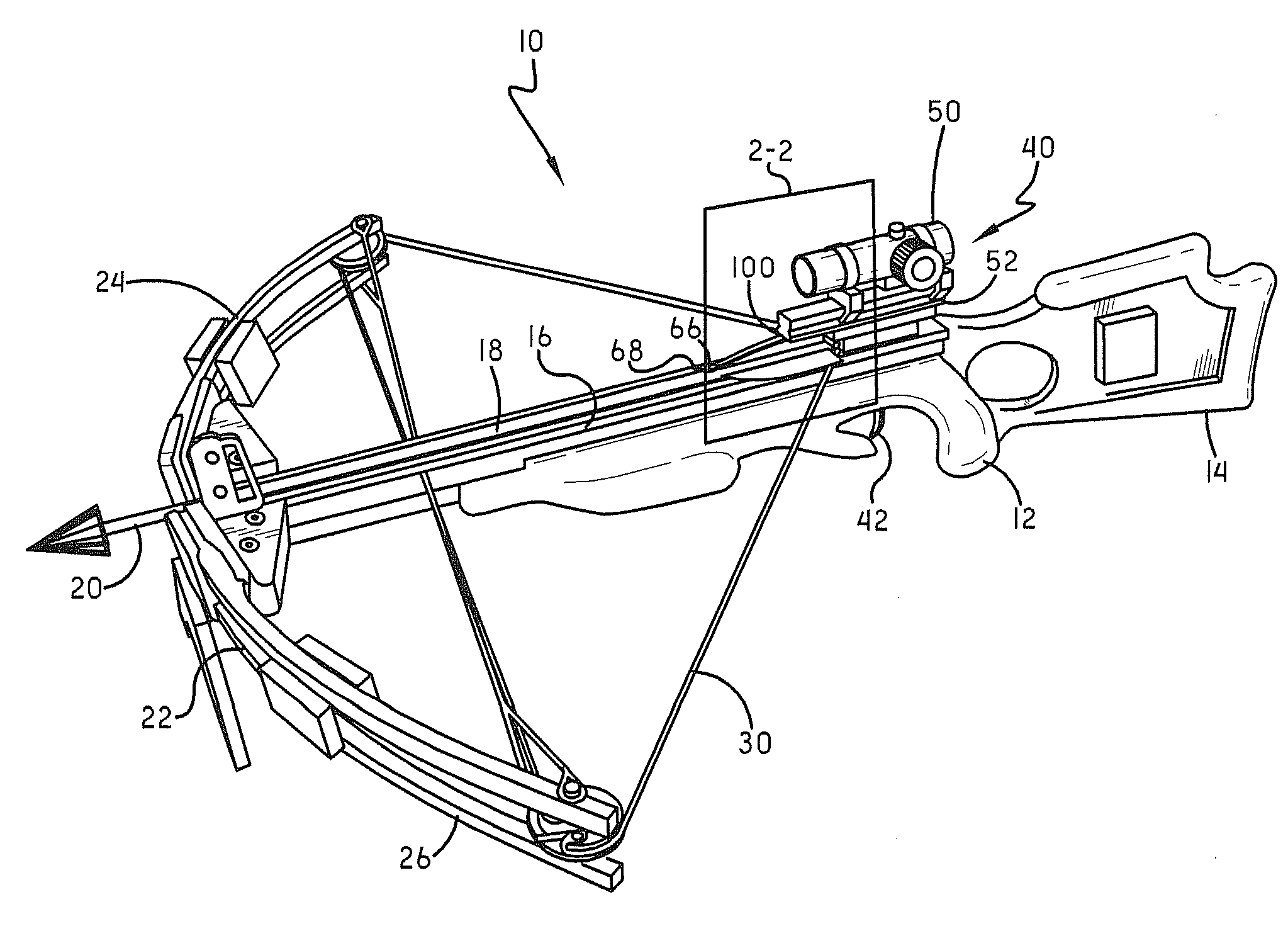

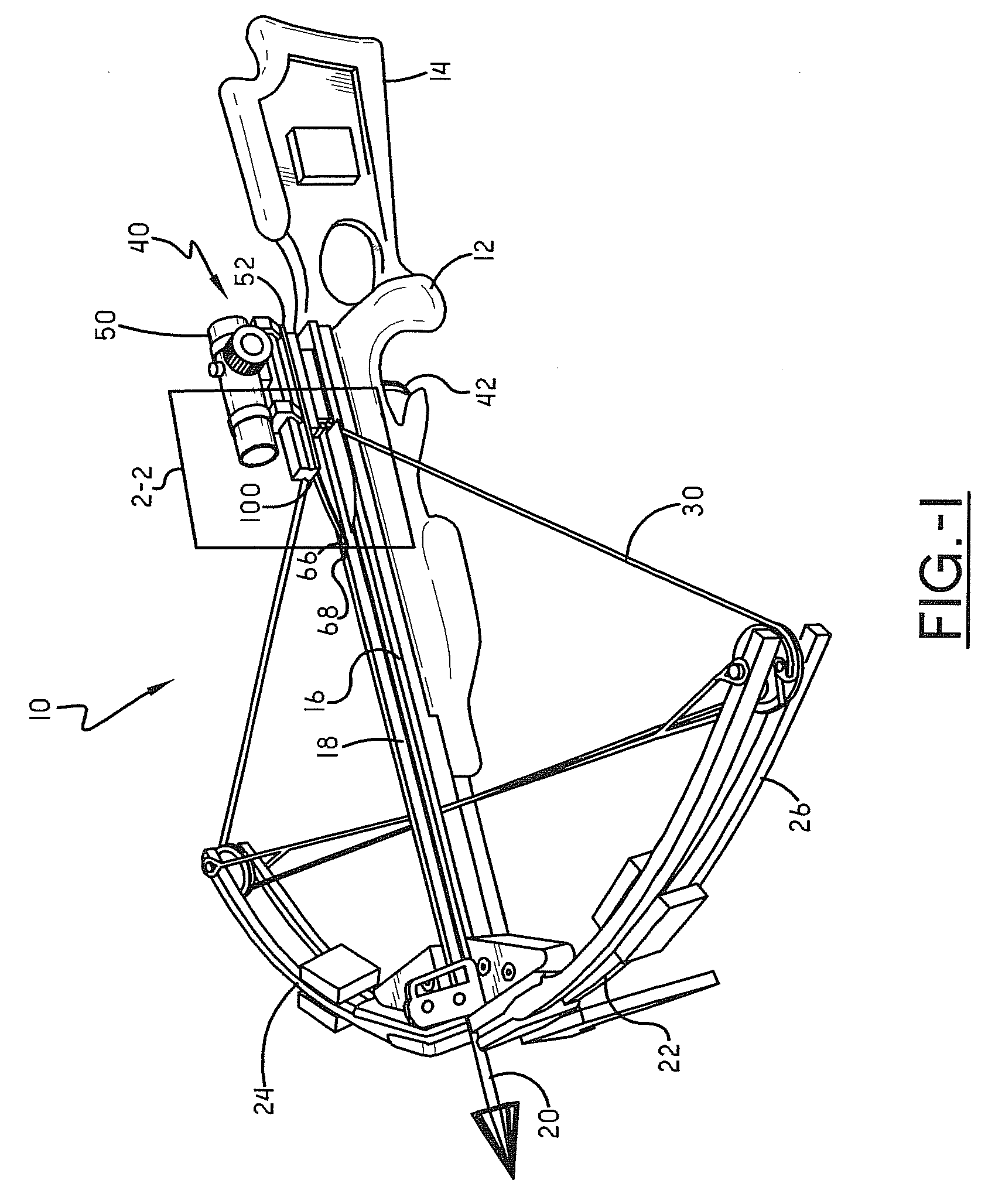

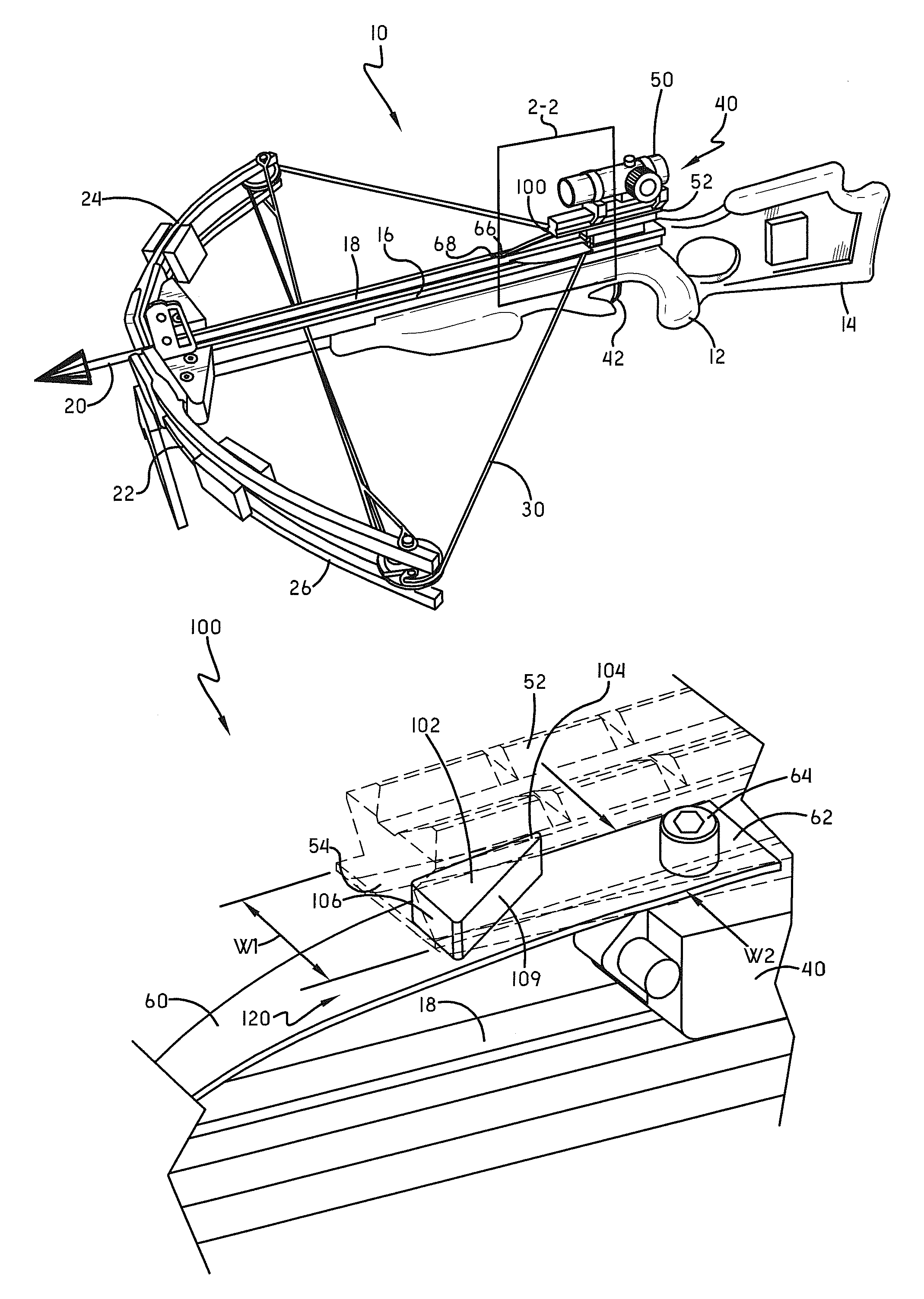

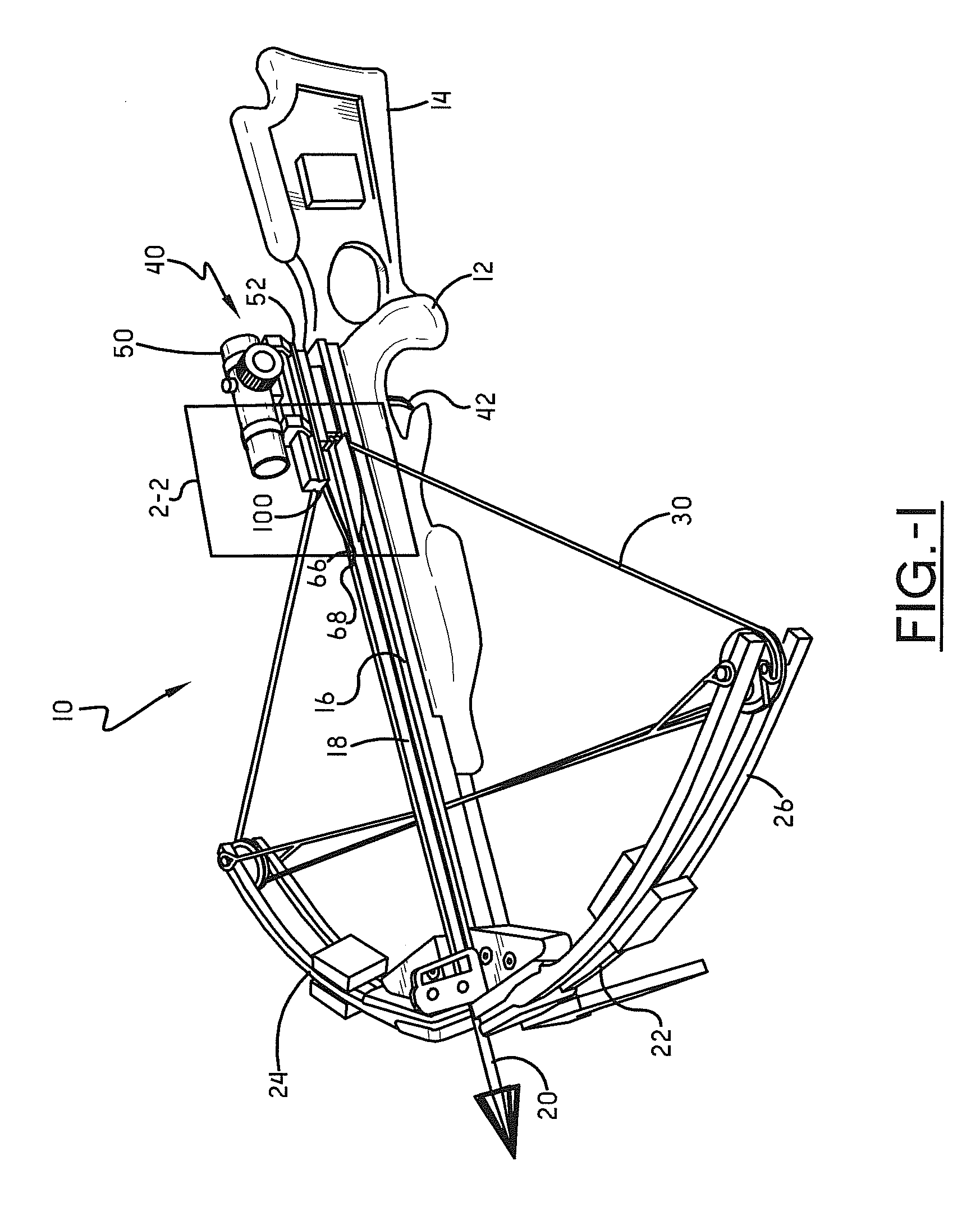

Vibration Dampening Arrow Retention Spring

A crossbow includes a body having a stock member and a barrel connected to the stock member. The barrel has an arrow receiving area for receiving an arrow. The crossbow also includes a bow having a pair of bow arms, a bowstring connected to the bow arms, a bowstring release mechanism used to hold and release the bowstring and, a scope mount used to hold a scope. An arrow retention spring is provided for retaining the arrow to the arrow receiving area. A vibration dampener may be positioned between the arrow retention spring and the scope mount in order to dampen the arrow retention spring vibrations made when shooting the crossbow. This greatly reduces unwanted noise.

Owner:HUNTERS MFG CO INC

Radiation CT radiographing device, radiation CT radiographing system, and radiation CT radiographing method using the same

InactiveUS20050265515A1Fast processingLow costMaterial analysis using wave/particle radiationRadiation/particle handlingControl signalSignal generator

An object rotating type cone beam radiation CT radiographing device in which a high speed and high sensitivity are obtained with low costs is provided. Thus, a radiation CT device of high performance for vehicle-mounted use and group medical examination can be provided at low costs. In the object rotating type cone beam radiation CT radiographing device, a rotational angle of an object is detected, a signal storage period of a batch-exposure type radiation image sensor panel is controlled on the basis of the rotational angle signal, and a signal storage period of a signal storage type reference signal generator is controlled. There is provided a radiation CT radiographing device in which the object can be photographed at arbitrary resolution during the photographing, a fluctuation of a radiation source during the photographing can be detected without using a special detector and corrected in accordance with its detection amount.

Owner:CANON KK

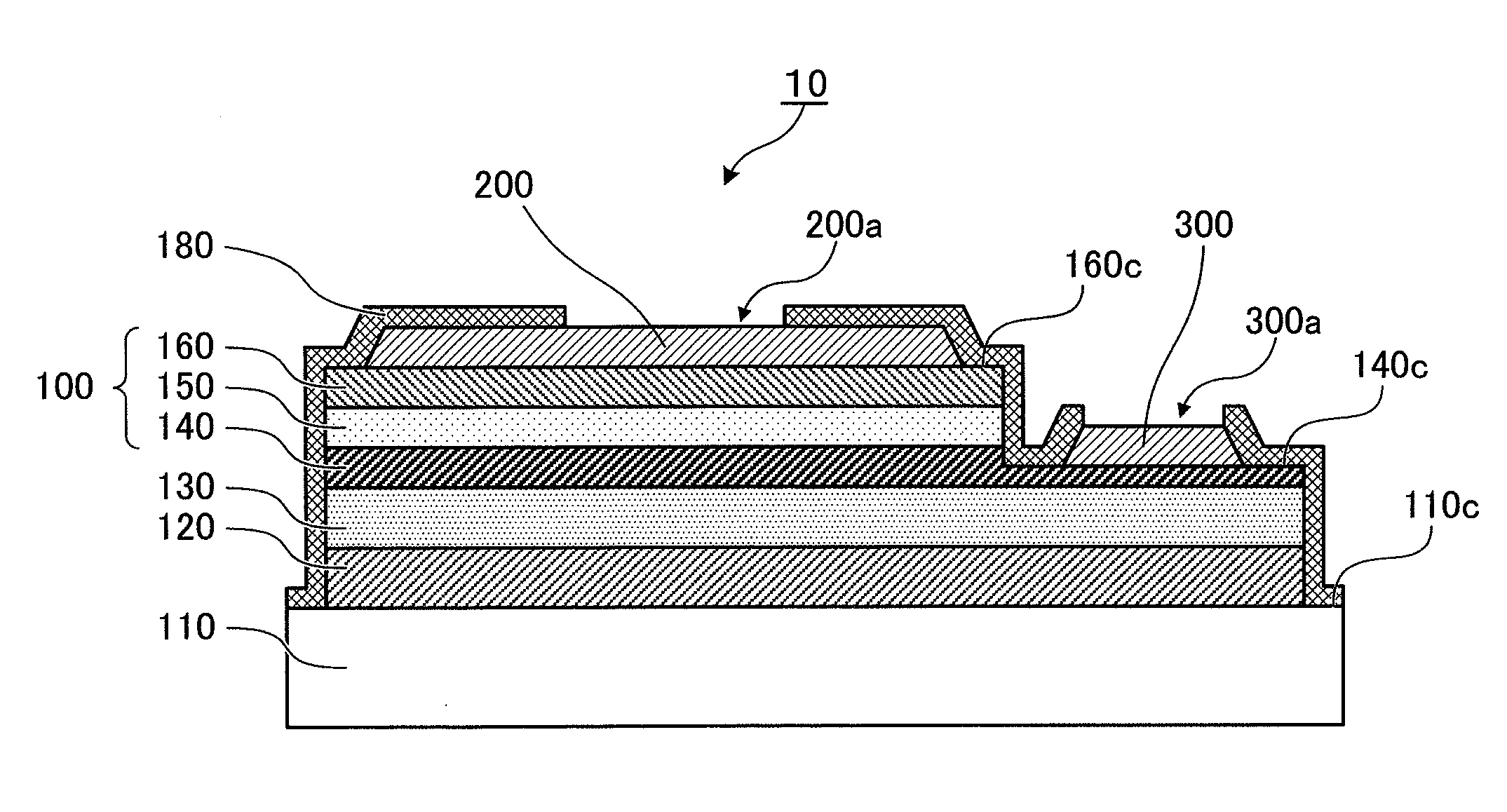

Semiconductor light- emitting element, semiconductor light- emitting device, method for producing semiconductor light- emitting element, method for producing semiconductor light- emitting device, illumination device using semiconductor light-emitting device, and electronic apparatus

ActiveUS20120138999A1Large light emission outputLow forward voltage VfSolid-state devicesSemiconductor/solid-state device manufacturingReflective layerLight emitting device

The disclosed semiconductor light-emitting element is configured from layering an n-type semiconductor layer, a light-emitting layer, and a p-type semiconductor layer (160); and a first electrode (200), which is the cathode, is formed on the p-type semiconductor layer (160). Also, between the p-type semiconductor layer (160) and a reflecting layer (220b), the first electrode (200) is provided with a crystalline first transparent electrode layer (210) and a non-crystalline second transparent electrode layer (220a). The crystalline first transparent electrode layer (210) increases adhesion with the p-type semiconductor layer (160), and the non-crystalline second transparent electrode layer (220a) suppresses delamination of the reflecting layer (220b). Also, the first transparent electrode layer (210) and the second transparent electrode layer (220a) transmit light emitted from the light-emitting layer and suppress degradation of reflective characteristics. In this way, delamination of the reflecting layer and degradation of reflective characteristics are suppressed in a semiconductor light-emitting element mounted using flip-chip (FC) mounting.

Owner:TOYODA GOSEI CO LTD

Vibration dampening arrow retention spring

A crossbow includes a body having a stock member and a barrel connected to the stock member. The barrel has an arrow receiving area for receiving an arrow. The crossbow also includes a bow having a pair of bow arms, a bowstring connected to the bow arms, a bowstring release mechanism used to hold and release the bowstring and, a scope mount used to hold a scope. An arrow retention spring is provided for retaining the arrow to the arrow receiving area. A vibration dampener may be positioned between the arrow retention spring and the scope mount in order to dampen the arrow retention spring vibrations made when shooting the crossbow. This greatly reduces unwanted noise.

Owner:HUNTERS MFG CO INC