A system for synchronous and real-time processing of video data using single-chip sram

A video data and real-time processing technology, applied in the field of image processing, can solve the problems of large image data and waste of off-chip resources, and achieve the effect of improving computing speed and saving off-chip resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

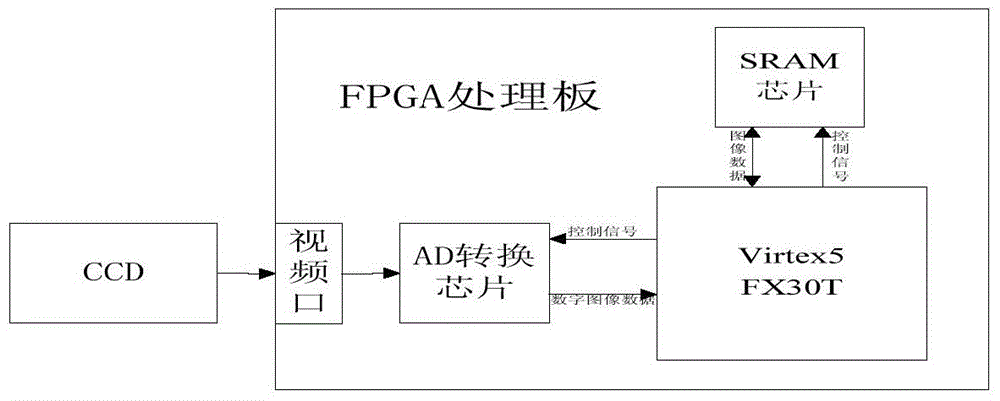

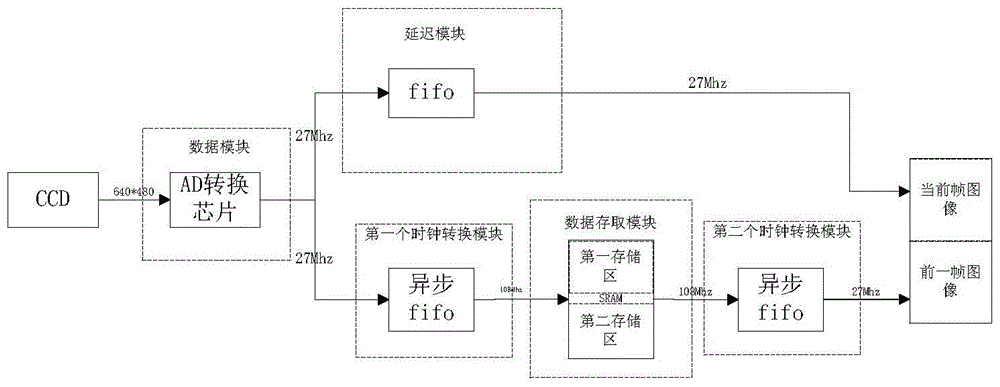

[0017] The processing system of this embodiment is as figure 1 As shown, the FPGA is the main processing chip, including a video interface, a piece of SRAM and a CCD; the CCD is connected to the FPGA processing board; the main chip of the FPGA processing board is Virtex5FX30T; the chip selected by the SRAM is IS61WV102416BLL, which contains 20 address bits And 16 data bits, with the address 400000 as the dividing line, it is divided into two parts, namely the first storage area and the second storage area; the algorithm is described in Verilog language, and the programming and simulation are completed on ISE13.1. The implementation process is as follows:

[0018] Step 1: First, power on the CCD and FPGA processing board respectively, input the video data collected by the CCD into the FPGA processing board through the video interface, and then complete the conversion from analog data to digital data through the AD conversion chip in the FPGA control data module Conversion, whe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More