A DMA transaction-level modeling method based on powerpc processor

A modeling method and transaction-level technology, applied in software simulation/interpretation/simulation, program control devices, etc., can solve problems such as DMA modeling and can not support DMA simulation, and achieve the effect of improving running speed and improving functions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] A PowerPC processor-based DMA transaction-level modeling method of the present invention will be described in detail below in conjunction with the embodiments and drawings.

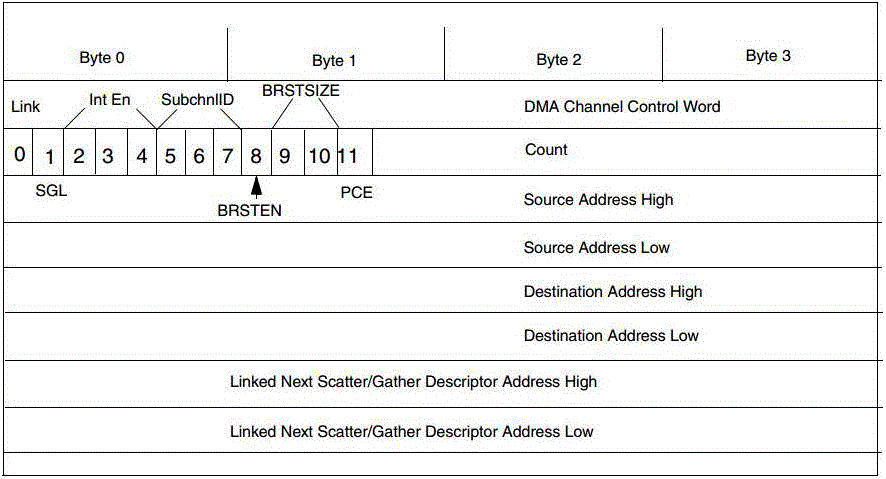

[0025] A DMA transaction-level modeling method based on PowerPC processors of the present invention aims at DMA controllers of PowerPC series processors, uses SystemC-TLM to carry out high-level modeling on DMA, and completes the system-level model of the DMA controllers. Modify the Qemu instruction set to realize the control of the DMA controller by using the DCR instruction, so that the DMA can complete the data transfer by programming the DMA when the CPU does not use the bus, and improve the simulation of the PowerPC processor.

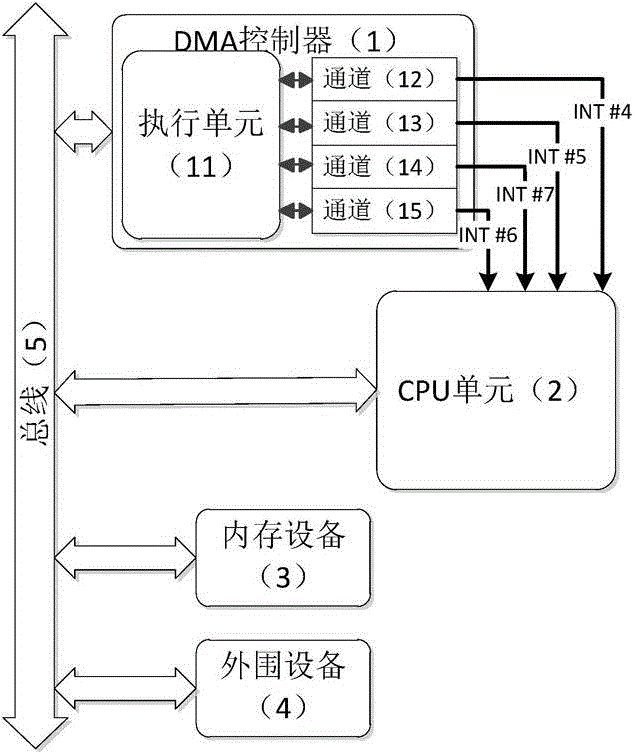

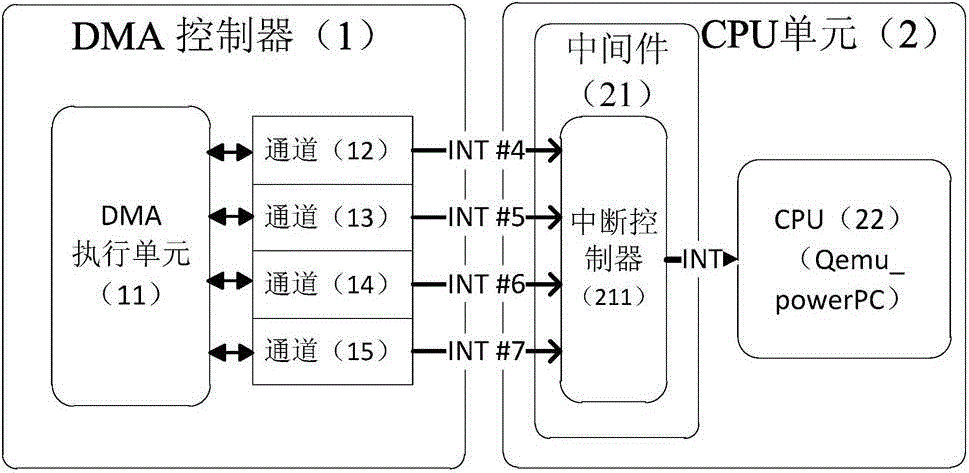

[0026] The present invention uses SystemC for modeling, and needs to complete the communication between the CPU and the DMA, the logic control inside the DMA, and the interrupt processing of the interrupts of the four channels of the DMA. Such as figure 1, DMA Executi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More