A kind of multi-DSP and FPGA parallel processing system and realization method

A parallel processing, FPGA4 technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of parallel interface signal line interference, interference, etc., and achieve high performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

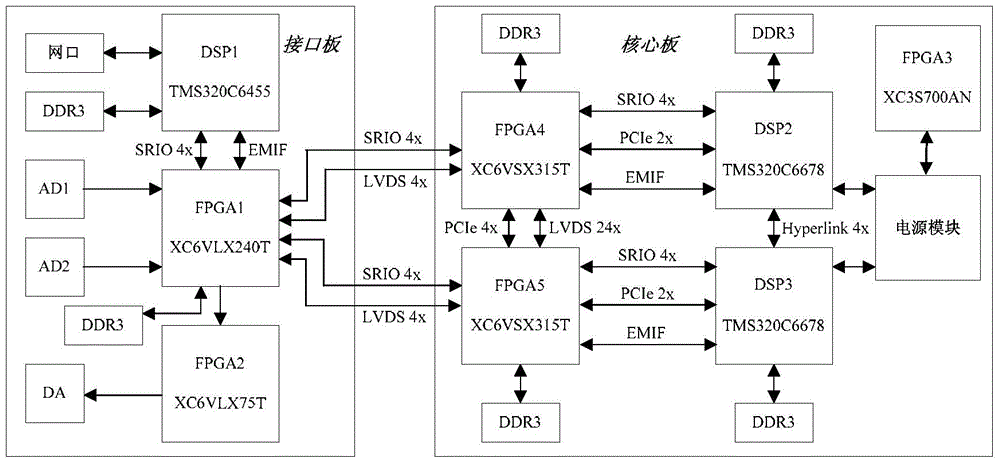

[0120] See figure 1 — Figure 7 , the multi-DSP and FPGA parallel processing system of the present invention includes: FPGA, DSP, AD, DA, DDR3, and power supply chip.

[0121] The present invention includes multiple FPGAs, and the functions of each FPGA are different. FPGA1 of the interface board controls two channels of AD to collect data; the collected data can be preprocessed; the preprocessed results are transmitted to FPGA4 and FPGA5 of the core board through SRIO; the processing results of FPGA4 and FPGA5 are received at the same time; SRIO is passed to DSP1 of the interface board; it receives the command of DSP1 and controls FPGA2 of the interface board according to the command. FPGA2 of the interface board controls the DA output waveform according to the command of FPGA1. The function of the FPGA3 of the core board is to control the power-on sequence of the core boards DSP2 and DSP3. The functions of FPGA4 and FPGA5 of the core board are similar, and they cooperate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More