Chip bonding pad layout design method suitable for multiple different encapsulation requirements

A chip pad and layout design technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of small number of pads, overlapping, and different shapes, so as to provide flexibility and reduce costs Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be further described below in conjunction with the accompanying drawings. The following examples are only used to illustrate the technical solution of the present invention more clearly, but not to limit the protection scope of the present invention.

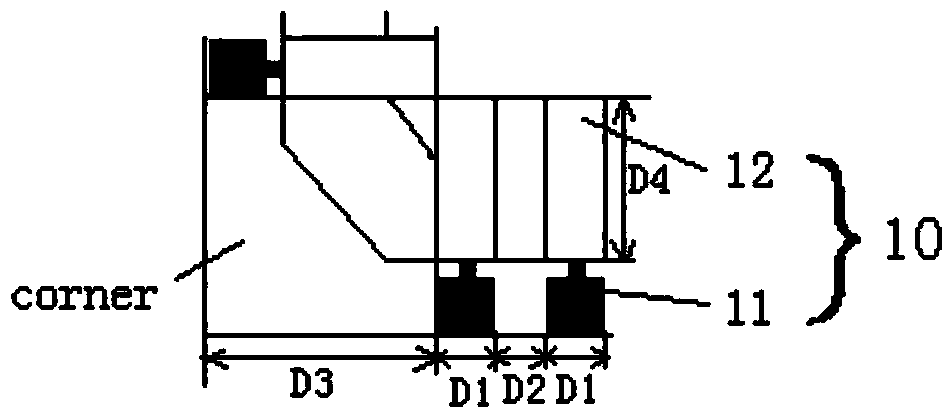

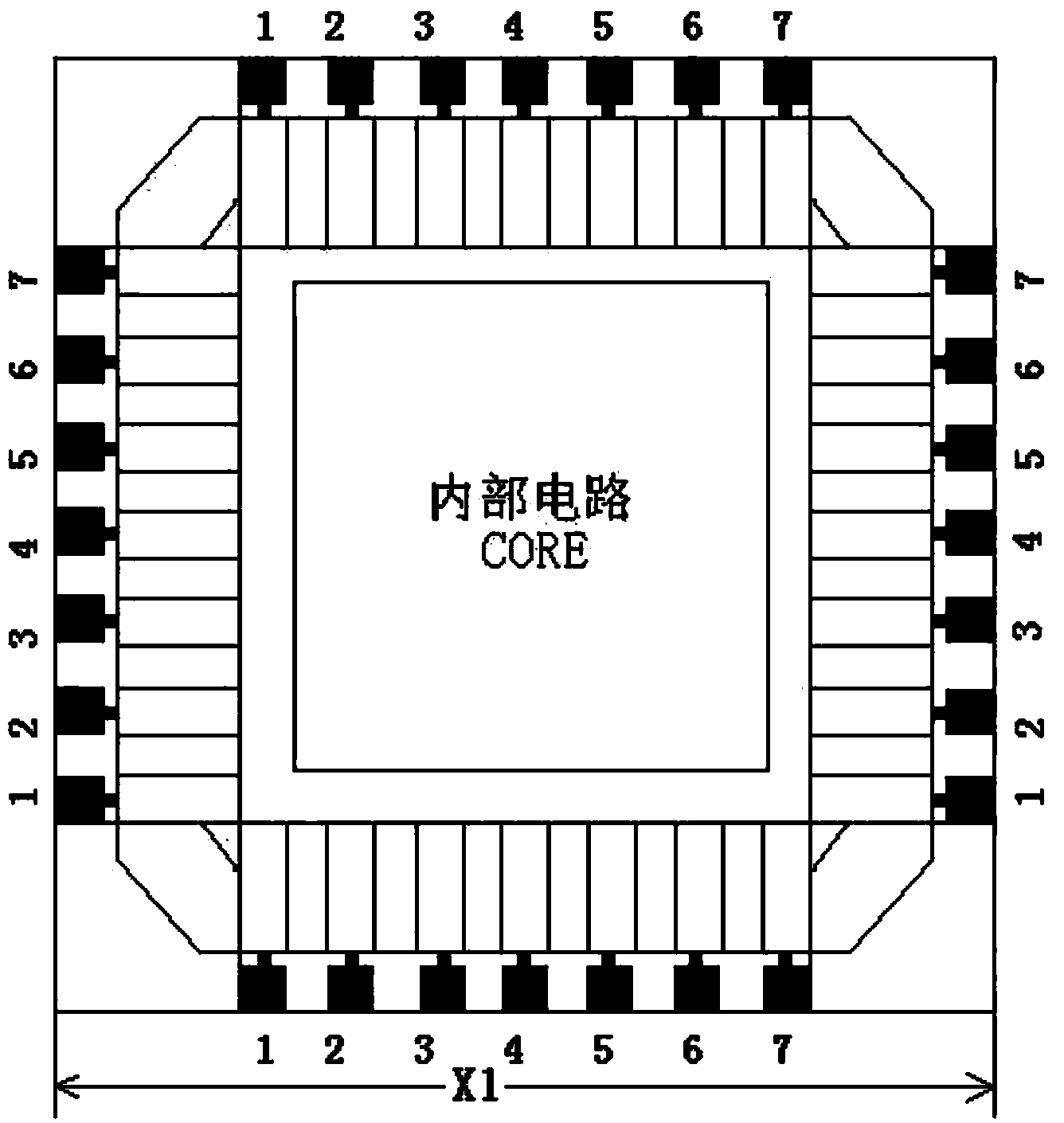

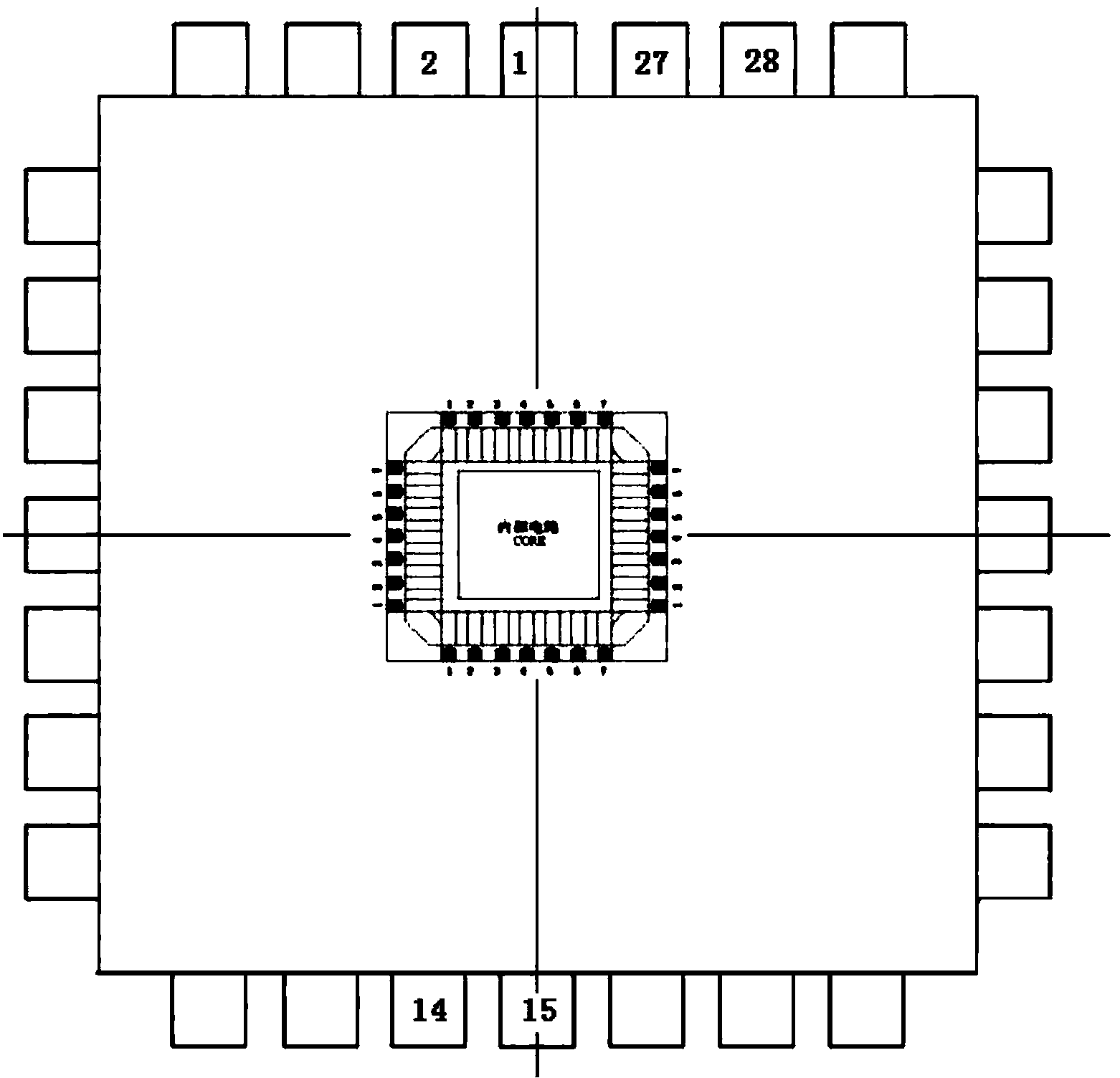

[0028] 1. Determine the total number of pads of the chip and the number of pads on each side: determine the total number of pads (N) of the chip, including necessary (such as input, output), redundant (such as multiple power supplies, grounds), available Selected (such as intermediate test), etc.; according to the total number of pads, roughly determine the number of pads on each side and the size of the chip in the length and width direction.

[0029] 2. Determine the basic package type: According to the total number of pads and the chip area, select a variety of package types that meet the requirements of the lumen size and lumen lead frame, and select a package type as the basic package type....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More