A Field Programmable Gate Array Layout Method Based on Simulated Annealing/Tempering

A technology of simulated annealing and layout methods, applied in the computer field, can solve problems such as being unable to cross the energy barrier and being sensitive to parameters

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0054] The application of the present invention to the EDA software layout tool supporting FPGA (Field Programmable Gate Array) field-programmable gate array development will be further described below in conjunction with the accompanying drawings and specific embodiments, and the application principle will be further described.

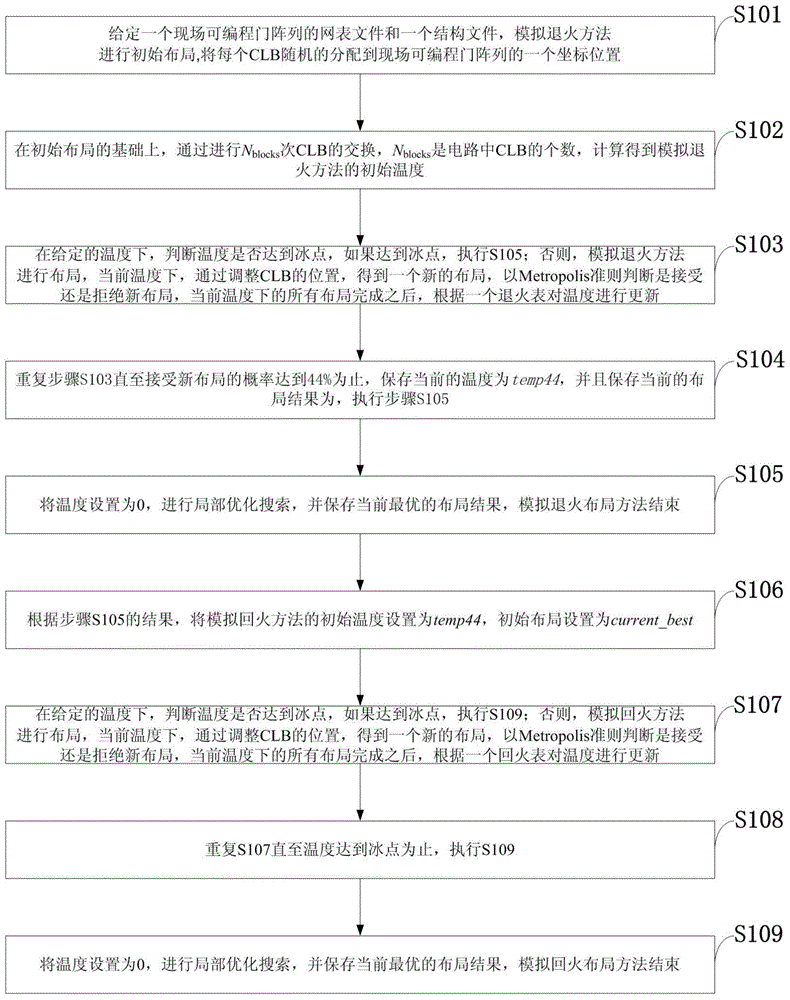

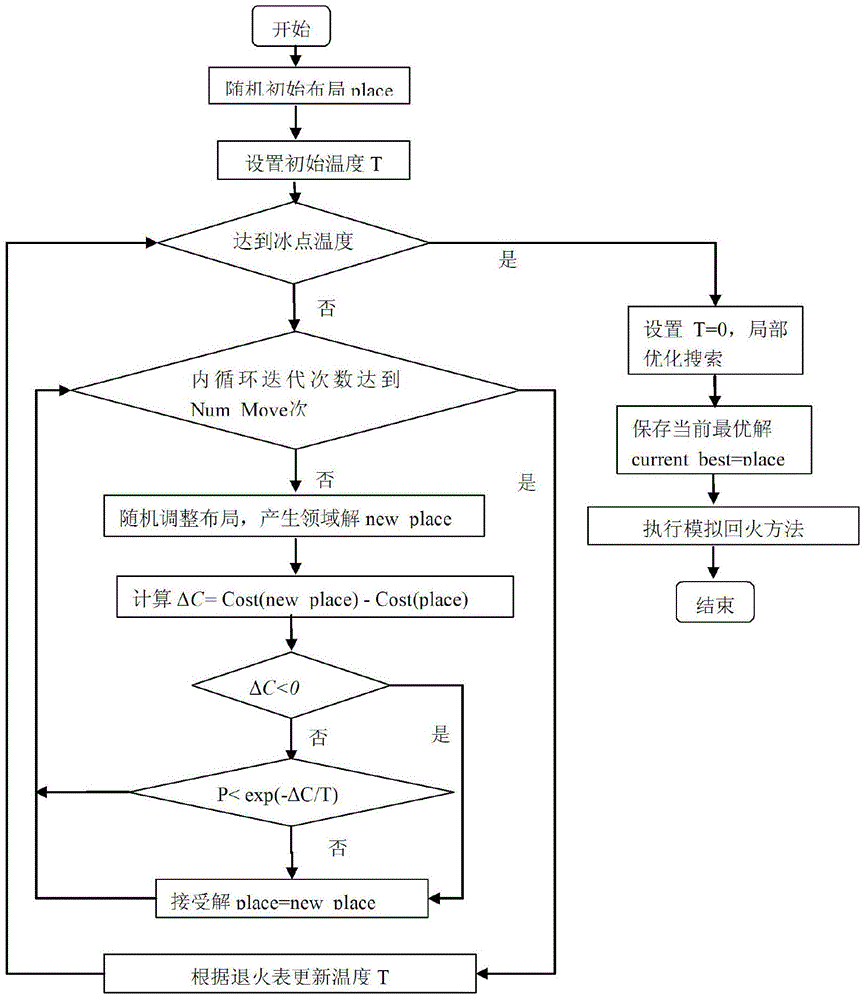

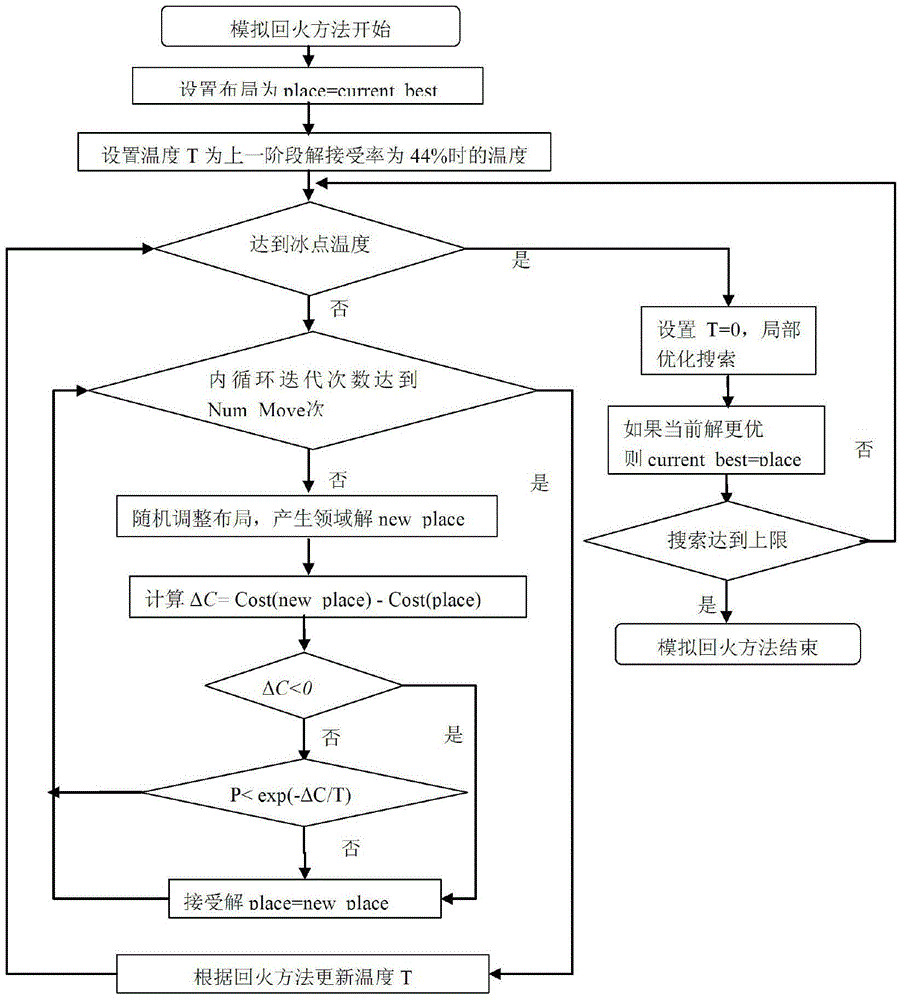

[0055] Such as figure 1 As shown, the method for field programmable gate array layout based on simulated annealing / tempering of the embodiment of the present invention is applied to a layout tool of EDA software supporting FPGA (Field Programmable Gate Array) field programmable gate array developm...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More