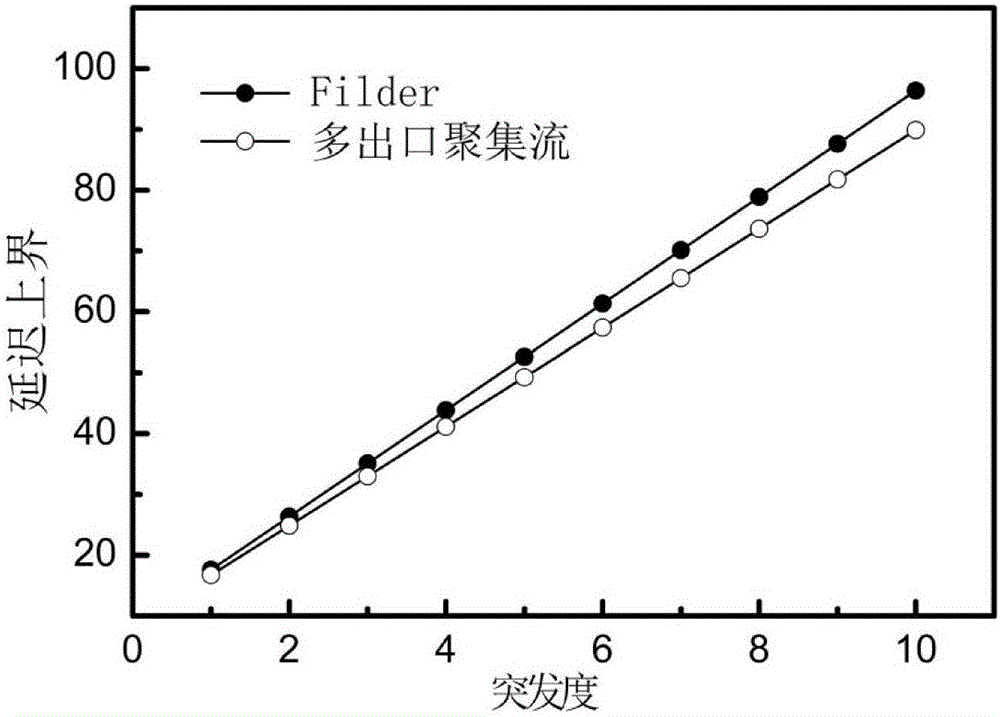

A multi-egress aggregation flow analysis method with an upper bound on the delay of on-chip network

A network-on-chip, multi-export technology, applied in instruments, electrical digital data processing, computers, etc., can solve problems such as insufficient Fidler model accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

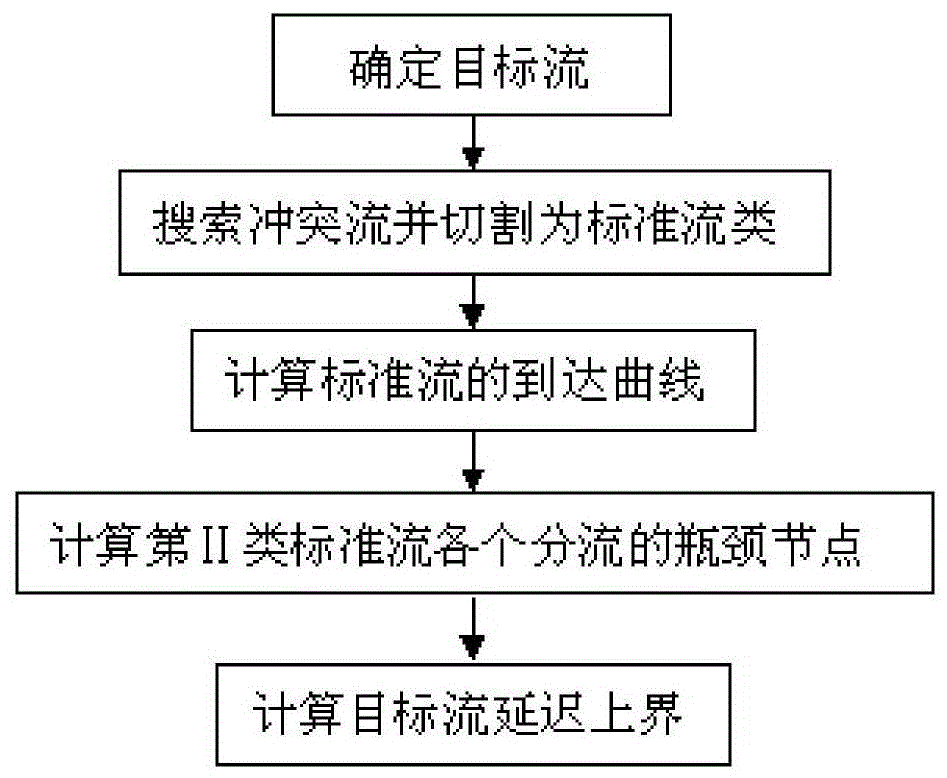

[0039] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0040] Such as figure 1 Shown is the flow chart of the method of the present invention.

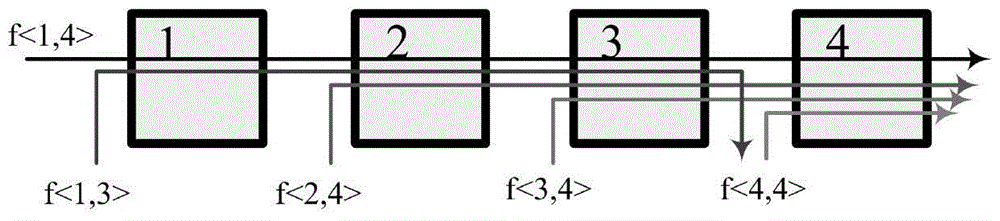

[0041] One, embodiment: with figure 2 Taking the conflict chain shown as an example, the calculation process of the delay upper bound is derived. Table 1 explains the formula parameters.

[0042] Table 1

[0043]

[0044]

[0045] Step 1: Determine the target stream:

[0046] There are 5 business flows in total, f <1,4> , f <1,3> , f <2,4> , f <3,4> and f <4,4> . we f <1,4> is the target flow, the other four f <1,3> , f <2,4> , f <3,4> and f <4,4> for the conflict flow. Assuming that the arrival curve of all business flows is α(t)=0.1t+2, it means that one data packet is sent every 10 cycles, and a maximum of two data packets are sent at one time. All routing nodes adopt FCFS arbitration strategy, and the service curve provided is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More