Method for improving operating efficiency of parallel architecture

A technology of operation efficiency and parallel processing, applied in the direction of concurrent instruction execution, machine execution device, resource allocation, etc., can solve the problems of reduced operation efficiency, unbalanced processing capacity among multiple channels, etc., to achieve the effect of improving processing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0015] The advantages and design content of the method for improving the operating efficiency of the parallel architecture described in the present invention will be described in detail below through an embodiment.

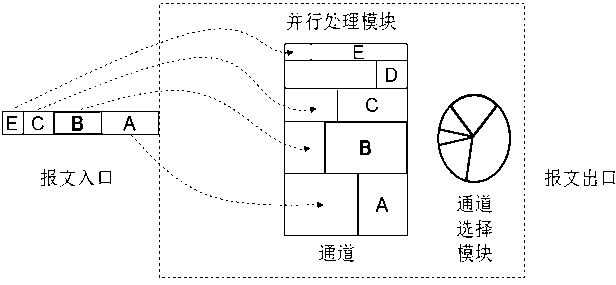

[0016] The method for improving the operating efficiency of the parallel architecture described in this embodiment proposes a parallel processing module, the parallel processing module includes a message entry, a message exit, multiple data processing channels and a channel selection module, wherein various message Enter the parallel processing module through the message entrance, the channel selection module is a selector that allocates time according to the processing complexity, the message flow with higher complexity gets more processing time and less sending time window, the complexity Low message, get less processing time and more sending time window; After processing, various messages are sent out through the message exit.

[0017] as attached figure 1 As ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More