Array substrate and display device

An array substrate and overlapping area technology, applied in optics, instruments, electrical components, etc., can solve problems such as large capacitance value, and achieve the effect of reducing capacitance value and reducing overlapping area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

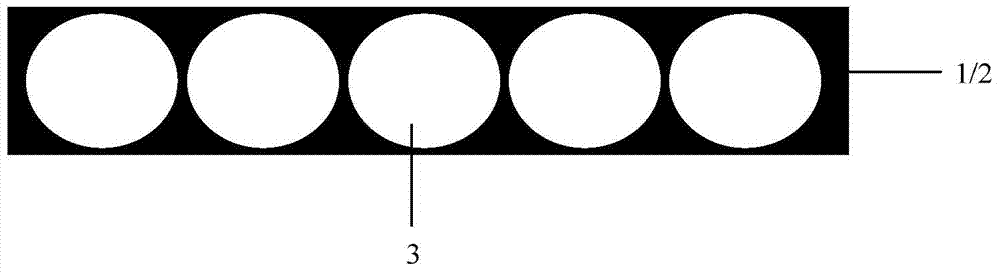

[0074] The solution of the embodiment of the present invention will be described below by taking the structure of a pixel unit included in the array substrate in the HADS mode display device as an example.

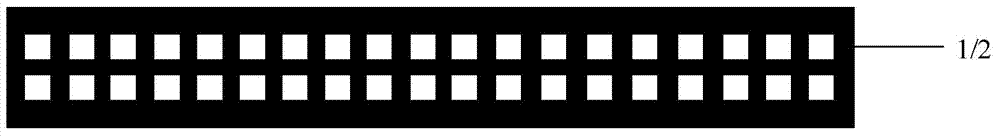

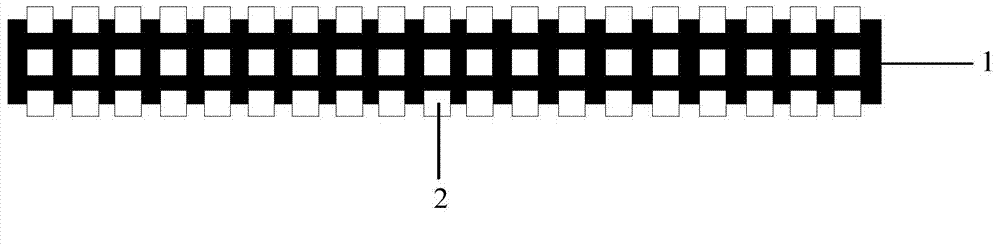

[0075] Such as figure 2 As shown, the array substrate of the HADS mode display device includes: a gate line 10 and a data line 20 crossing each other to define a pixel unit, a TFT (thin film transistor) 30 and a pixel electrode 40 located in the pixel unit and electrically connected to each other, and A common electrode line 50 that is provided on the same layer as the gate line 10 and is insulated from each other, and a common electrode layer 70 that is electrically connected to the common electrode line 50 through a via hole 60;

[0076] There is an overlapping area A between the electrically insulated common electrode layer 70 and the gate line 10, and an overlapping area B exists between the electrically insulated common electrode layer 70 and the data line 20;

[00...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More