Apparatus and method for providing multi-core programming platform

A platform, memory mapping technology, applied in program control device, program control design, input/output process of data processing, etc., can solve the problems of time-consuming, complexity, and lack of multi-core computer memory.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present advances described herein are directed to portable memory maps that can be ported to multiple multi-core platforms.

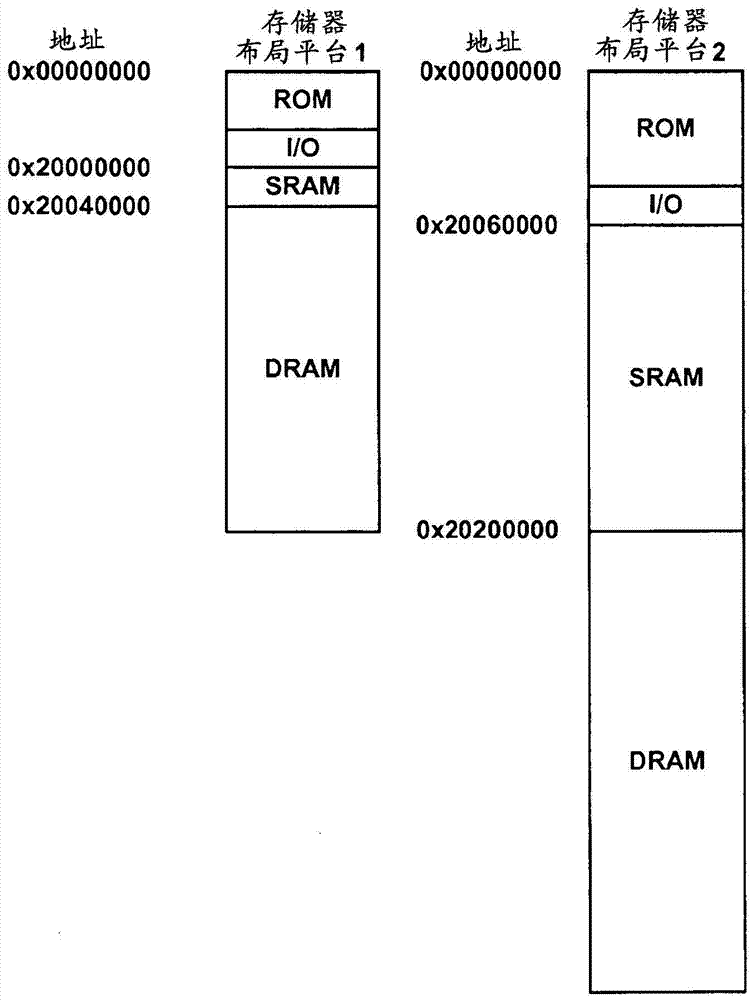

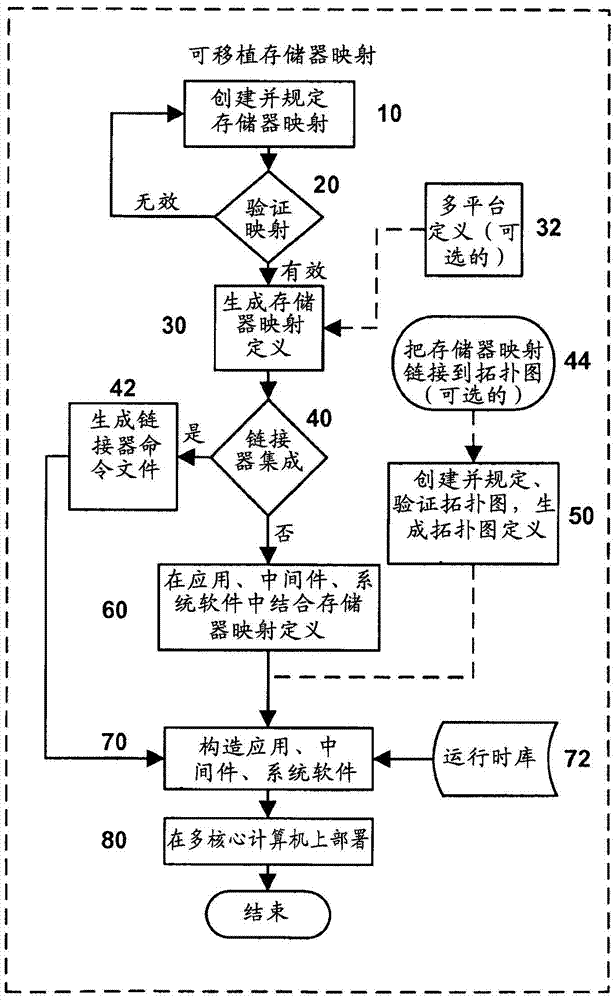

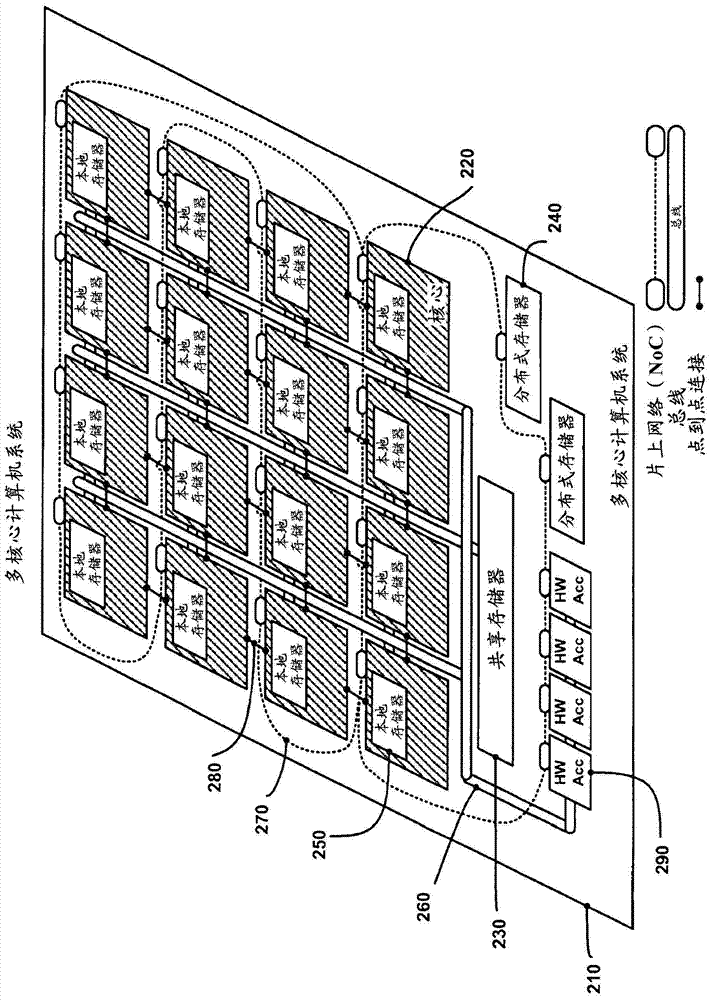

[0028] Portable memory-mapping methods and apparatus, also known as memory-mapping, provide fully portable memory-map definitions with greatly simplified multi-core platform-specific memory layout and memory utilization, see figure 1 . Depending on the embodiment, multiple cores in a multi-core computer or platform may be on a single chip or on multiple chips. A memory map definition is generated from a user-defined memory map. In some embodiments, the memory map definition includes a value representing a symbolically defined definition of the memory map provided in the descriptor file format. The descriptor file format is independent of architecture tools and development tools. That is, the descriptor file format is compiler, assembler, and linker independent. In some embodiments, the memory map definition is symbolically referenced from...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More