Sampling value linear interpolation operator and calculation method based on fpga

A linear interpolation and sampling value technology, which is applied to calculations using numerical representations and calculations using non-contact manufacturing equipment, can solve problems such as increased costs, large resources occupied by division operations, and shortage of FPGA chip hardware resources. Achieve the effect of saving hardware costs, saving resource usage, and ensuring normal operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

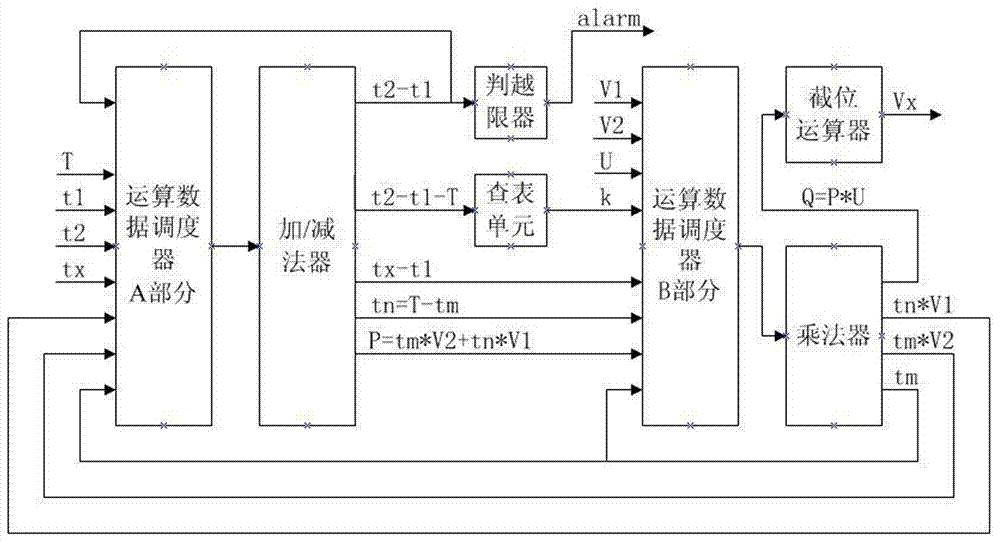

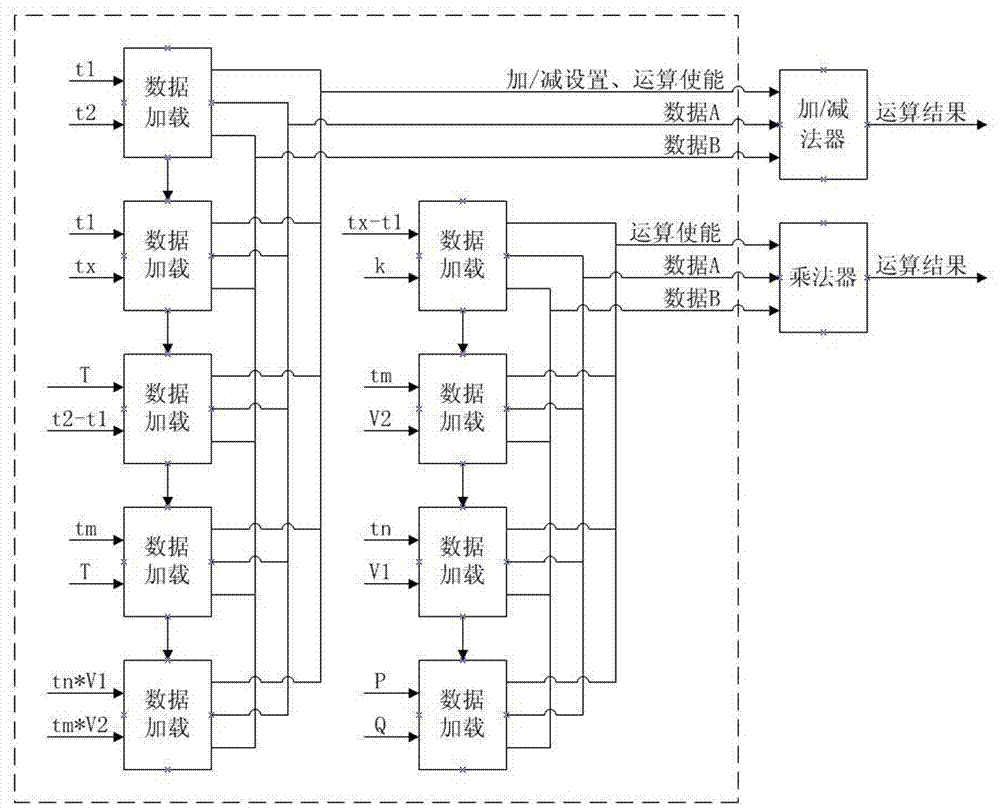

[0037] An FPGA-based sampling value linear interpolation operator is used to obtain the sampling value Vx at the tx time according to the sampling values V1 and V2 collected by the variable Vt at the time t1 and t2. The linear interpolation calculation formula is: Such as figure 1 As shown, it includes an adder / subtractor, a multiplier, an operation data scheduler (the two parts of the operation data scheduler A and B in the figure are actually the same module, and will not be distinguished in the subsequent description), a table lookup unit, and a truncation operator And judge the overrunning device, each module is connected through the data transmission line for data transmission. The table lookup unit uses t2-t1-T as the address to query the built-in storage block of the FPGA chip, and the storage depth is the number of frame interval values that do not exceed the limit, and each frame interval value corresponds to the address of a storage unit of the storage module. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More