A kind of preparation method of fs-igbt

A silicon chip and backside technology, applied in the field of power semiconductor devices, can solve the problems of silicon chip warping, difficulty, silicon chip size limitation, etc., and achieve the effect of reduced forward conduction voltage and small turn-off loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The principles and characteristics of the present invention will be further described below in conjunction with the accompanying drawings, and the examples given are only for explaining the present invention, and are not intended to limit the scope of the present invention.

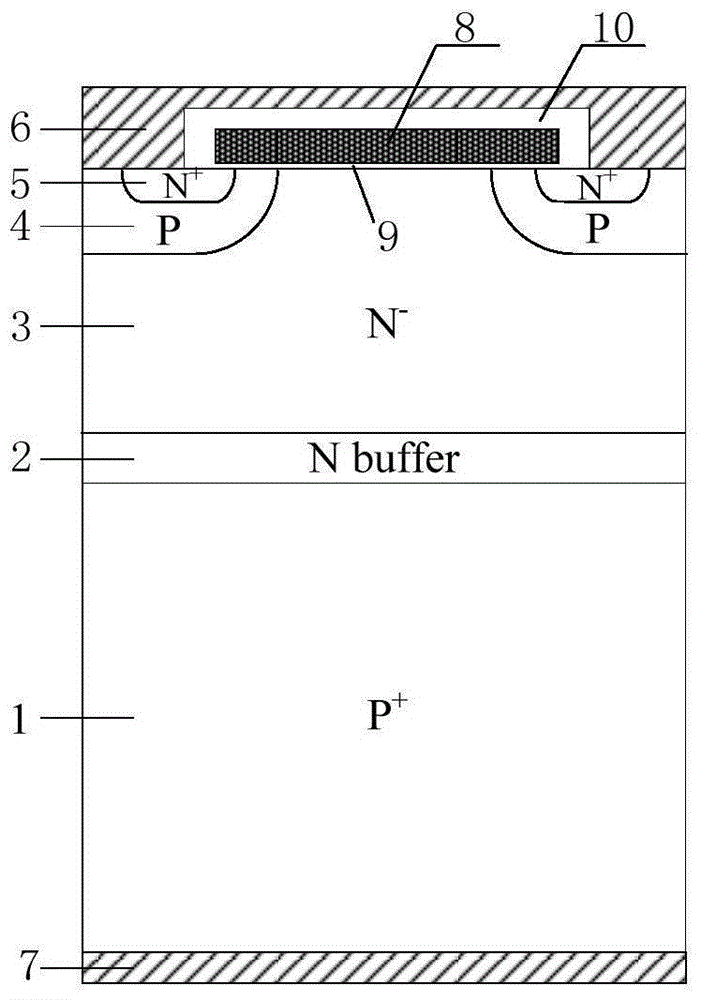

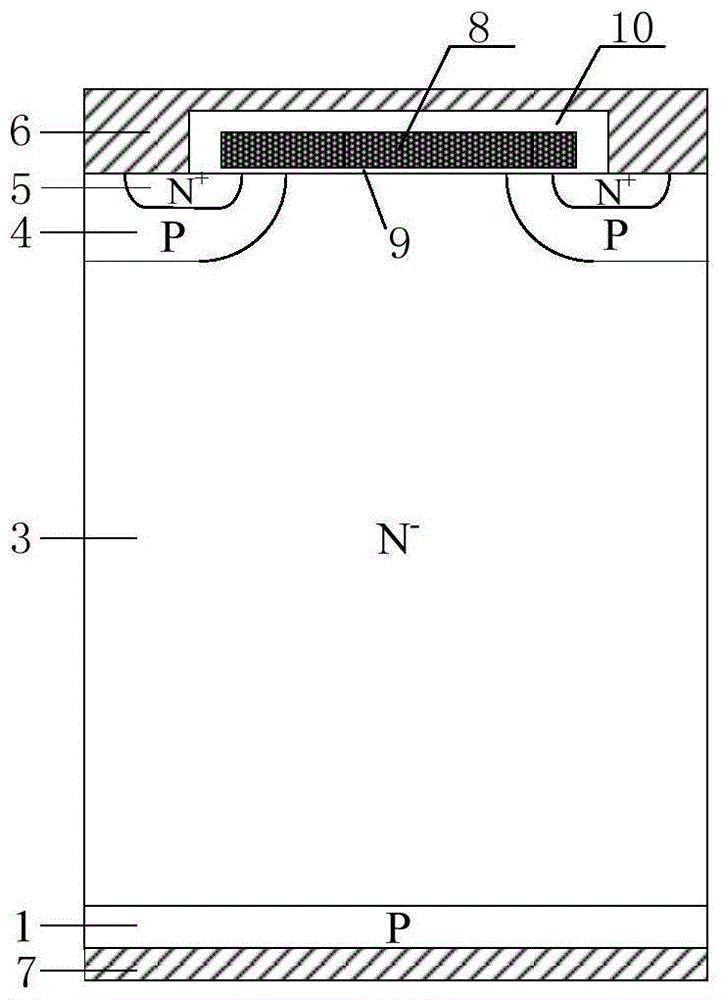

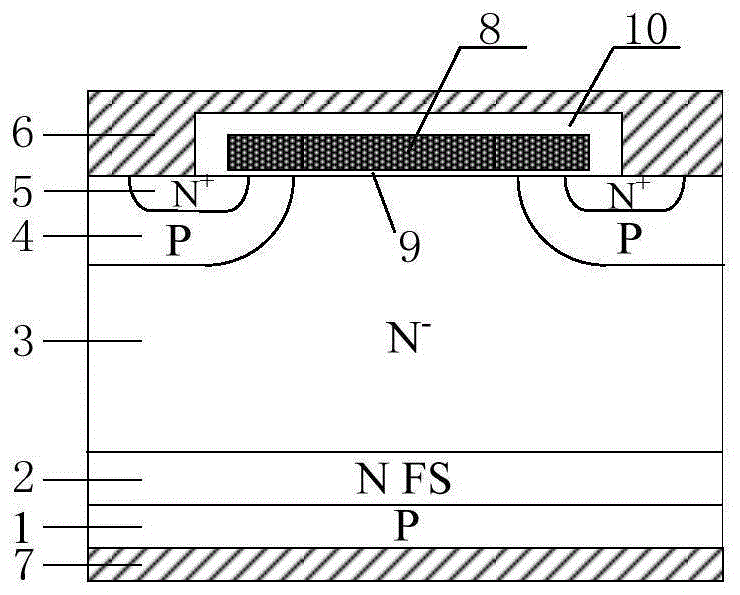

[0039] Such as Image 6 As shown, the present invention provides a kind of method that prepares FS-IGBT with thin drift region on thick silicon chip, comprises:

[0040] Step 1: Select two N-type monocrystalline silicon wafers as the first silicon wafer and the second silicon wafer. The thickness of the first silicon wafer is 300 microns, and lightly doped FZ silicon is used with a doping concentration of 2.5*10 14 piece / cm 3 , to form Figure 5 In the drift region 3 of the FS-IGBT mentioned in the above, the thickness of the second silicon wafer is 300 microns, and heavily doped CZ silicon is used, and the doping concentration is 5*10 19 piece / cm 3 , to form Figure 5 The back N+ region 11 of...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More