Method and device for mipi LANE signal serialization output based on fpga

A signal string and signal technology, which is used in image communication, color TV parts, TV system parts and other directions to achieve stable and reliable work, low implementation cost, and easy implementation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045]The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

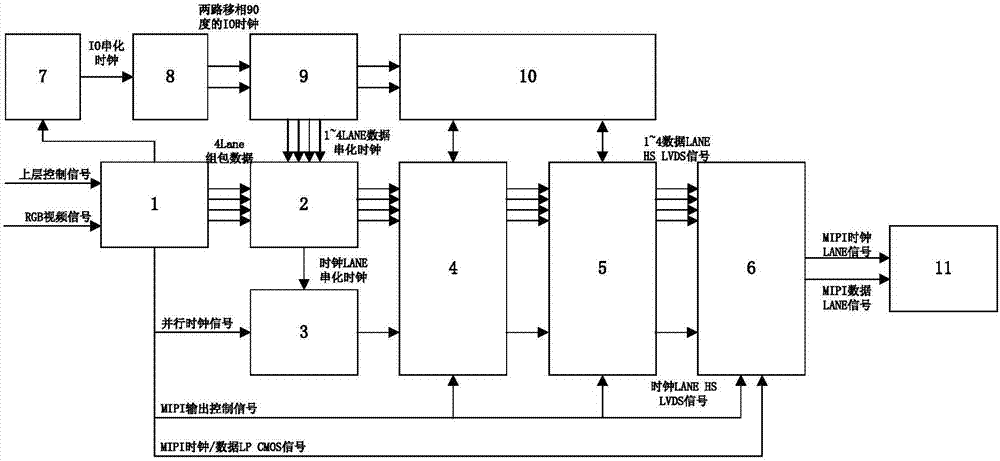

[0046] like figure 1 As shown, a device for realizing MIPI signal serialization output based on FPGA provided by the present invention includes MIPI data conversion and buffer module 1, BANK data serialization module 2, BANK clock serialization module 3, and BANK IO delay adjustment module 4 , LVDS output module 5, MIPI output module 6, IO serialization clock module 7, phase adjustment module 8, BANK driver module 9 and BANK IO calibration module 10;

[0047] The MIPI data conversion and buffer module 1 is respectively connected to the BANK data serialization module 2, the BANK clock serialization module 3 and the IO serialization clock module 7. The IO serialization clock module 7 is connected to the BANK drive module 9 through the phase adjustment module 8, and the BANK The drive module 9 is connected to the BANK data serialization ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More