Board-level fan-out chip packaging device and manufacturing method thereof

A chip packaging and fan-out technology, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problems of development and cost reduction, and achieve the effects of improving performance, improving heat dissipation performance, and eliminating dependencies

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

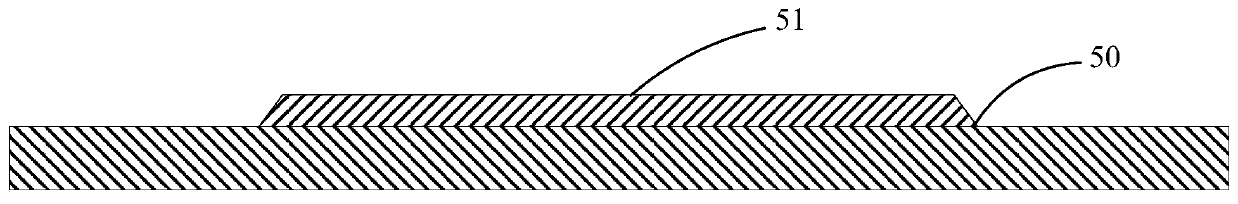

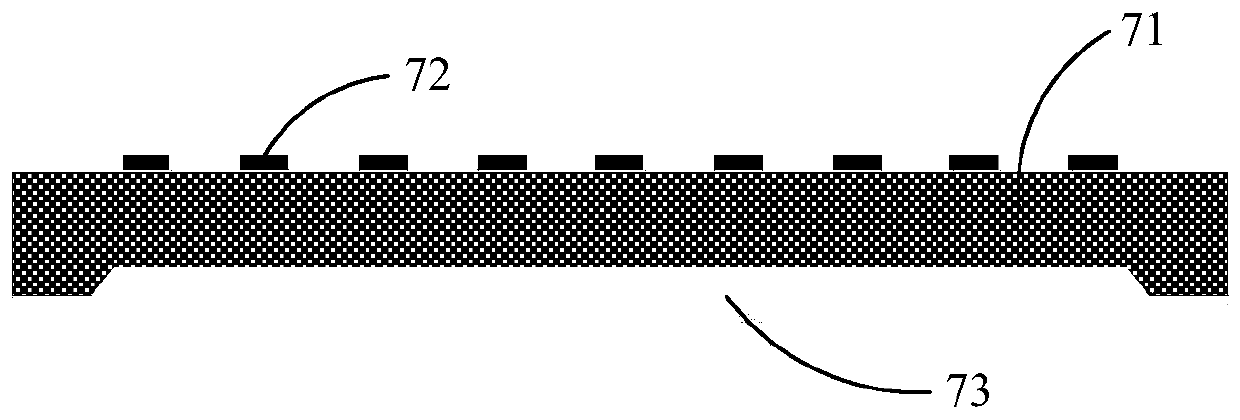

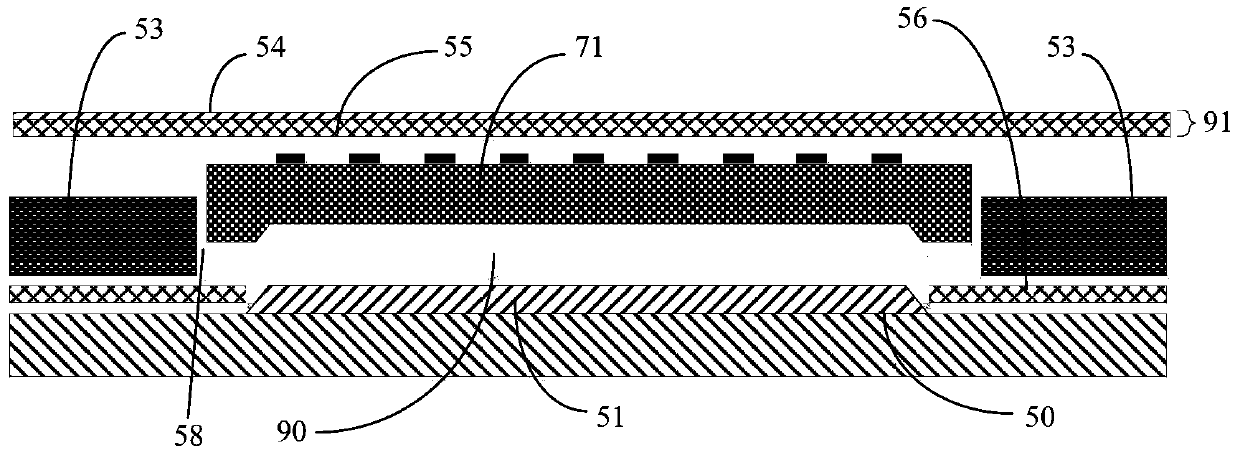

[0044] Therefore, the method for manufacturing a board-level fan-out chip packaging device provided according to an embodiment of the present invention includes: providing a carrier board on which bumps are provided; arranging a first dielectric around the bumps on the carrier board layer; arranging a core board on the dielectric layer, wherein the core board is provided with an opening, and the opening of the core board surrounds the bump; embedding the chip in the opening of the core board, wherein the backside of the chip has a size matching the bump The recess of the chip is embedded so that the recess of the back of the chip is engaged with the bump of the carrier board, and the core board surrounds the chip; a second dielectric layer is arranged on the embedded structure of the chip and the core board; and by extruding the chip and The embedding structure of the core board, the carrier board and the dielectric layer enables the material of the dielectric layer to fill the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com