Patents

Literature

119results about How to "Reduce craft production cost" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

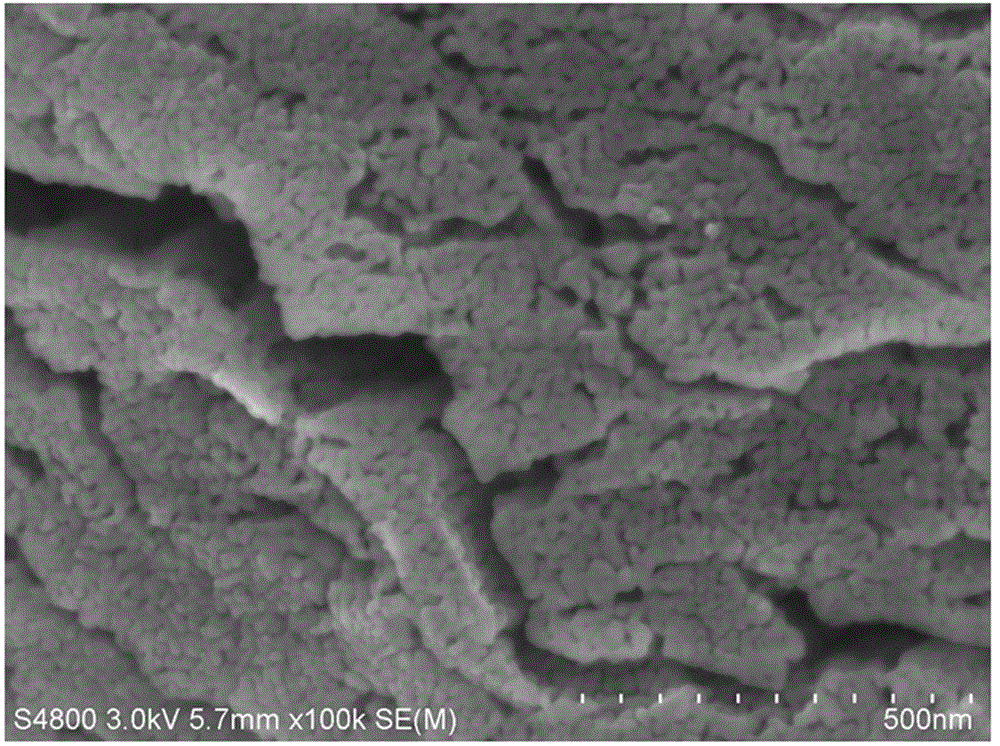

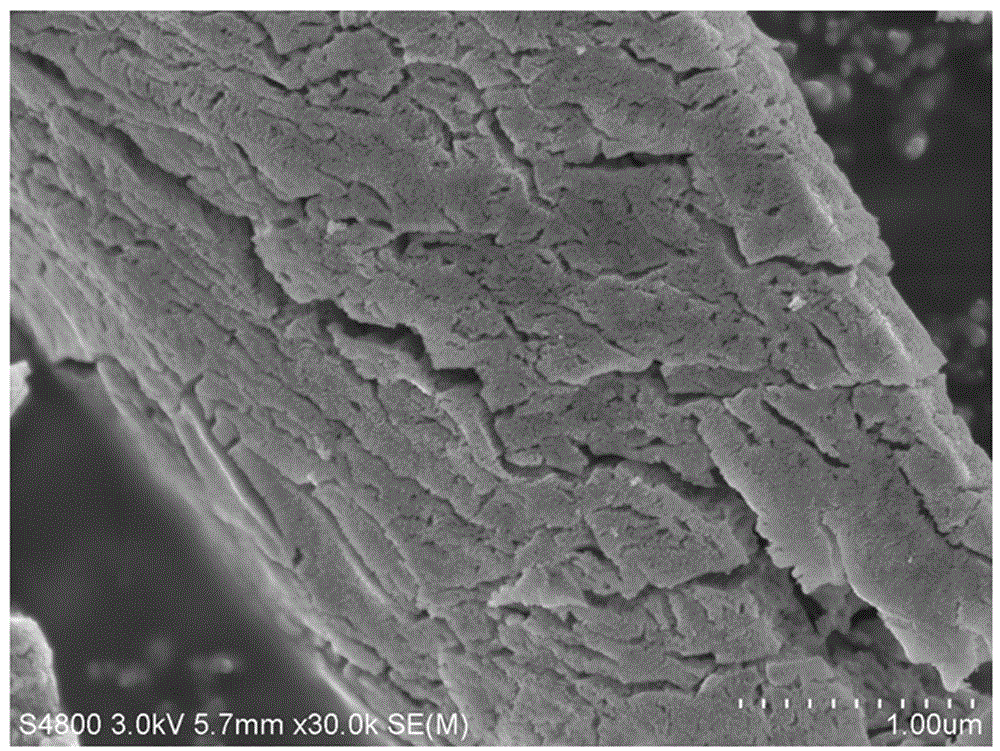

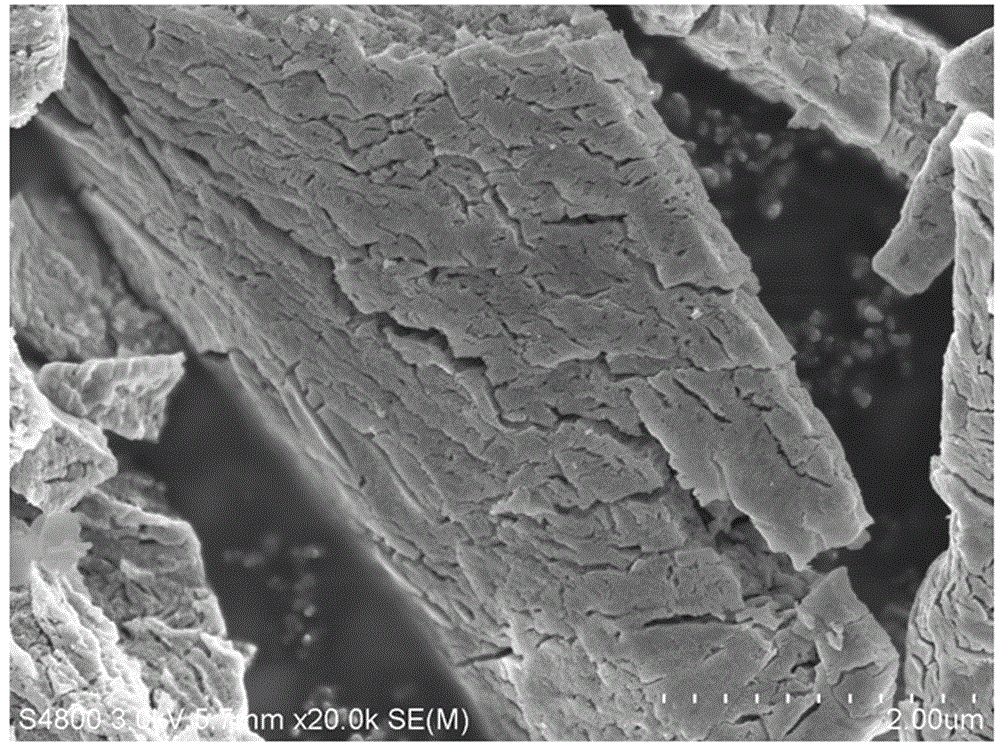

Method for preparing graphene through carrying out ultrasonic stripping on graphite

InactiveCN103253659AReduce craft production costControllableGrapheneHigh concentrationOrganic solvent

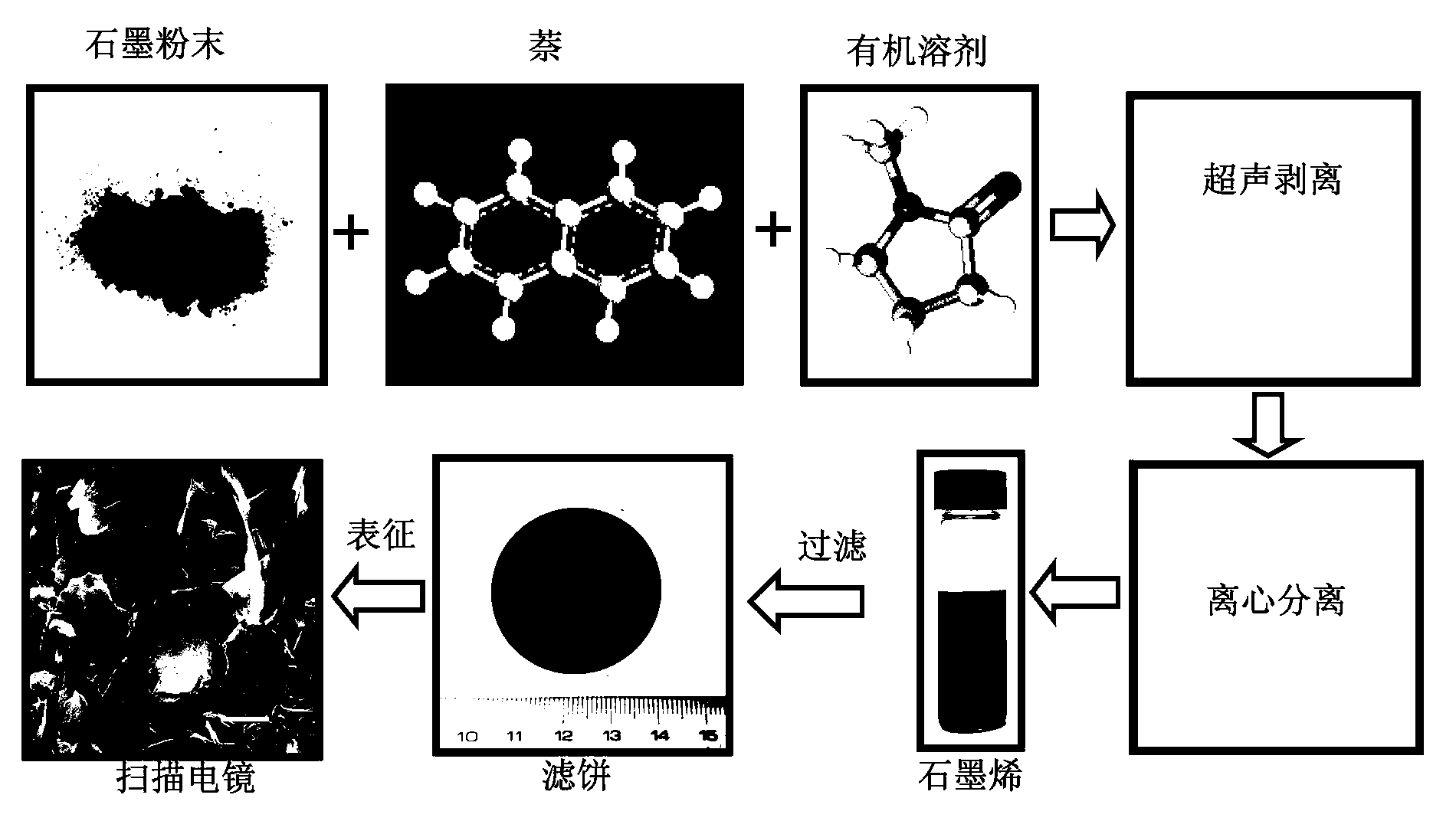

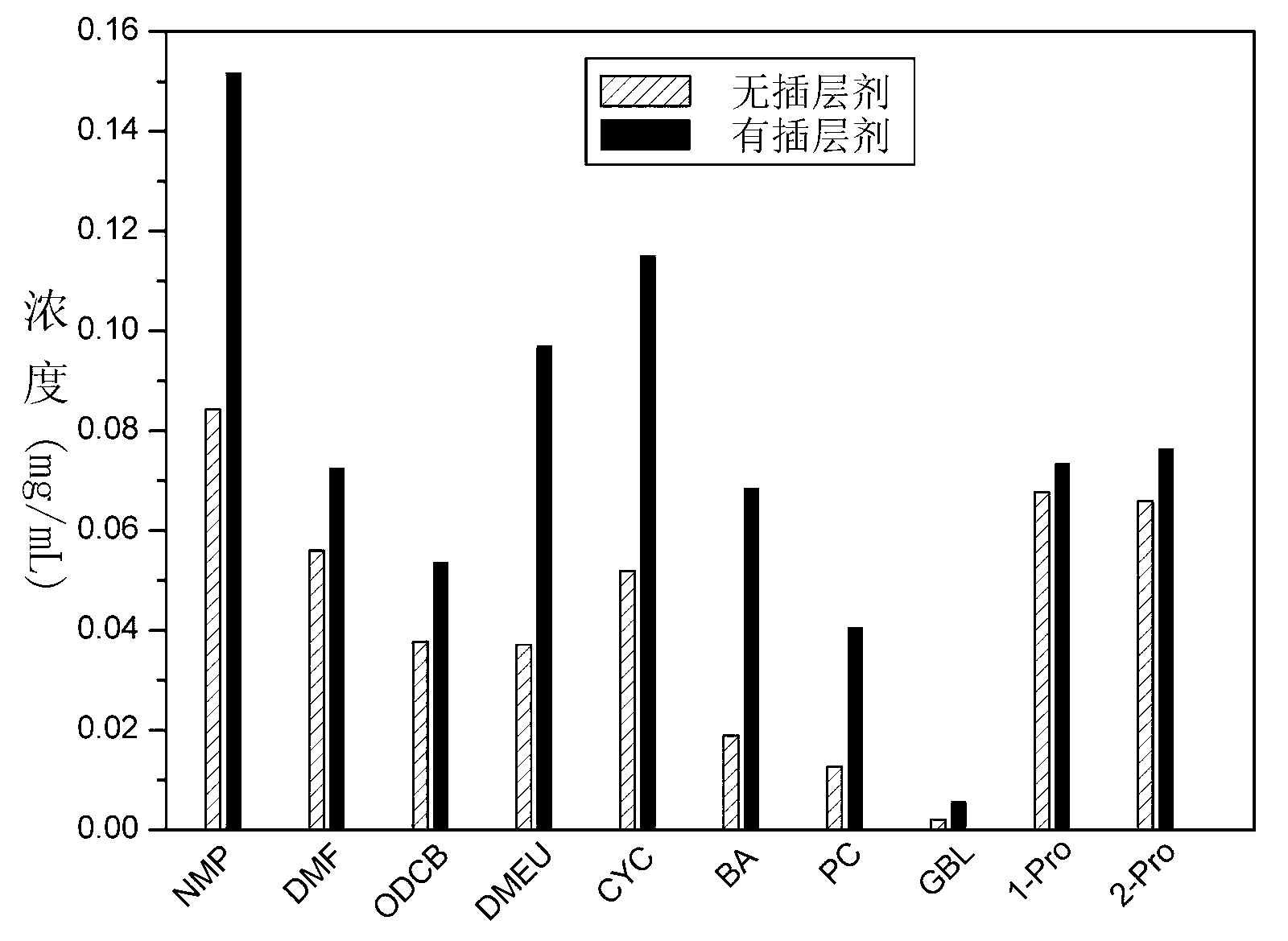

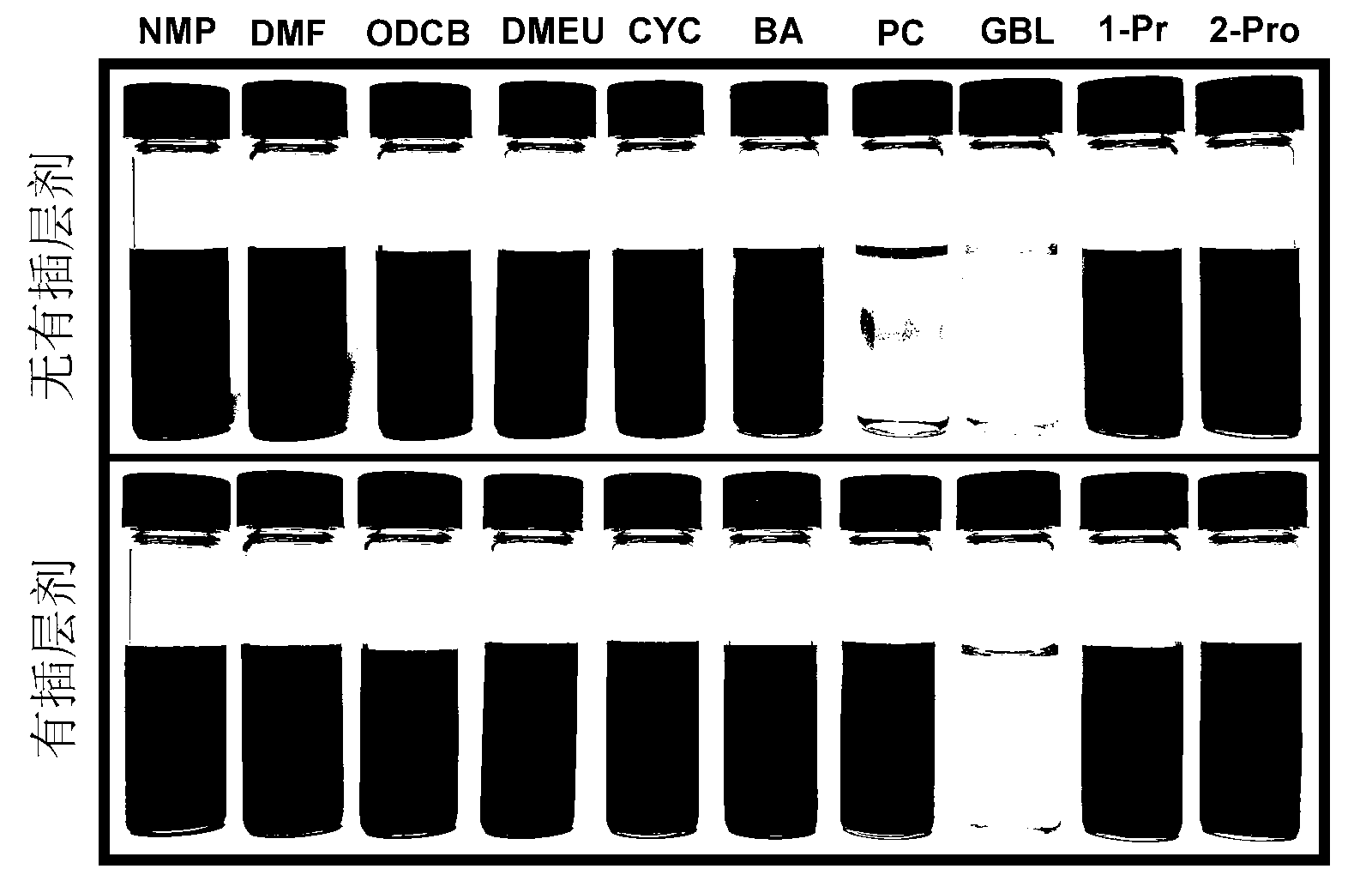

The invention belongs to the technical field of functional material preparation, and relates to a novel method for preparing graphene through carrying out ultrasonic stripping on graphite. The method comprises the following steps: uniformly mixing graphite powder and an intercalator in certain proportion in an organic solvent, carrying out stripping on the obtained mixture a certain time by using an ultrasonic water bath, carrying out centrifugal separation on the obtained object, and filtering the obtained product so as to obtain a graphene material. In the traditional process for preparing graphene through ultrasonic stripping, in the invention, a series of compounds such as naphthalene and the like are taken as an intercalator for preparing graphene. Compared with the prior art, the graphene prepared by using the method disclosed by the invention has the advantages of high quality, excellent performances, less defects, low impurity content, and the like; and especially the method is a physical process, thereby ensuring the perfect performances of the graphene. In addition, the method disclosed by the invention has the advantages of simpleness, easiness for operation, low preparation cost of products, high concentration of synthesized graphene dispersion liquid, and uneasiness for gathering, and has a good application prospect in the photoelectric field of graphene materials.

Owner:BOHAI UNIV

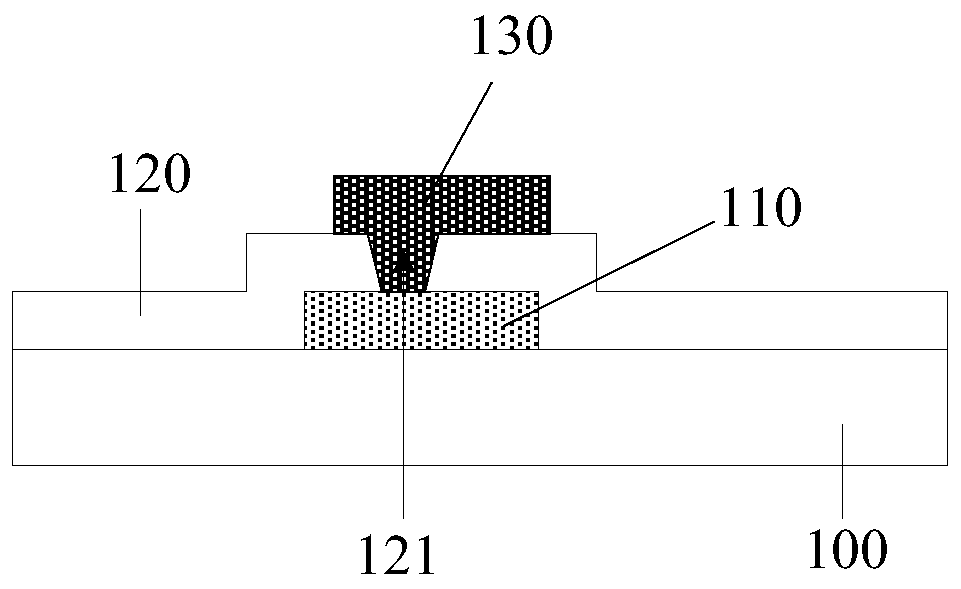

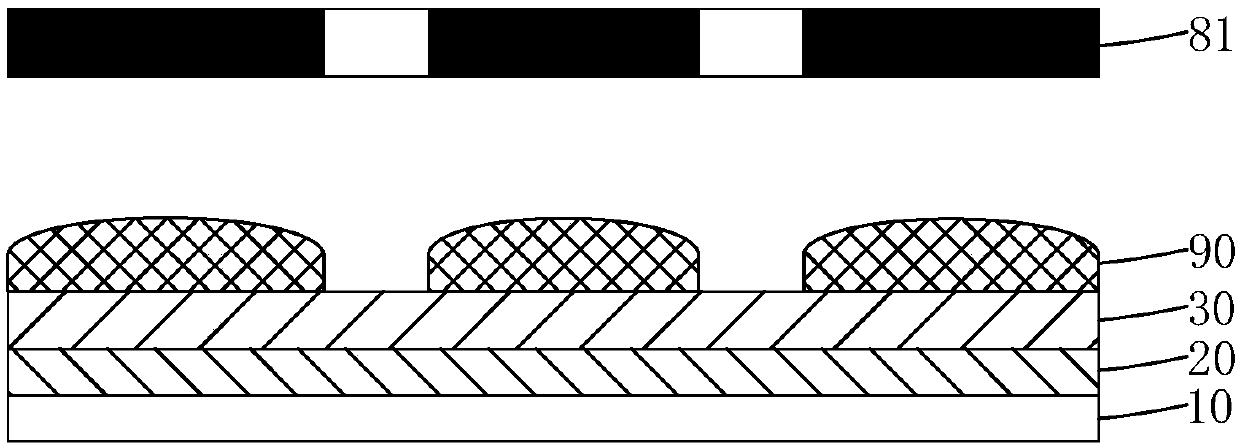

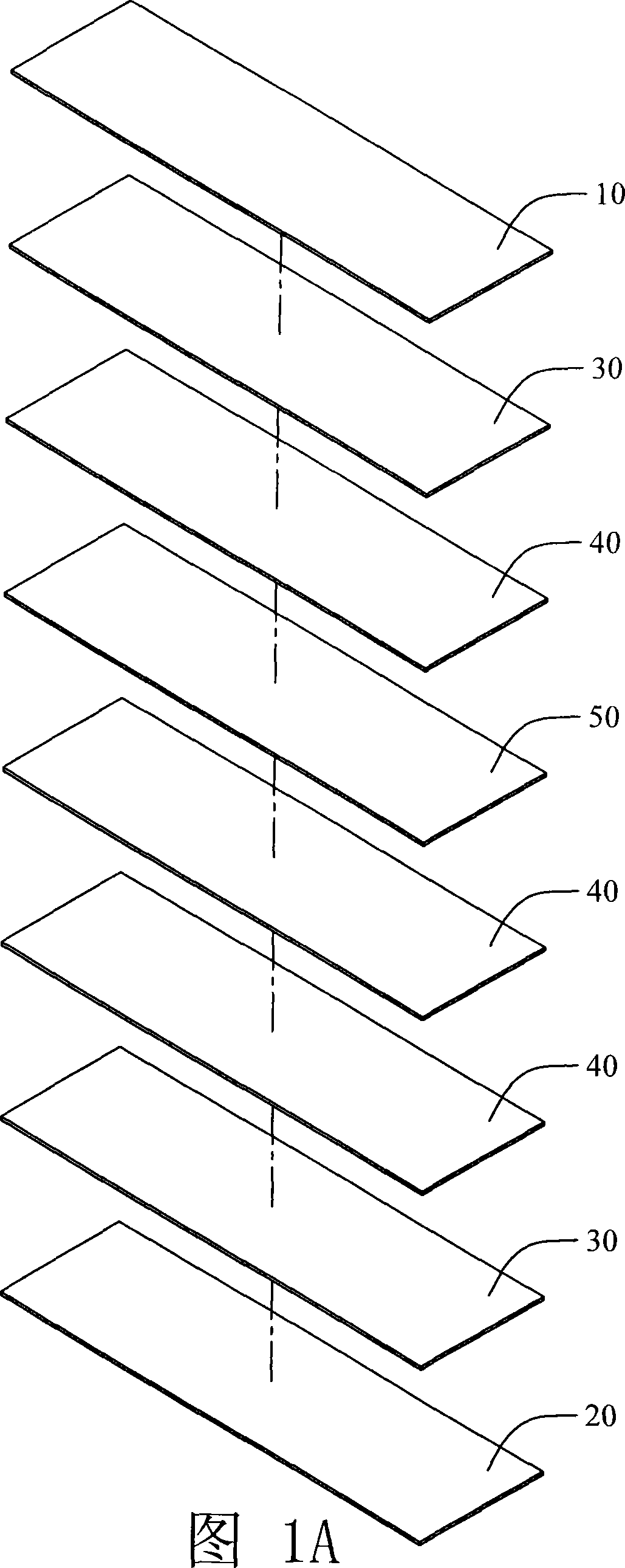

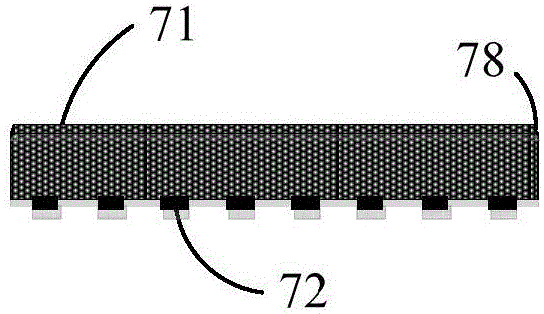

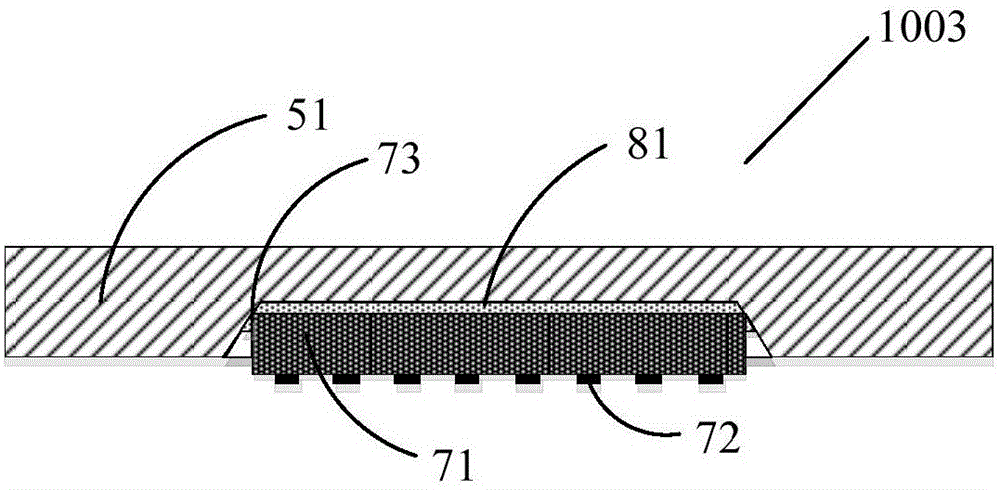

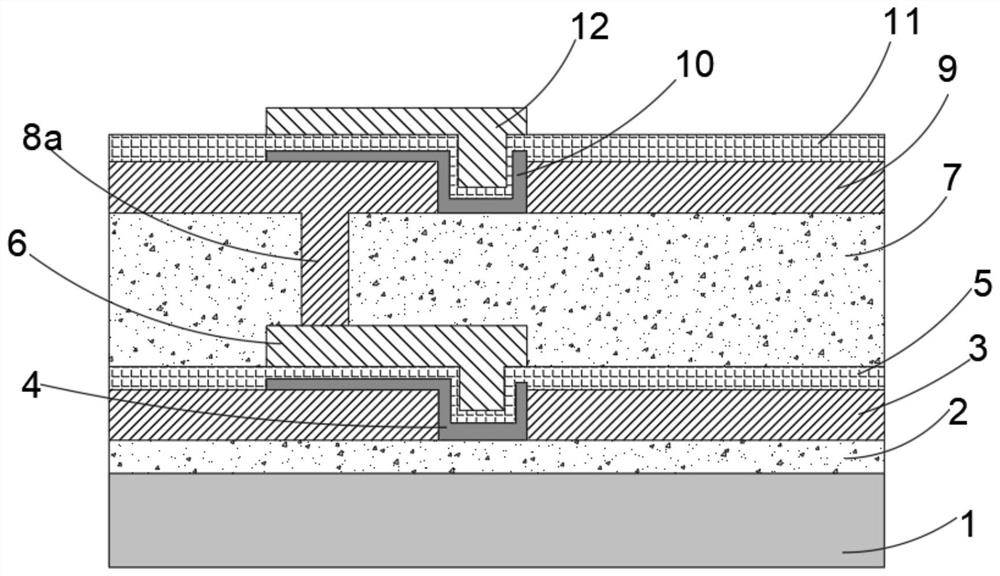

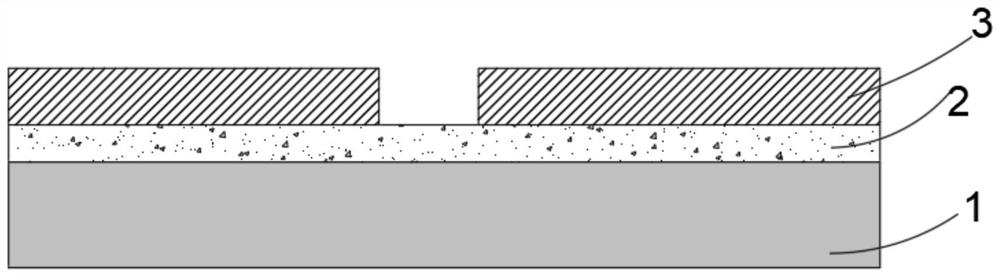

Flexible capacitor type micromachining ultrasonic transducer (CMUT) and preparation method thereof

ActiveCN105413997AOvercome deficienciesOvercoming Bandwidth LimitationsMechanical vibrations separationUltrasonic sensorCoupling

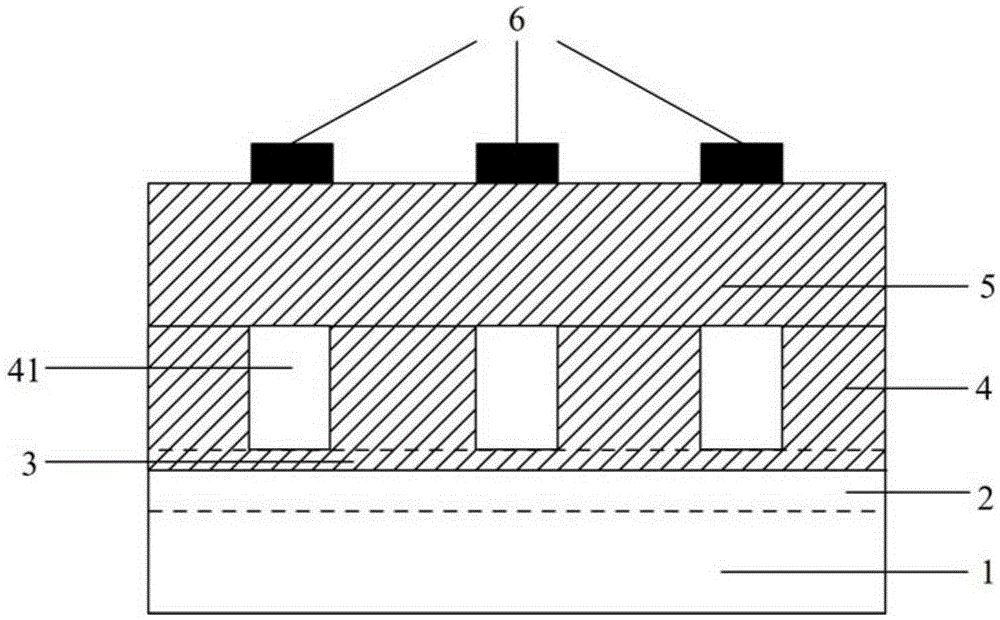

The invention discloses a flexible capacitor type micromachining ultrasonic transducer (CMUT). The flexible CMUT comprises a flexible substrate, a lower electrode, an etching sacrificial layer, an organic polymer support layer, an organic polymer vibration thin film and an upper electrode which are arranged sequentially. The organic polymer support layer is provided with a groove, and the groove and the organic polymer vibration thin film form a cavity of the ultrasonic transducer. The invention further discloses a preparation method of the flexible CMUT. According to the flexible CMUT, ultrasonic loss caused by poor coupling is effectively reduced, and the flexible ultrasonic transducer is achieved. The flexible CMUT is suitable for detection objects, including animals' epidermal tissue, of any shapes, so that the application range of the CMUT is effectively widened. The preparation method is simple in preparation process and low in cost.

Owner:SOUTH CHINA UNIV OF TECH

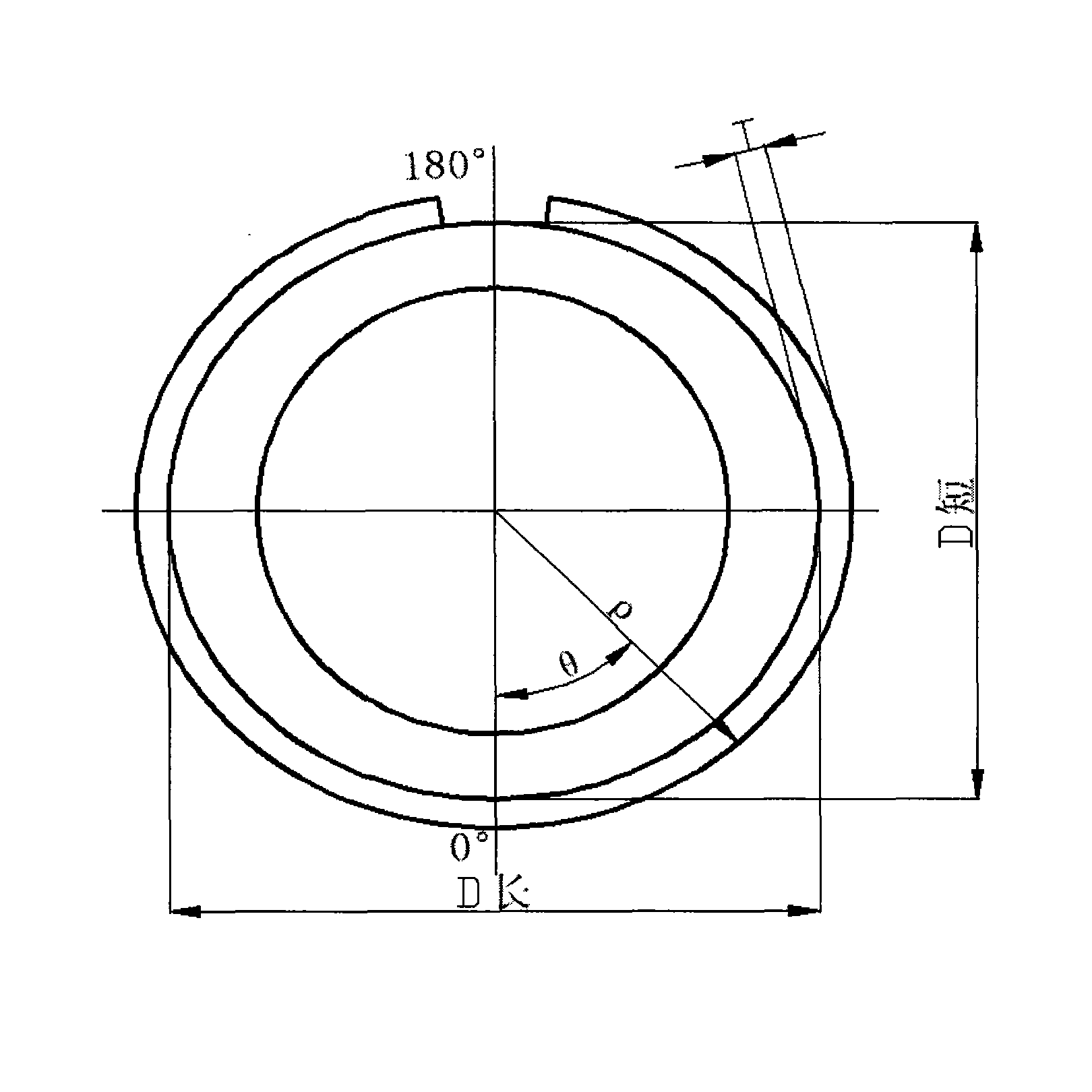

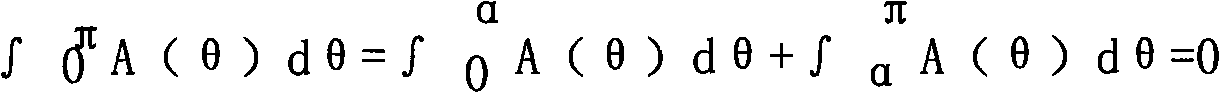

Processing method of steel piston gas ring

ActiveCN101649790ALow yieldSolve the cumbersome machining processPiston ringsMachines/enginesPliabilityProcess manufacturing

The invention discloses a processing method of a steel piston gas ring, which comprises the following steps: winding-destressing-grooving-shaping-top line trimming-flat surface grinding-excircle boning-chroming or nitriding-top line trimming-excircle boning-top line trimming-flat surface grinding; the size of a shaped blank rod is improved by calculating pressure distribution mold lines with different ovality requirements and fully considering the mold line change caused by nitriding shrinkage, thereby the problem of gas ring deformation after procedures, such as nitridation, and the like is greatly reduced, and the finished product ratio of the product is improved. Compared with the defects of long process routes, multi-workshop crossing processing and low comprehensive finished product ratio in the casting iron gas ring, the comprehensive finished product ratio of the steel gas ring processed by using the shaped blank rod can reach up to 95 percent. By utilizing the pliability characteristic of the steel and adopting a shaped steel winding and shaping process, the invention solves the fussy machining process of cast iron material, shortens the manufacturing period, also reduces the procedure waste simultaneously and saves the process manufacturing cost.

Owner:NANJING FAYN PISTON RING

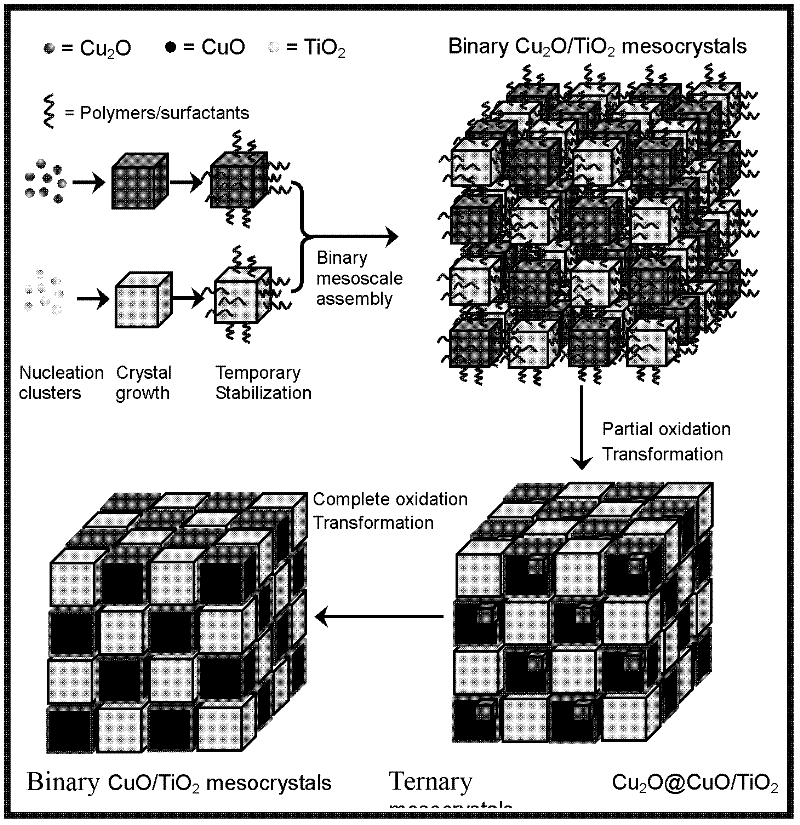

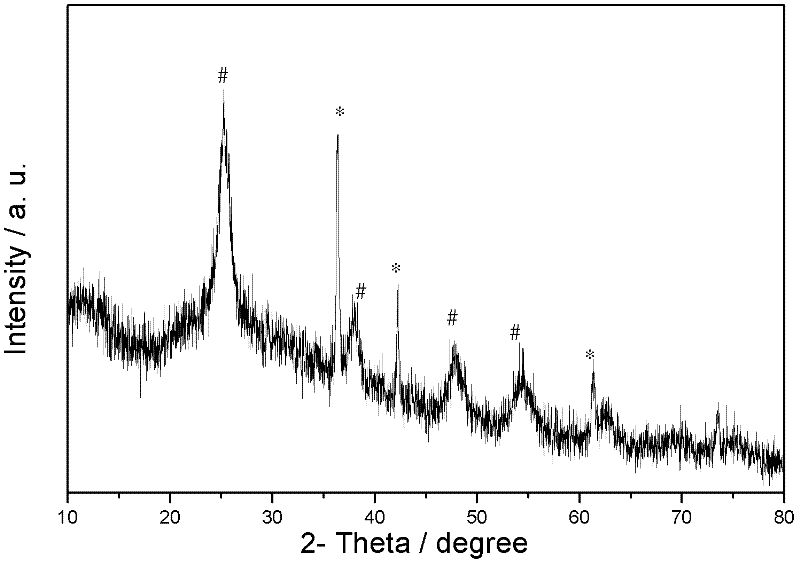

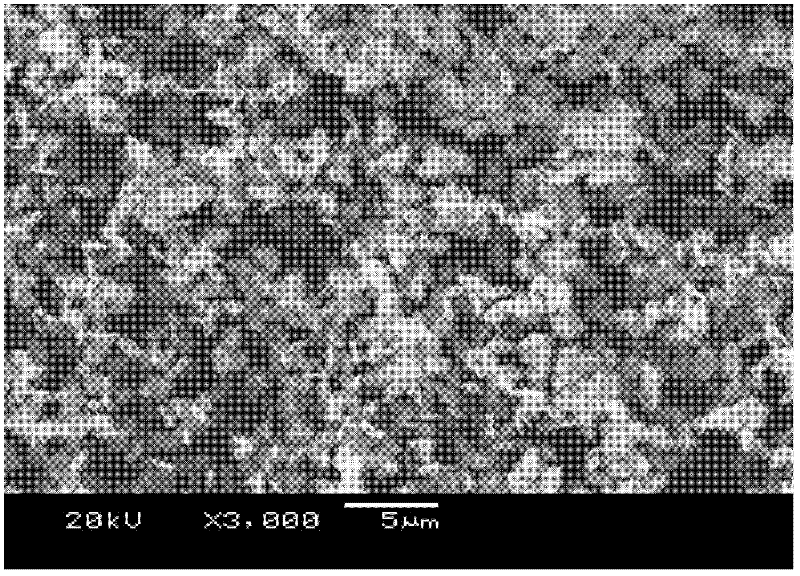

Preparation method of copper-titanium-oxide mesomorphism material

InactiveCN102631919AReduce craft production costControllableWater/sewage treatment by irradiationWater contaminantsMuffle furnaceTitanium oxide

The invention belongs to the technical field of function materials and relates to a preparation method of a copper-titanium-oxide mesomorphism material. The preparation method comprises the following steps of: uniformly dissolving soluble metallic copper slat and titanium salt in a mixed solution of alcohol / water according to a certain proportion, and adding a certain quantity of surfactant in the mixing process; performing hydrothermal reaction, filtering, washing, drying in the mixed solution of alcohol / water continually; and then performing thermal treatment in a muffle furnace to obtain the copper-titanium-oxide mesomorphism material. According to the preparation method, the technology is simple and convenient, the purity of the prepared material is high, the content of impurities is low, the preparation cost of the material is low, the performance of the material is excellent, and thus the material can be subjected to industrialized mass production. The copper-titanium-oxide mesomorphism material prepared by the method can serve as a photochemical catalyst responsive to visible light, and has wide application prospect in the fields of degradation of dyeing waste water and indoor harmful gas, photochemical catalysis disinfection and the like.

Owner:BOHAI UNIV

Preparation method of nickel titanate/titanium dioxide composite nanomaterial

InactiveCN105905940AReduce craft production costControllableTitanium dioxideMetal/metal-oxides/metal-hydroxide catalystsCross-linkDyeing wastewater

The invention belongs to the technical field of functional materials, and relates to a preparation method of a nickel titanate / titanium dioxide composite nanomaterial. The method comprises the following steps: dissolving and uniformly mixing nickel acetylacetonate and titanium acetylacetonate in an alcohol solution, carrying out a cross-linking reaction at a certain temperature, and carrying out heat treatment in a muffle furnace to obtain the nickel titanate / titanium dioxide composite nanomaterial. The preparation method is simple and easy, and the nickel titanate / titanium dioxide composite nanomaterial has the advantages of high purity, low content of impurities, low preparation cost, excellent performances, and realization of industrial batch production. The nickel titanate / titanium dioxide composite nanomaterial prepared in the invention has high catalysis activity as a photocatalytic material, and has wide application prospects in the field of degradation of dye wastewater and indoor harmful gases and the field of photocatalytic disinfection.

Owner:BOHAI UNIV

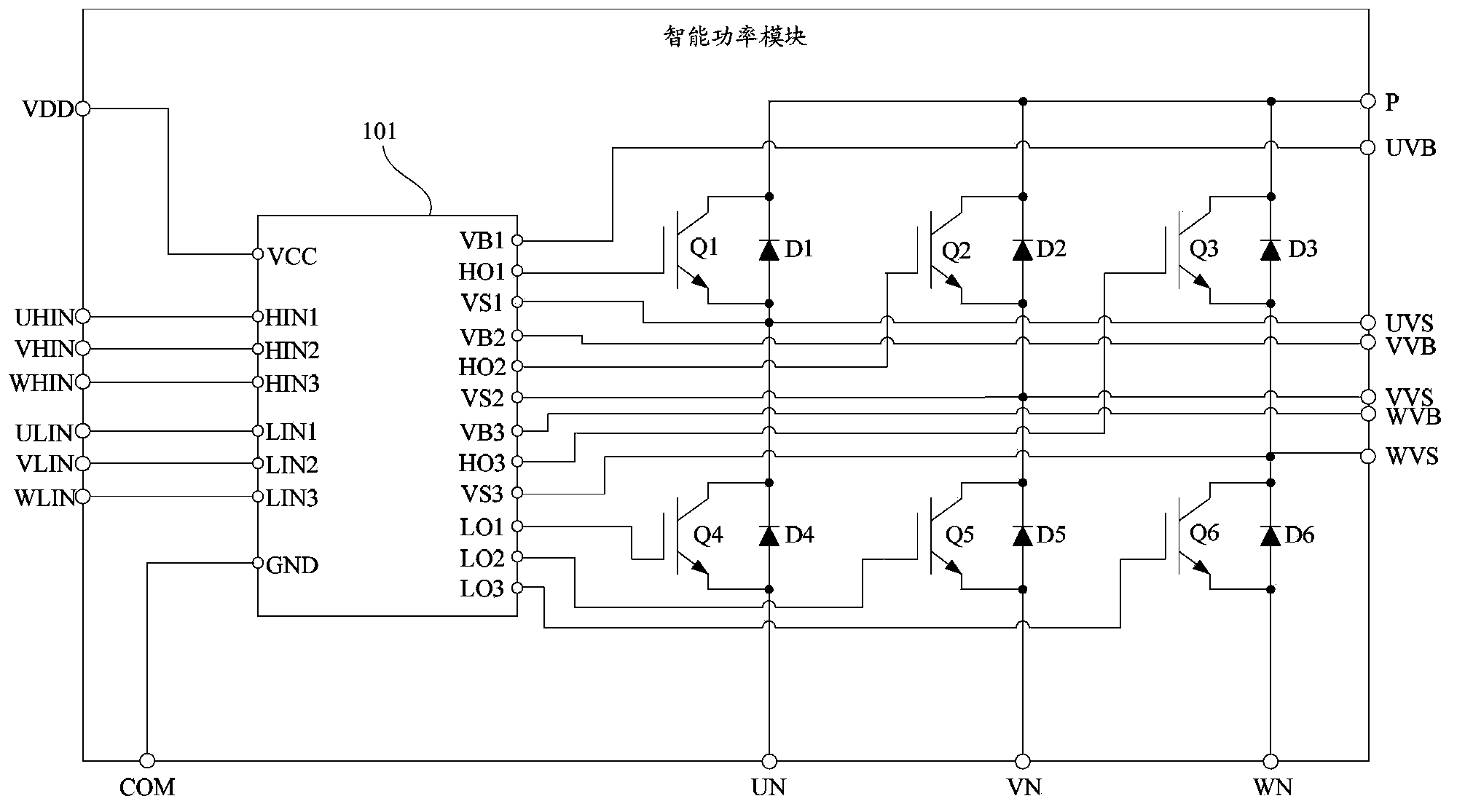

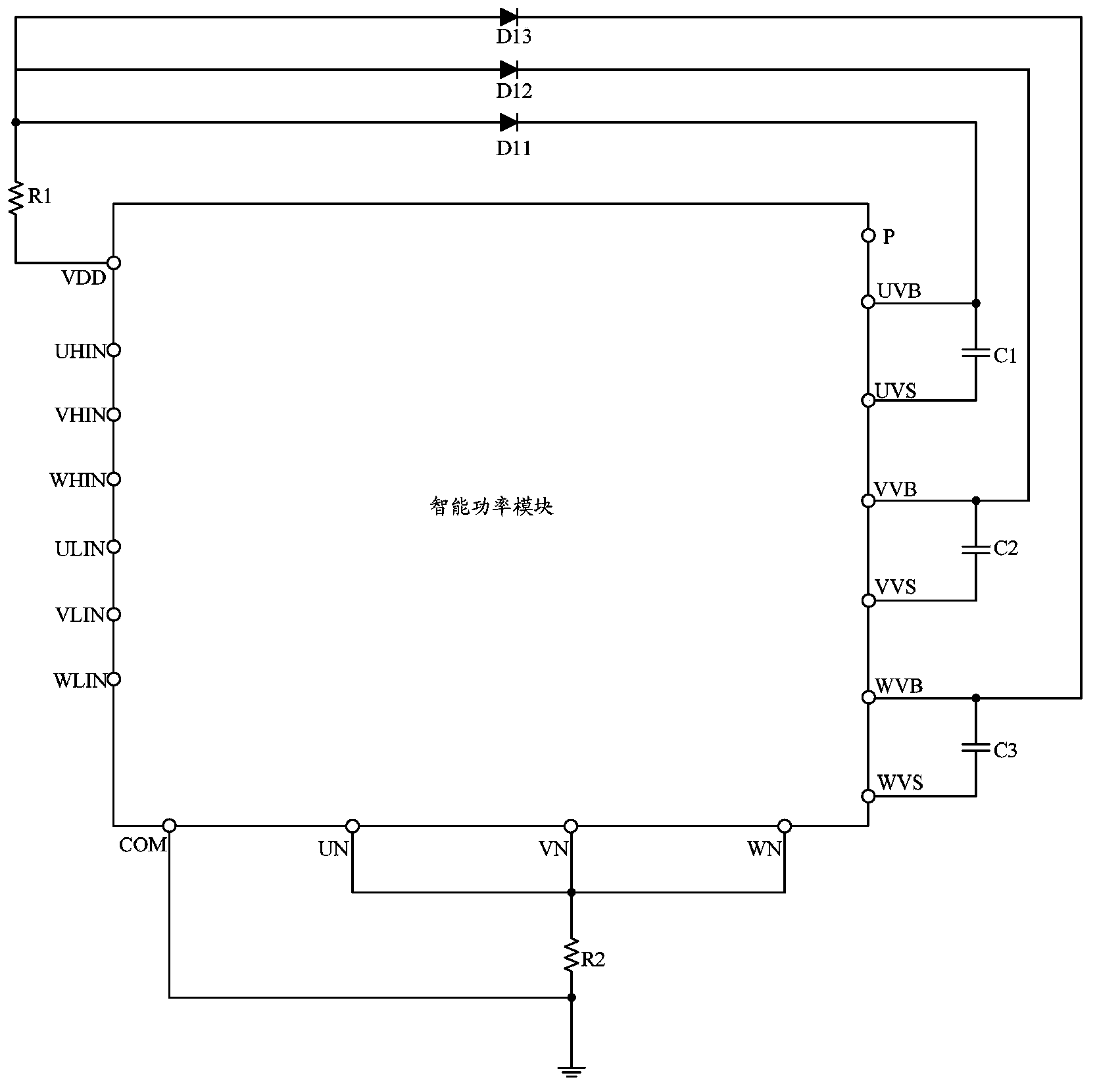

Intelligent power module

ActiveCN104113191AImprove securityReduce manufacturing costPower conversion systemsLow voltageCircuit noise

The invention belongs to the field of power drive control, and provides an intelligent power module. An input circuit, a U-phase upper bridge arm output circuit, a V-phase upper bridge arm output circuit, a W-phase upper bridge arm output circuit, a U-phase lower bridge arm output circuit, a V-phase lower bridge arm output circuit and a W-phase lower bridge arm output circuit are adopted in the intelligent power module so that each IGBT tube is driven by an independent circuit, a jumper wire between the circuit and the gate electrode of the IGBT tube is effectively reduced, gate electrode inductance is reduced, circuit noise is reduced, and thus switching speed of the IGBT tubes is enhanced. Besides, switching time of the IGBT tubes of upper and lower bridge arms are maintained to be consistent without conduction at the same time so that safety of the intelligent power module is enhanced. Furthermore, the U-phase lower bridge arm output circuit, the V-phase lower bridge arm output circuit and the W-phase lower bridge arm output circuit are low-voltage area circuits so that technical manufacturing cost is relatively low, and thus manufacturing cost of the overall intelligent power module can be substantially reduced.

Owner:GD MIDEA AIR-CONDITIONING EQUIP CO LTD

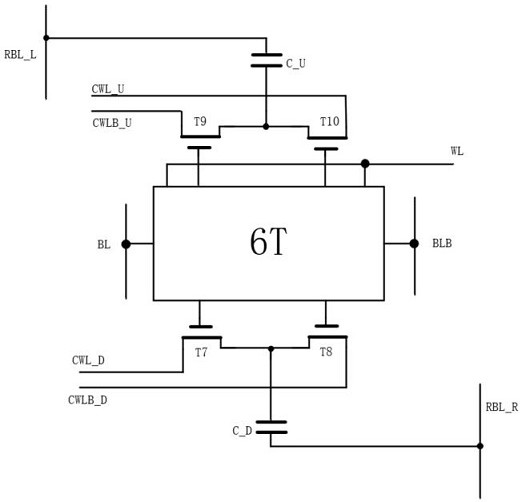

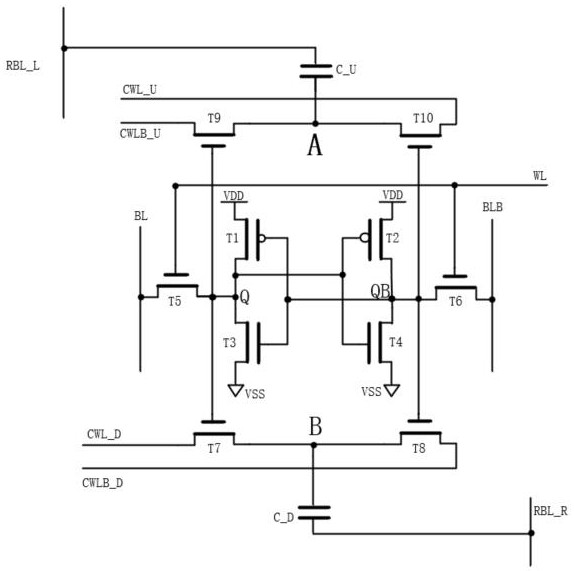

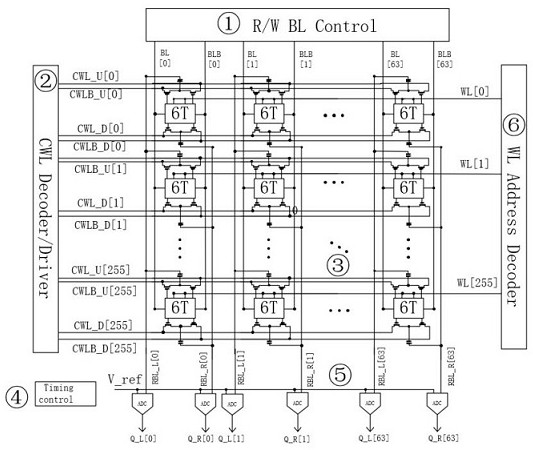

6T unit-based storage unit, storage array and in-memory computing device

ActiveCN112133348AImprove computing powerReduce craft production costDigital storageCapacitanceBit line

The present invention relates to a 6T unit-based storage unit. The storage unit comprises a PMOS transistor T1, a PMOS transistor T2, an NMOS transistor T3, an NMOS transistor T4, an NMOS transistor T5, an NMOS transistor T6, an NMOS transistor T7, an NMOS transistor T8, an NMOS transistor T9, an NMOS transistor T10, a capacitor C_U, a capacitor C_D, a word line WL, a bit line BL, a bit line BLB,a bit reading line RBL_L, a computing word line CWL_U, a differential signal end CWLB_U, a computing word line CWL_D, a differential signal end CWLB_D and a bit reading line RBL_R. The circuit is conducted only when the voltages at the two ends of the capacitor are changed in the calculation process, the power consumption is saved through a capacitance coupling calculation mode, and the energy efficiency is improved.

Owner:中科南京智能技术研究院

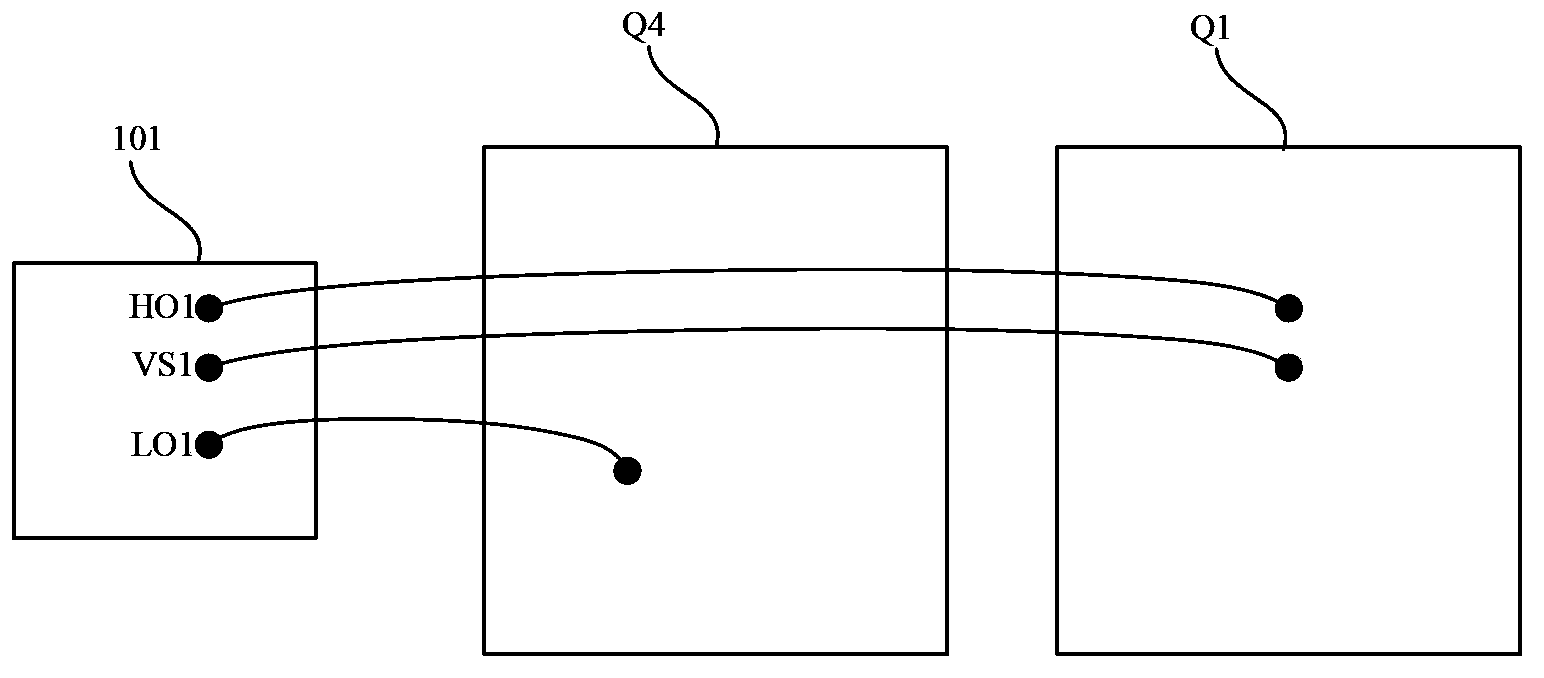

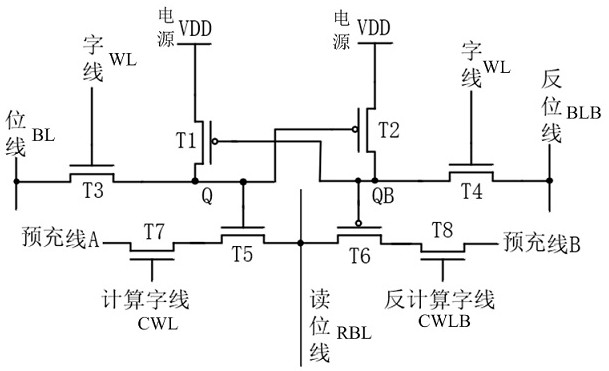

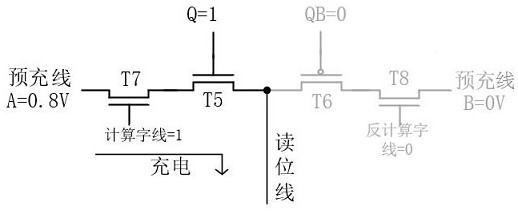

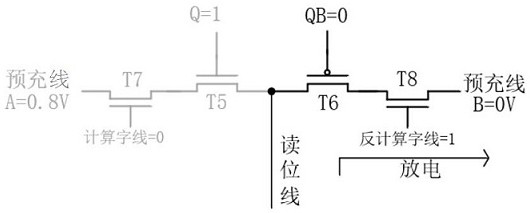

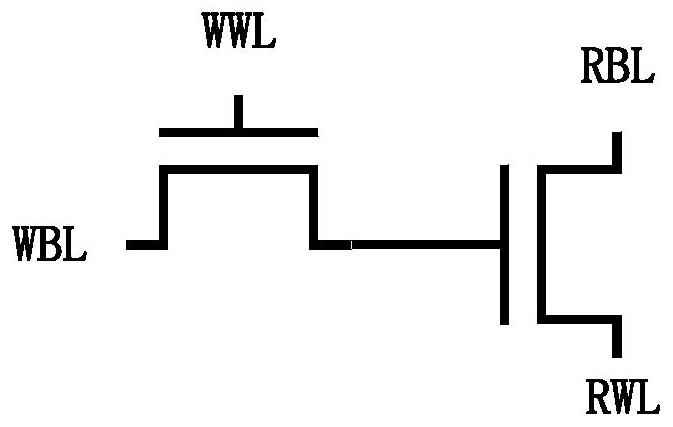

In-memory computing bit unit and in-memory computing device

ActiveCN112558919ANo read and write interferenceReduce craft production costDigital data processing detailsPhysical realisationComputation processEngineering

The invention relates to an in-memory calculation bit unit and an in-memory calculation device, the in-memory calculation bit unit comprises a four-tube storage unit and a four-tube calculation unit,the four-tube calculation unit comprises a transistor T5, a transistor T6, a transistor T7 and a transistor T8; the drain electrode of the transistor T7 is connected with a pre-storage line A, the grid electrode of the transistor T7 is connected with a calculation word line, the source electrode of the transistor T7 is connected with the drain electrode of the transistor T5, the grid electrode ofthe transistor T5 is connected with the four-tube storage unit, the source electrode of the transistor T5 is connected with the source electrode of the transistor T6, and the grid electrode of the transistor T6 is connected with the four-tube storage unit; the drain electrode of the transistor T6 is connected with the drain electrode of the transistor T8, the grid electrode of the transistor T8 isconnected with the inverse calculation word line, and the source electrode of the transistor T8 is connected with the pre-storage line B; and the source electrode of the transistor T5 and the sourceelectrode of the transistor T6 are connected with a read bit line RBL. When the weight value is designed to be 0, the retention state is directly adopted, and the calculation process is accelerated.

Owner:中科南京智能技术研究院

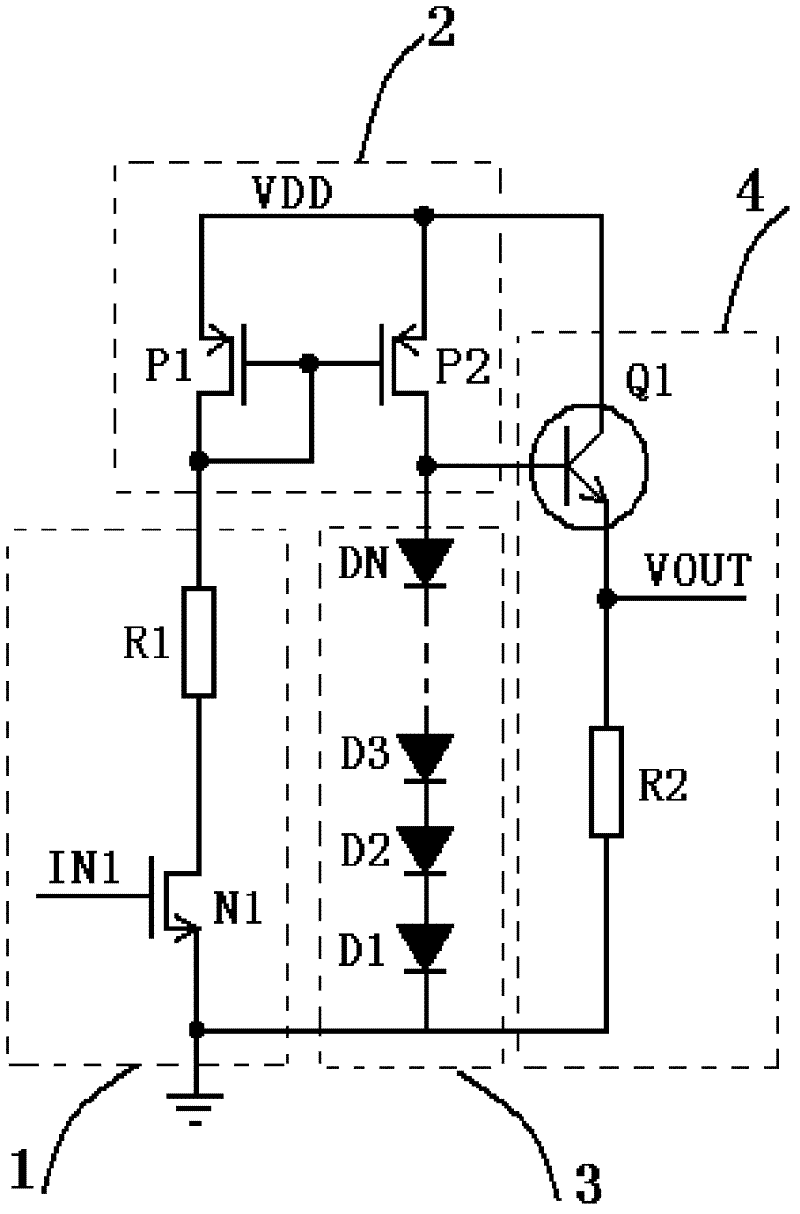

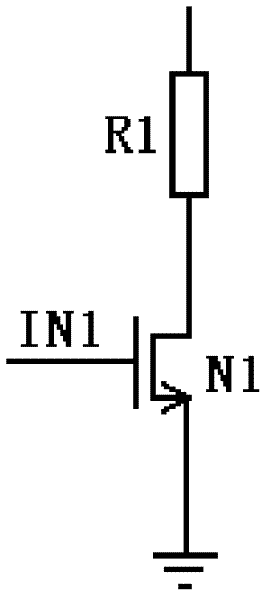

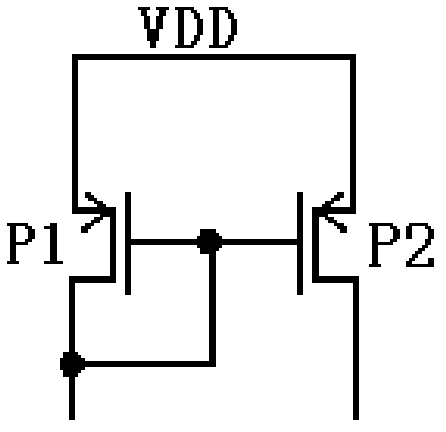

Circuit converting high-voltage power supply into low-voltage power supply for enabling zero switching current of chip

InactiveCN102364851ASafe and reliable workSimple structureDc-dc conversionElectric variable regulationPower flowLow voltage

The invention discloses a circuit converting a high-voltage power supply into a low-voltage power supply for enabling zero switching current of a chip. The circuit comprises an enabling control circuit, a high-voltage PMOS (P-channel Metal Oxide Semiconductor) tube proportion current mirror, a diode series connection network and a current amplifying and outputting circuit. According to the circuit disclosed by the invention, the low-voltage power supply which is converted from the high-voltage power supply and is required by a chip enabling module is realized by directly adopting a general device in a high-voltage process without a special device. The invention has the technical characteristics that: in the circuit disclosed by the invention, the high-voltage power supply is converted into the low-voltage power supply without a traditional architecture consuming quiescent current or the special device; the same function is achieved by adopting the most general device in the high-voltage process, so that the manufacturing cost of the process can be reduced; meanwhile, the quiescent current can be ensured to be zero when the chip is positioned in an enabling switching state; in addition, a low-voltage output power supply has basically no fluctuation along with the change of the high-voltage power supply; and stable voltage output and safety and reliability for work are achieved.

Owner:WUXI CHIPOWN MICROELECTRONICS

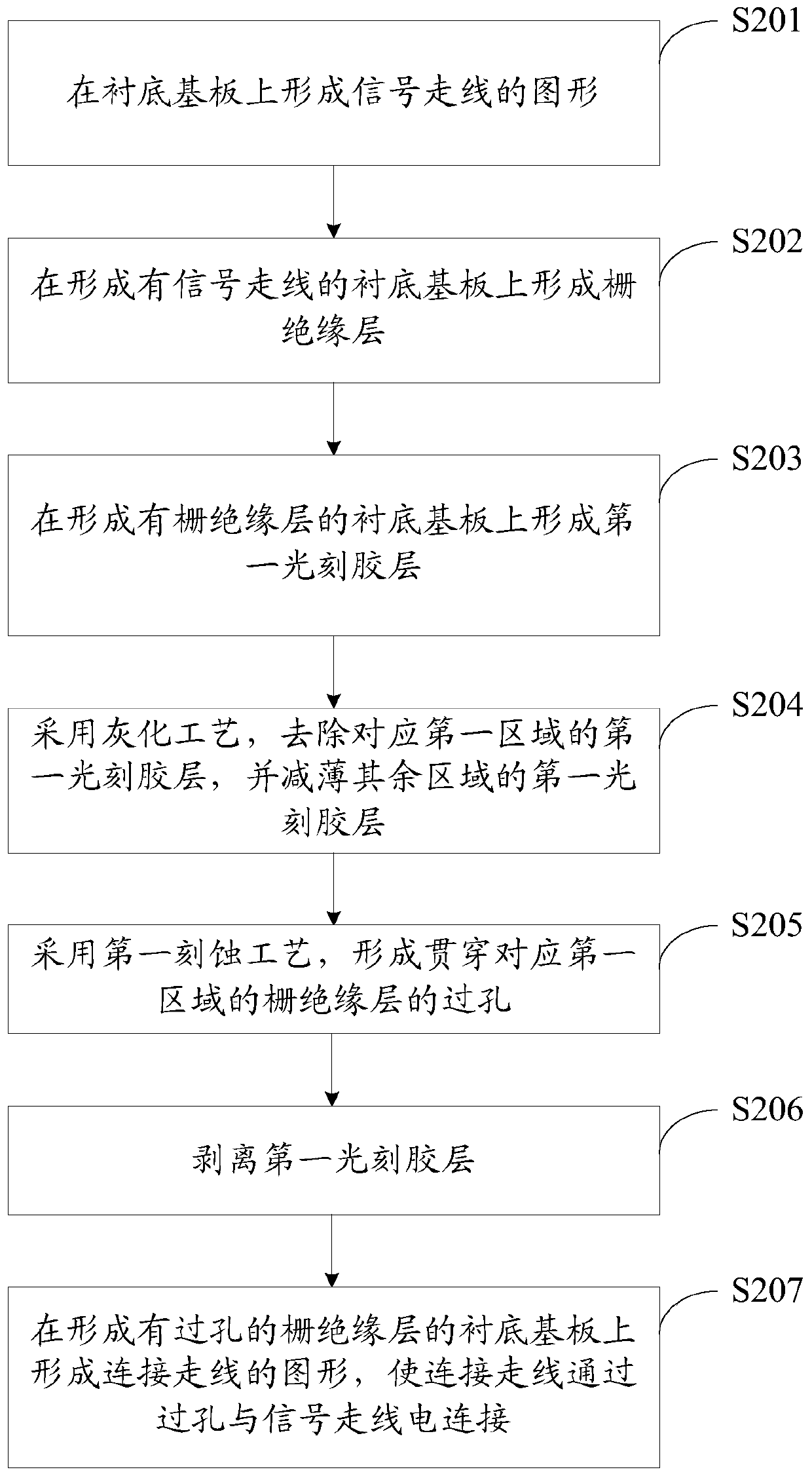

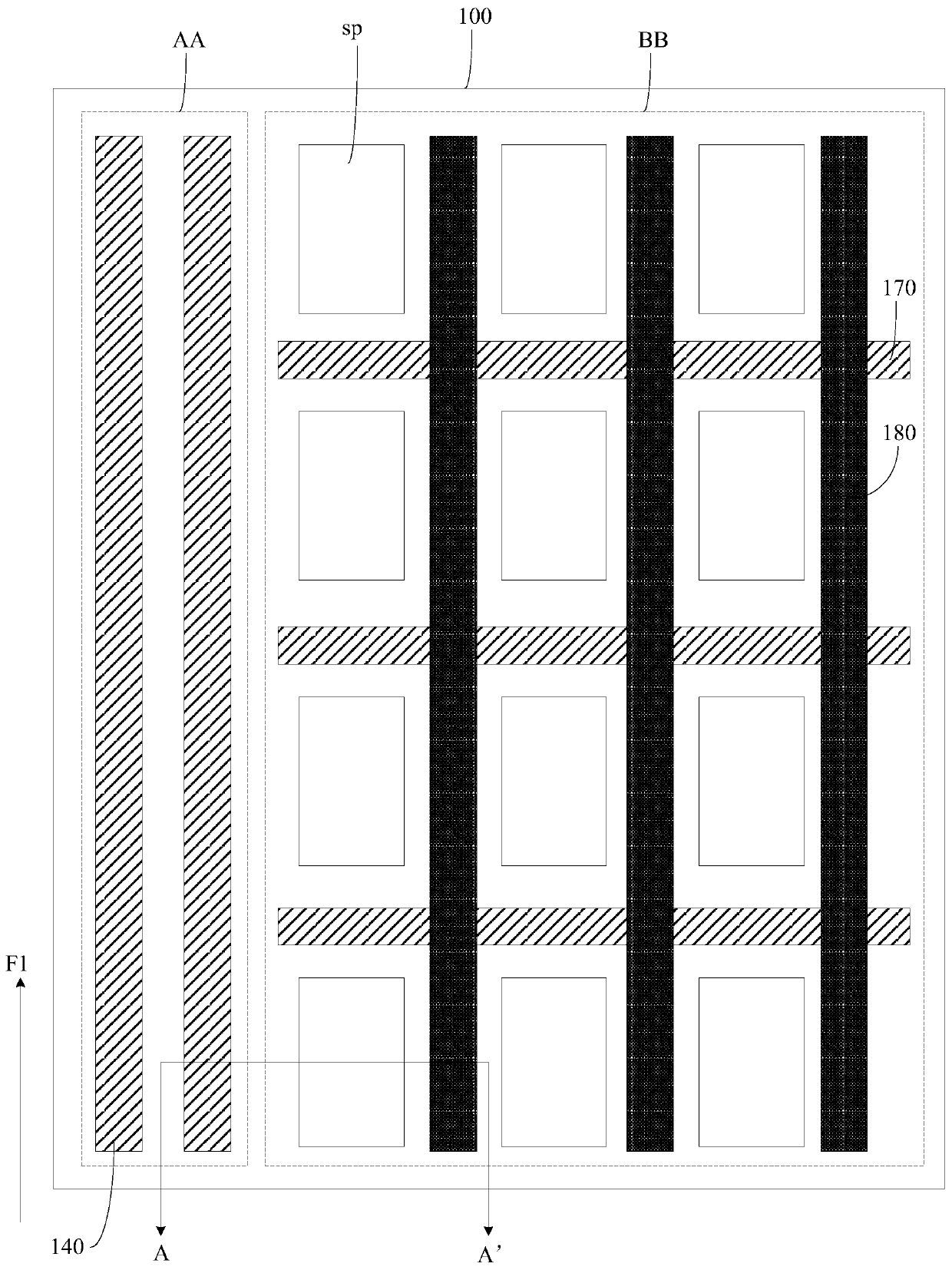

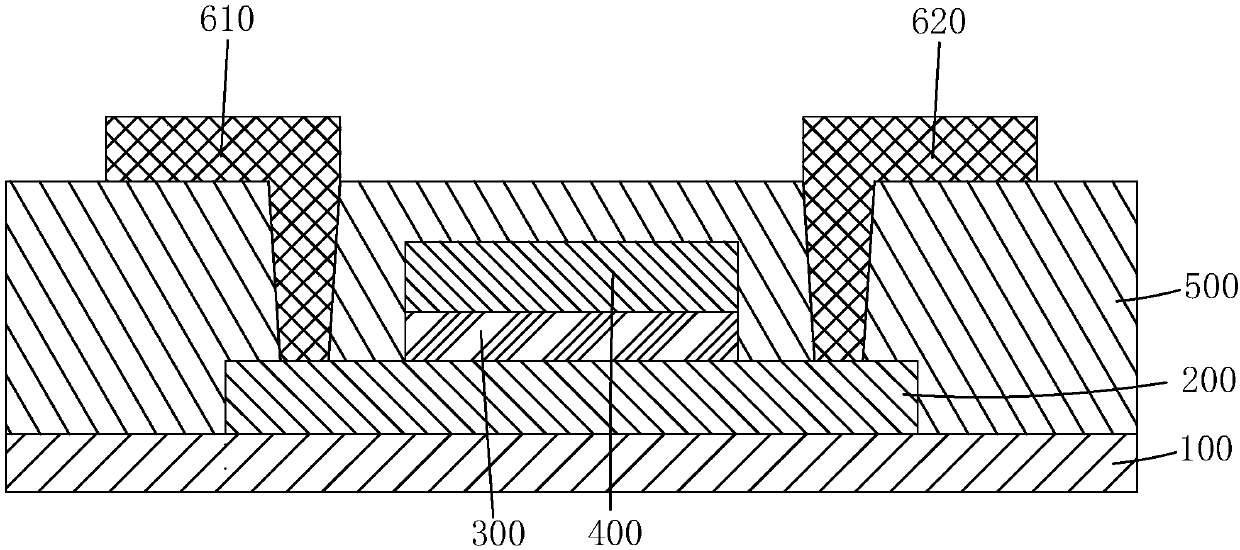

Array substrate, preparation method thereof and display device

ActiveCN109935516ALiquidReduce craft production costSolid-state devicesSemiconductor/solid-state device manufacturingDisplay devicePhotoresist

The invention discloses an array substrate, a preparation method thereof, and a display device. The thickness of a first region of a cross section, perpendicular to an extending direction of a signalline, of the signal line is greater than the thickness of a second region, so after a gate insulating layer and a first photoresist layer are formed, the thickness of the first photoresist layer corresponding to the first region can be less than the thickness of the other regions because the material of the first photoresist layer has flowability. In this way, the first photoresist layer is processed through the ashing technology, the first photoresist layer corresponding to the first area is removed and only the first photoresist layer in the rest areas is thinned, so that the gate insulatinglayer corresponding to the first area is directly exposed, and a via hole is formed through the etching technology. Therefore, the first photoresist layer above the first region corresponding to thesignal line can be removed without a mask plate, so that the gate insulating layer forms a via hole, thereby saving a mask plate, and reducing the process preparation cost.

Owner:BOE TECH GRP CO LTD +1

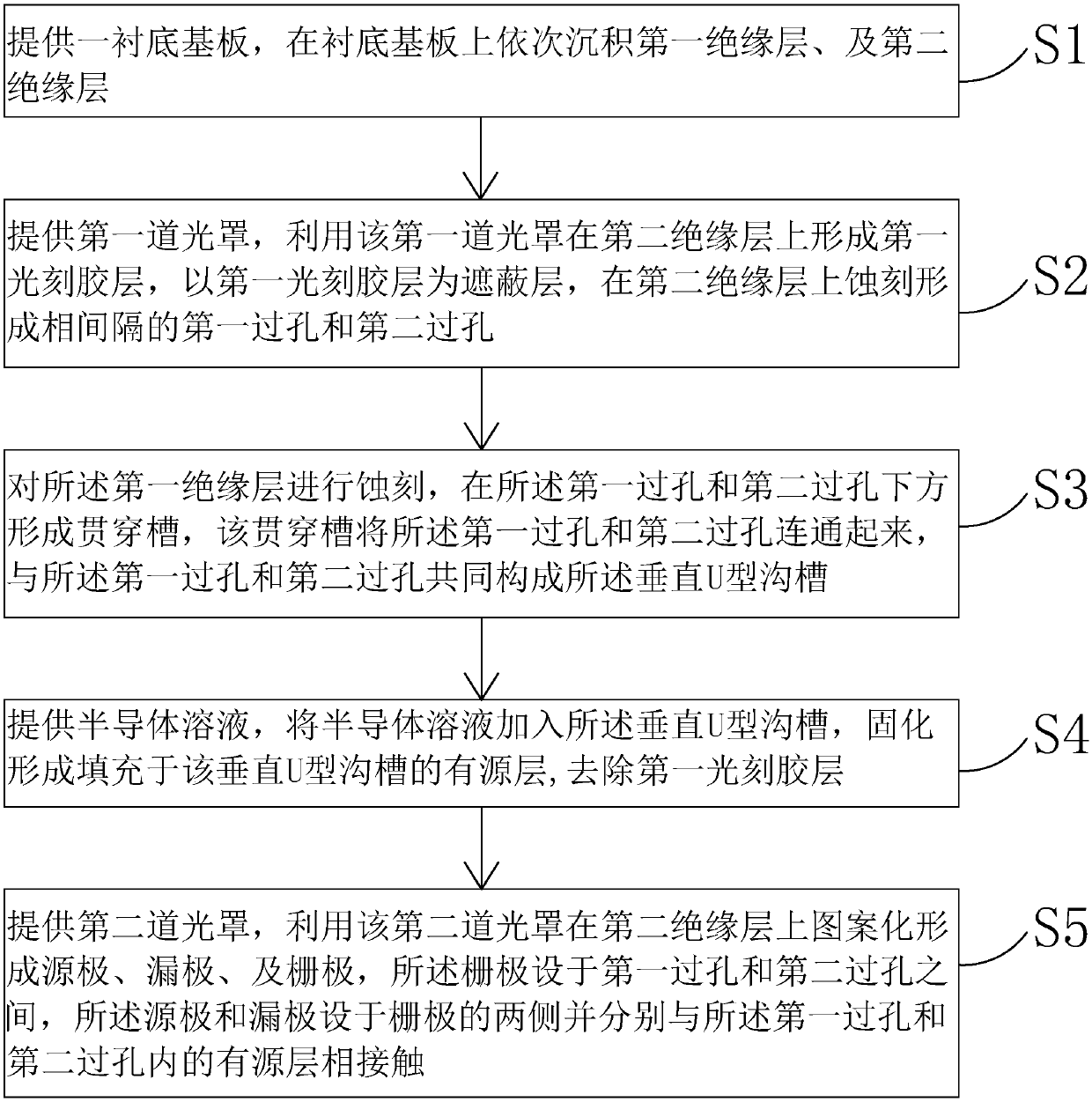

Manufacturing method of top gate type thin film transistor and top gate type thin film transistor

ActiveCN107946368ASimple structureReduce the number of processesTransistorSemiconductor/solid-state device manufacturingInsulation layerProcess manufacturing

The present invention provides a manufacturing method of a top gate type thin film transistor and a top gate type thin film transistor. The manufacturing method of the top gate type thin film transistor comprises the steps of: forming a first insulation layer and a second insulation layer on a substrate in order; employing a first photomask to form a first via hole and a second via hole which arearranged on the second insulation layer at intervals; forming a penetrating groove below the first via hole and the second via hole on the first insulation layer, wherein the penetrating groove is configured to communicate the first via hole with the second via hole, and the penetrating groove, the first via hole and the second via hole commonly form a vertical U-shaped groove; filling and formingan active layer in the vertical U-shaped groove; and employing a second photomask to form a source electrode, a drain electrode and a grid electrode on the second insulation layer. The manufacturingmethod of the top gate type thin film transistor and the top gate type thin film transistor simplifies the structure of the top gate type thin film transistor and reduces the number of photomask manufacture procedures, two photomasks are only used to complete manufacturing of the top gate type thin film transistor with the vertical U-shaped groove, and therefore, the process manufacturing cost issaved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Preparation method of titanium dioxide/copper oxide composited oxide nanometer material

InactiveCN106391014AReduce craft production costControllableWater/sewage treatment by irradiationWater treatment compoundsCross-linkCopper oxide

The invention belongs to the technical field of functional material preparation and relates to a preparation method of a titanium dioxide / copper oxide composited oxide nanometer material. The preparation method includes: dissolving copper acetylacetonate in a DMF (dimethyl formamide) solution for solvothermal reaction to obtain the DMF solution of nanocrystalline cuprous oxide after cooling; dissolving tetrabutyl titanate in an oxalic acid aqueous solution, adding DMF solution of nanocrystalline cuprous oxide, drying out solvent under conditions of heating and stirring, and performing cross-linking reaction to obtain the dioxide / copper oxide composited oxide nanometer material after heat treatment on a muffle furnace. The preparation method is simple and easy to implement, the nanometer material is high in purity, even in dispersion, low in impurity content, low in product preparation cost and good in performance; titanium dioxide / copper oxide composited oxide nanometer material serving as the photocatalyst material has high catalytic activity, and wide application prospect is achieved in the fields of degrading dye wastewater and indoor harmful gas, photo-catalytic disinfection and the like.

Owner:BOHAI UNIV

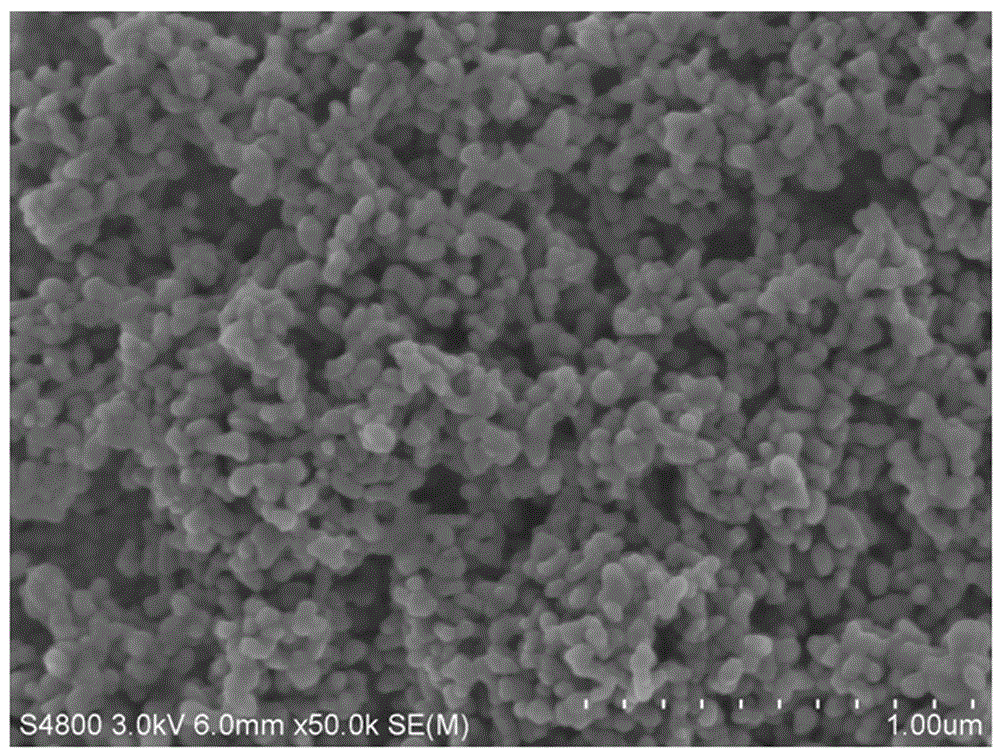

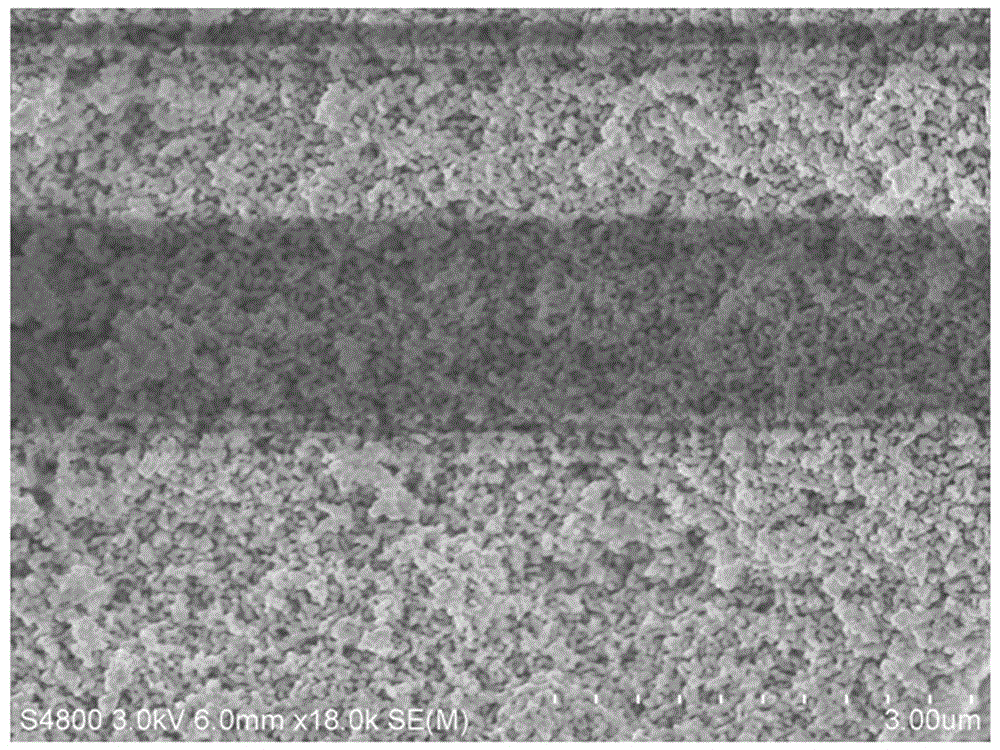

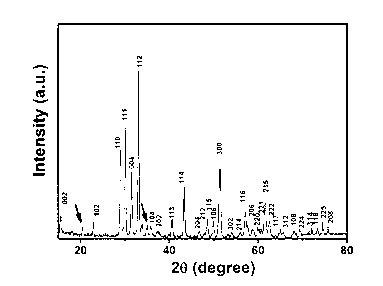

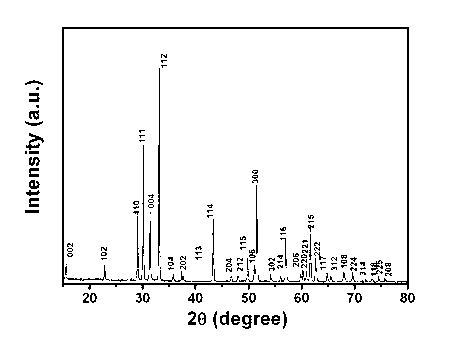

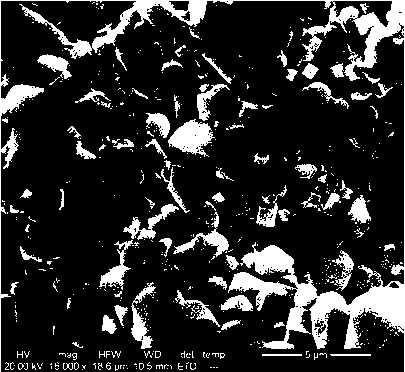

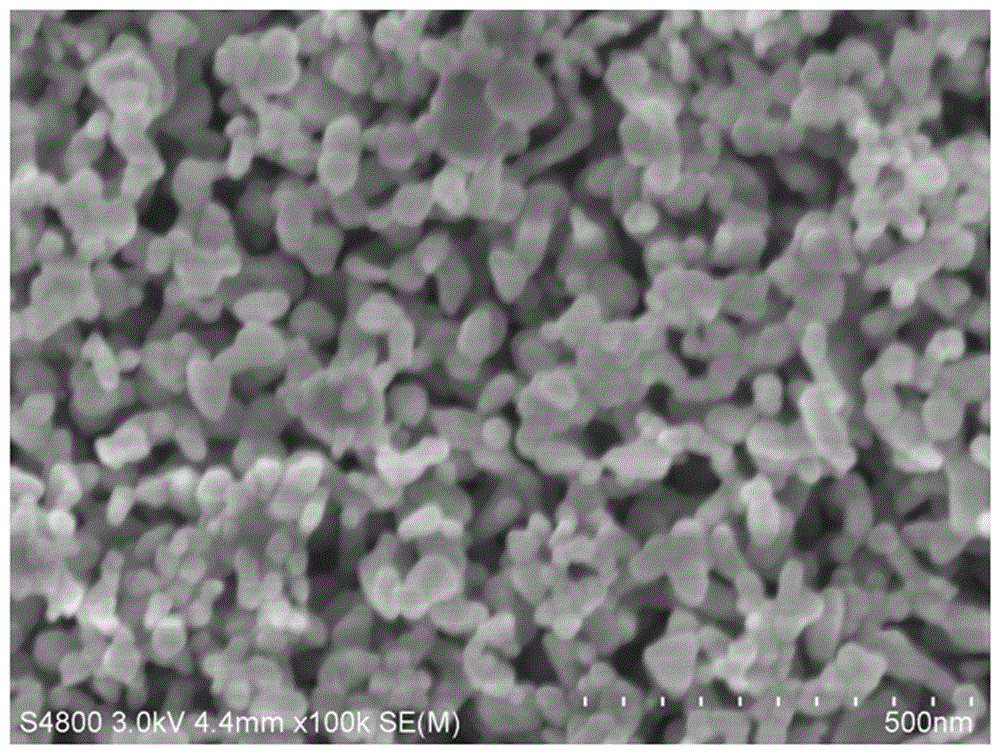

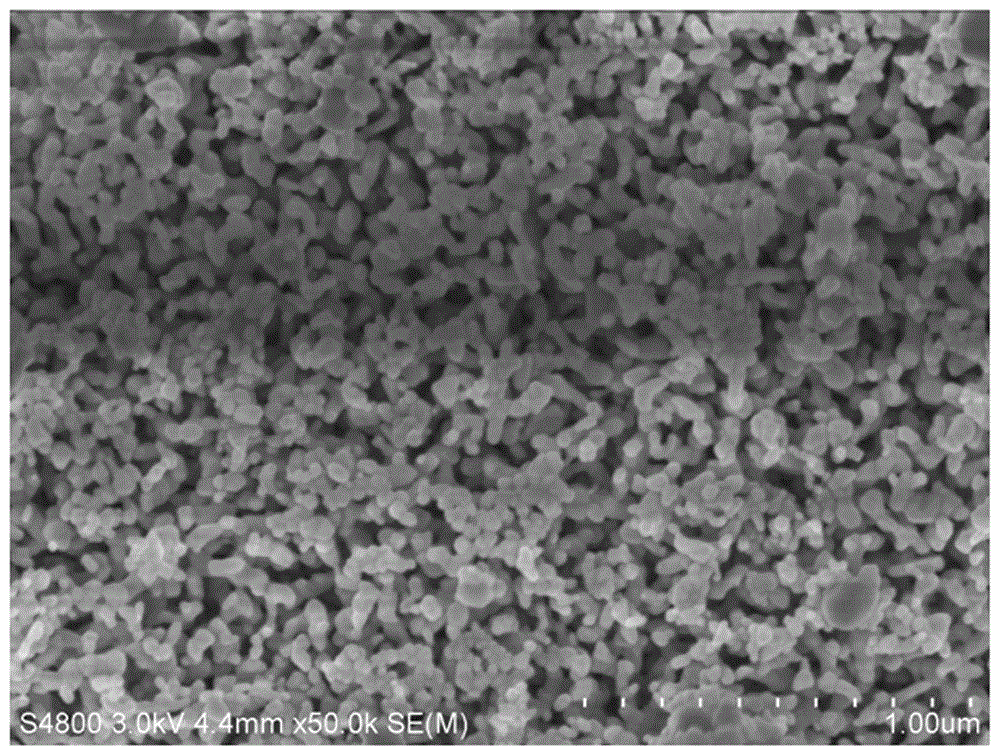

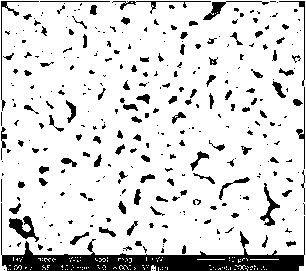

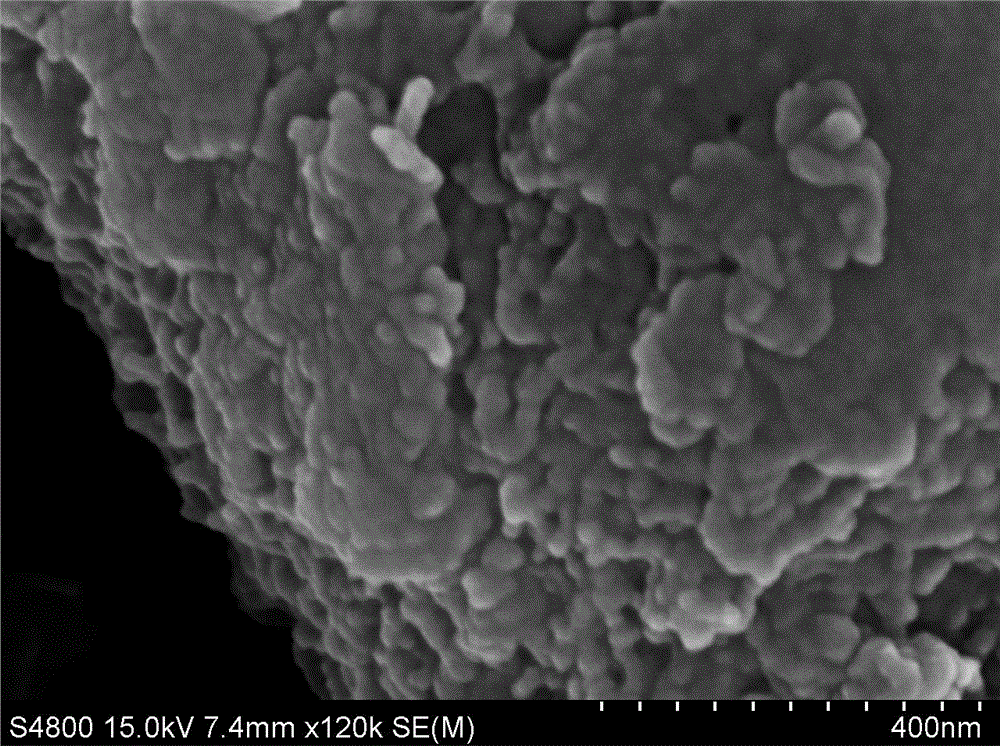

Preparation method of manganese sesquioxide hierarchical-structure material

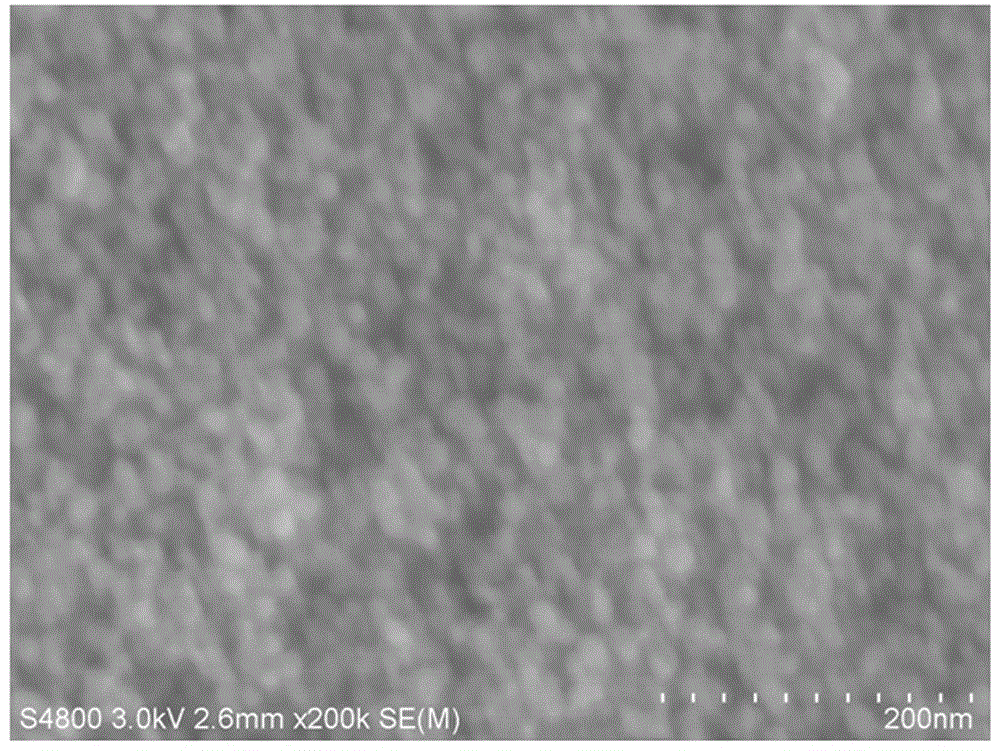

InactiveCN105883924ALarge specific surface areaMany gapsMaterial nanotechnologyHybrid capacitor electrodesCapacitanceSesquioxide

The invention belongs to the technical field of functional material preparation and relates to a preparation method of a manganese sesquioxide hierarchical-structure material. The method comprises the following steps: dropwise adding a soluble manganese salt aqueous solution into an oxalic acid aqueous solution; reacting at constant temperature under a stirring condition until precursor precipitate is generated; and after the reaction is over, filtering, washing, drying and calcining to obtain the manganese sesquioxide hierarchical-structure material. The product is a flaky hierarchical-structure material formed by assembling a large quantity of manganese oxide nano particles. The flake size is 10-20mu m, and the size of the manganese oxide nano particles is 20-30nm. With low preparation cost and easiness in operation control, the technology has relatively high production efficiency and can realize industrial mass production. The manganese sesquioxide hierarchical-structure material prepared by the preparation method is used as an electrode material and has relatively high specific capacitance and good cycle performance.

Owner:BOHAI UNIV

Lithium-sulfur battery and preparation method thereof

ActiveCN104659422AReduce process manufacturing costs and raw material usage costsReduce use costCell electrodesFinal product manufactureElectrical batteryAnode

The invention belongs to the field of lithium-sulfur batteries and particularly relates to a preparation method of a lithium-sulfur battery and the lithium-sulfur battery prepared by adopting the method. When the method provided by the invention is used for preparing the lithium-sulfur battery, a polymer component is only introduced in a cathode of the lithium-sulfur battery, a polymer is not introduced in an anode electrode, and a solvent for configuring polymer slurry is selected from components in an electrolyte of the lithium-sulfur battery. Thus, the content of the polymer component can be introduced as small as possible, the solvent residues caused by using other solvents are avoided, and thus the lithium-sulfur battery has better performance.

Owner:GUANGDONG ZHUGUANG NEW ENERGY TECH

High-strength and high-toughness silicon carbide ceramic bearing plate, manufacturing method and application thereof

The invention discloses a high-strength and high-toughness silicon carbide ceramic bearing plate, a manufacturing method and application thereof. The silicon carbide ceramic bearing plate is preparedfrom the following materials in parts by mass: 70-95 parts of silicon carbide, 2-10 parts of silicon carbide whiskers, 1 to 15 parts of tungsten carbide, 0.5 to 5 parts of boron carbide, 1 to 10 partsof a binder and 0.5 to 10 parts of a lubricant. The manufacturing method comprises burdening, mixing, pulping, spray drying, isostatic pressing, sintering and finish machining. The silicon carbide ceramic bearing plate is applied to the assembly of chemical-mechanical polishing devices. According to the silicon carbide ceramic bearing plate made by the manufacturing method, the strength and toughness are greatly superior to a common corundum ceramic bearing plate at present; a ceramic bearing plate with the same size can be reduced by 1 / 3 in thickness; the ceramic bearing plate is applied tothe chemical-mechanical polishing devices, the stability in the polishing process is greatly improved, the reliability in the operation process is greatly increased, the service life of the ceramic bearing plate is greatly prolonged, and the process manufacturing cost is reduced.

Owner:NANTONG SANZER PRECISION CERAMICS CO LTD

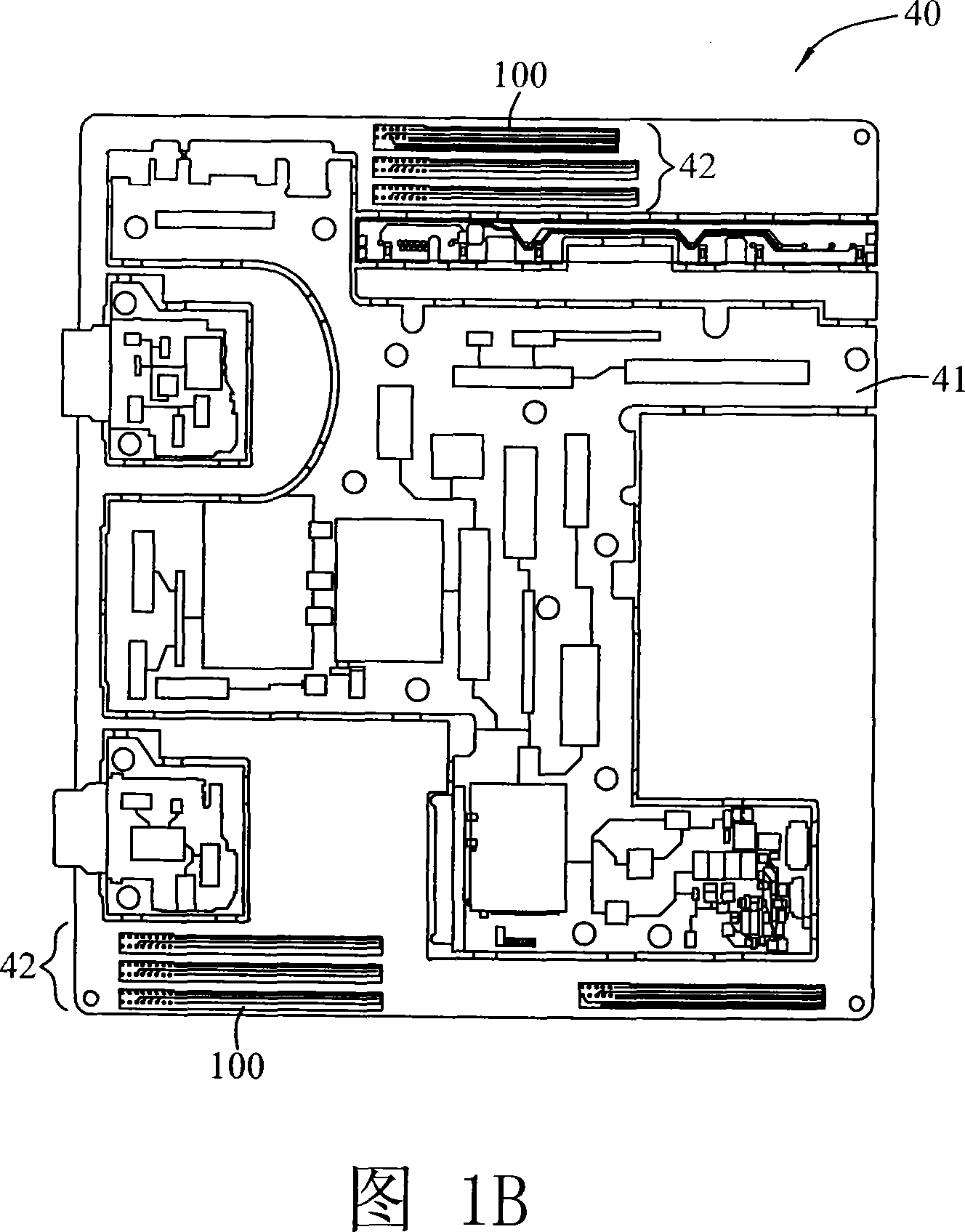

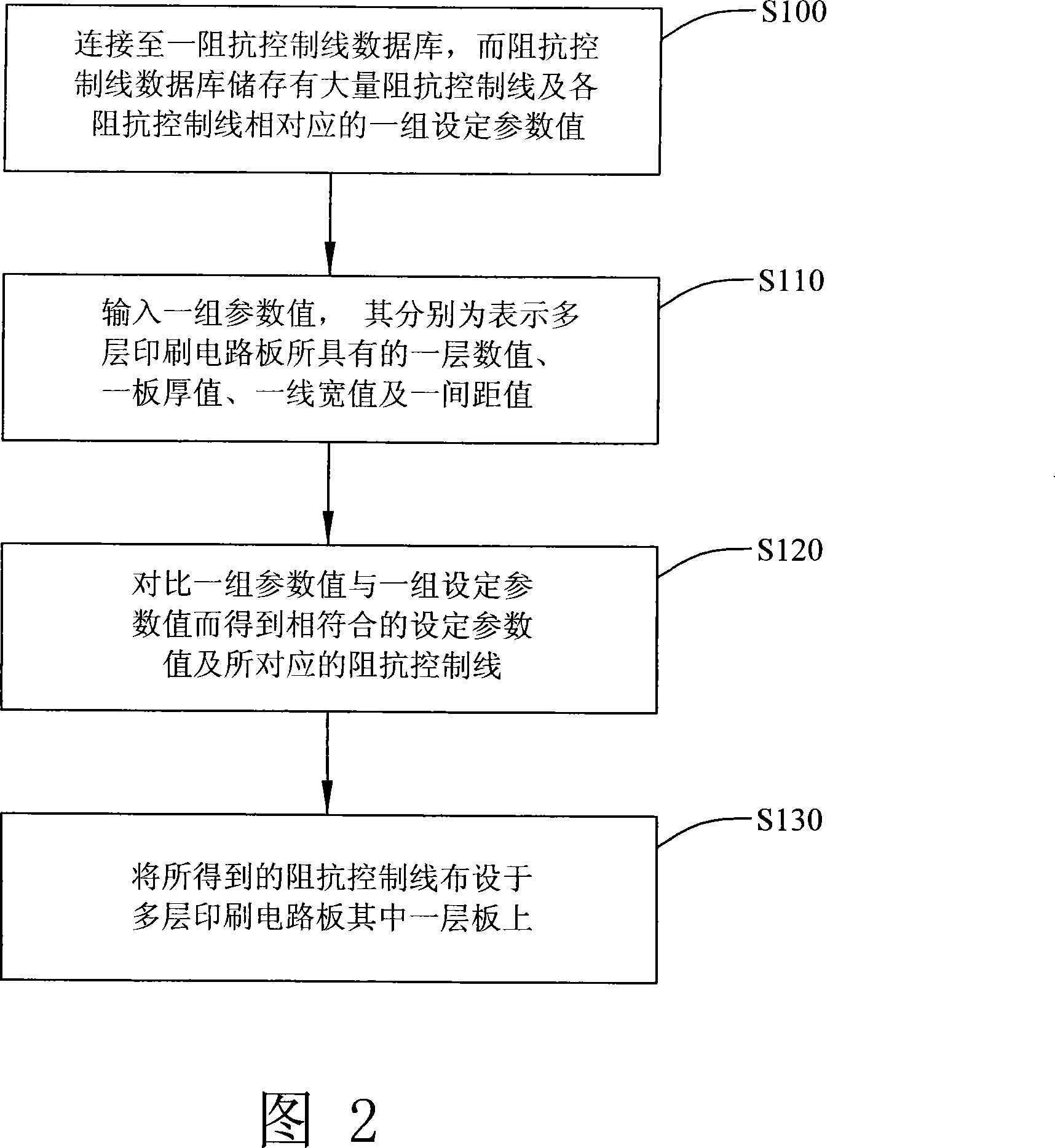

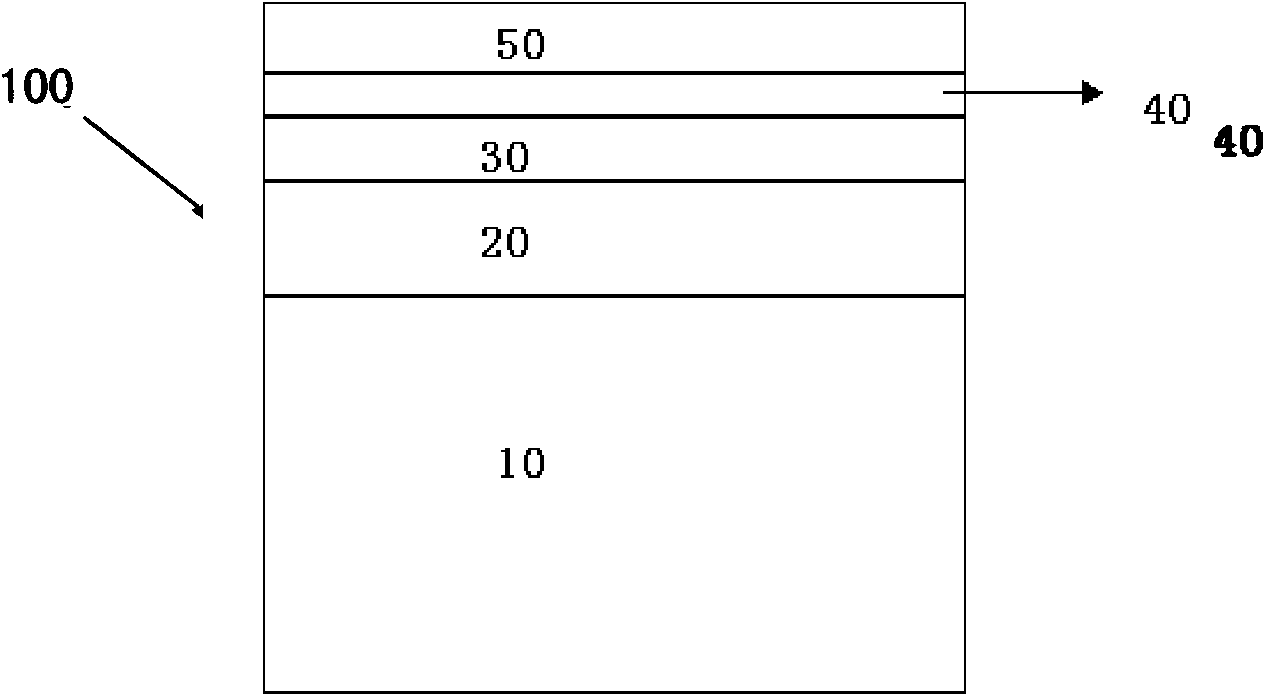

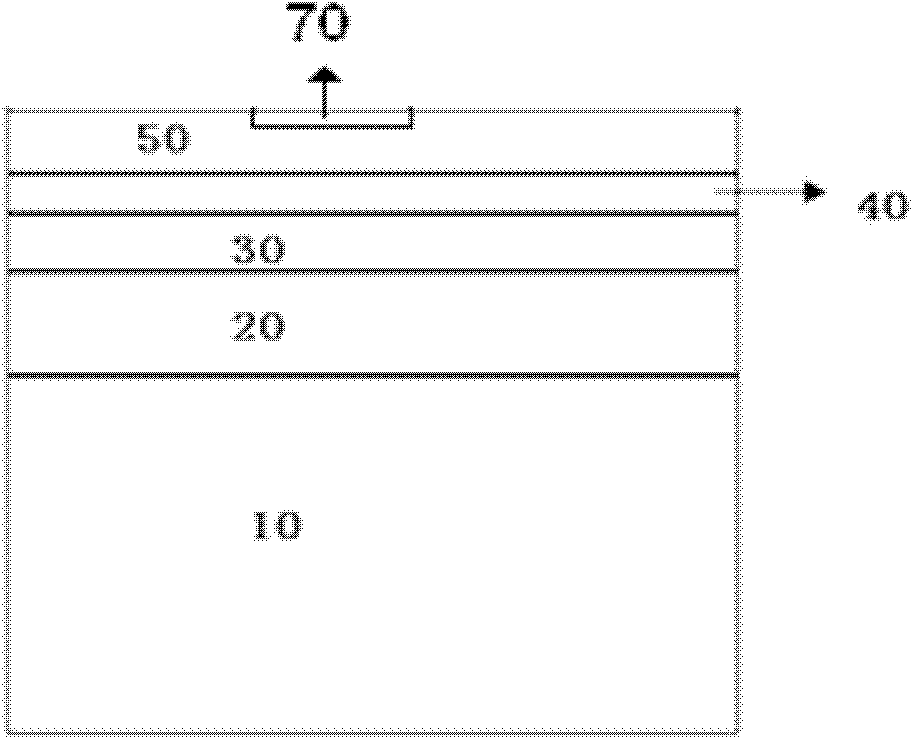

Method for establishing electric impedance control line

InactiveCN101211384AReduce human errorShorten the timeSpecial data processing applicationsEngineeringImpedance control

The invention discloses a method for establishing impendence control wires; the method is used in a multi-layered PCB. First of all, connect with a database for impendence control wires; the impendence control wire database stores a plurality of impendence control wires and a group of defined parameter values corresponding to all impendence control wires. Then, input a group of the parameter values that respectively include a layer of values, a board thickness value, a wire width value as well as a space value. After that, perform comparison between the input group of the parameter values and the defined parameter values in the impendence control wire database, so as to gain a group of defined parameter values that are complied with and corresponding impendence control wires. Moreover, arrange the acquired impendence control wires into a layer of the multi-layered PCB.

Owner:INVENTEC CORP

Method for manufacturing current blocking layer of gallium nitride-based light-emitting diode (LED)

InactiveCN102214743AImprove luminous efficiencyReduce craft production costSemiconductor devicesSurface layerQuantum well

The invention relates to a method for manufacturing a current blocking layer of a gallium nitride-based light-emitting diode (LED). The method comprises the following steps of: 1, preparing a gallium nitride LED epitaxial sheet which consists of a substrate, N-type gallium nitride, a multi-quantum well, aluminum gallium nitride EBL (Electron Blocking Layer) and P-type gallium nitride; 2, isolating the gallium nitride LED epitaxial sheet into a plurality of repeating units, wherein each unit is an independent LED chip; 3, performing surface treatment on a selected region of the upper surface of each unit to form a current blocking layer on the central region of the surface layer of the P-type gallium nitride; and 4, manufacturing an electrode P which covers the entire current blocking layer and the P-type gallium nitride on the upper surface of each unit to finish manufacturing the current blocking layer of the gallium nitride-based LED.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

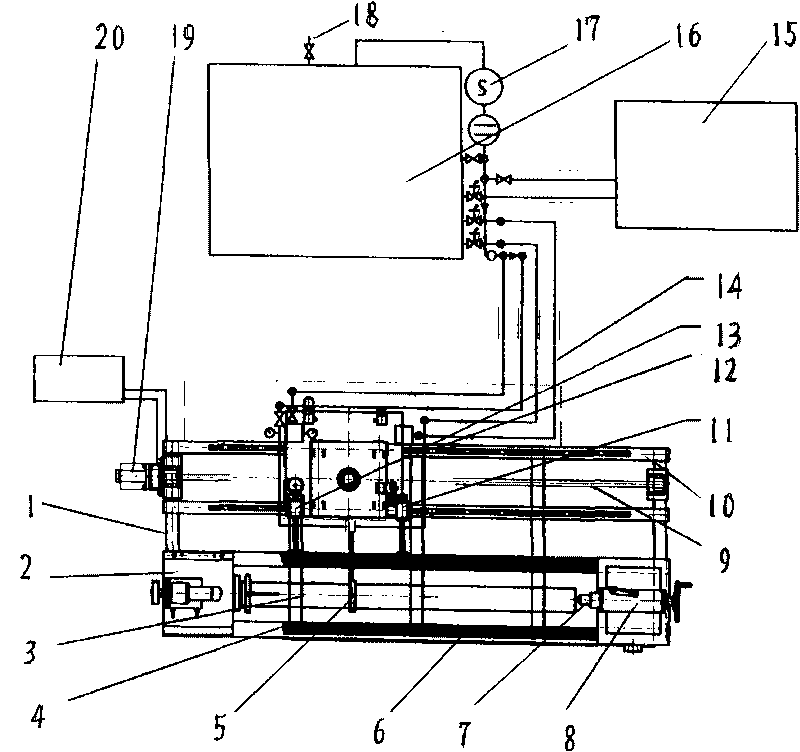

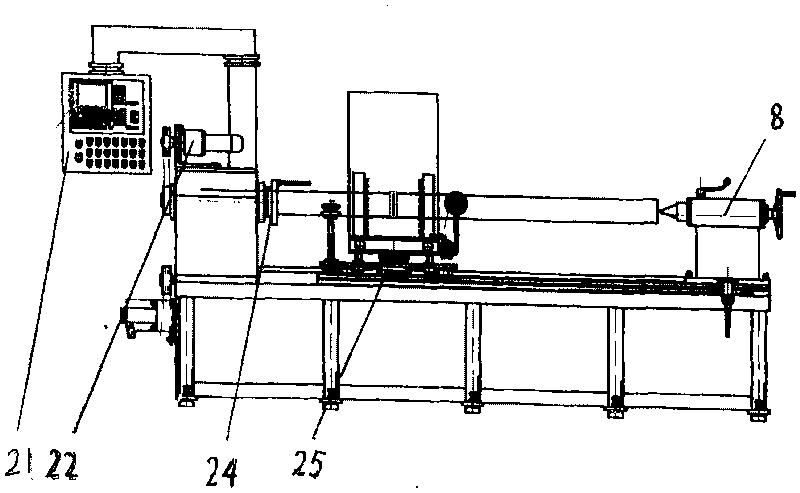

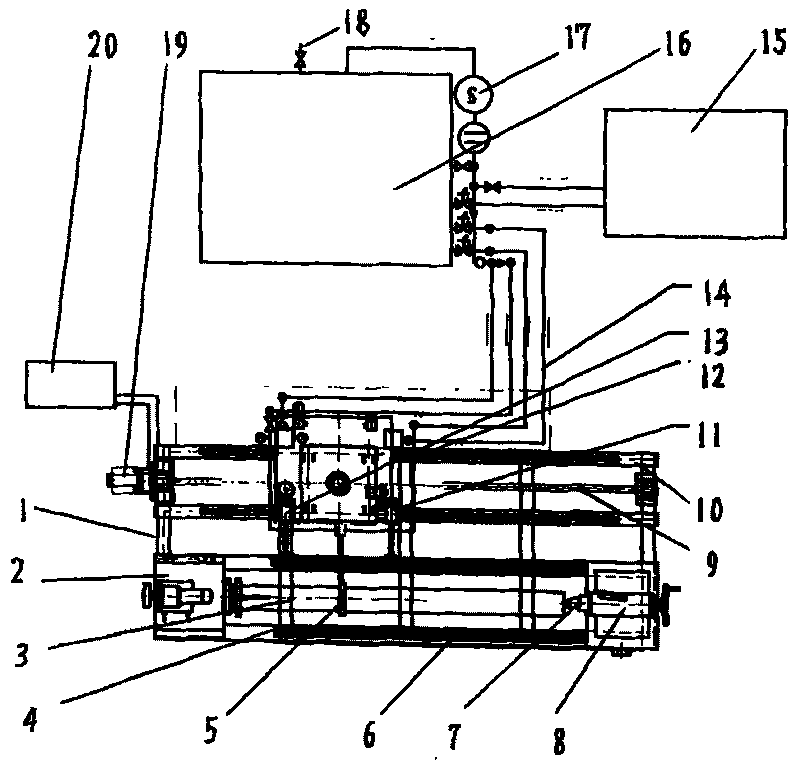

Induction remelting machine tool

InactiveCN101724840AFast and uniform heatingImprove the surface hardness valueMetallic material coating processesEngineeringHigh surface

The invention provides an induction remelting machine tool for induction remelting of an alloy (ceramics) powder coating and a metallic base material.The machine tool body is provided with a main spindle box and a tail bracket which are arranged in opposite direction, assist in clamping workpieces and drive the workpieces to rotate; the workpieces clamped by the main spindle box and the tail bracket are sleeved into an inductor which can heat the workpieces, the inductor is arranged on a carriage which can drag the inductor to do reciprocating motion.The machine tool of the invention solves the defects in the prior art that remelting temperature control is not accurate, the workpieces are not preheated and heated evenly, the remelted crystal grains are coarse, the remelting efficiency is low, the production quality is not stable and the like. The machine tool of the invention has the advantages of quick and even remelting temperature rise, small deformation of workpieces, high quality remelting, fine crystal grains in an induction remelting coating, high surface hardness value, and superiority of the corrosion resistance and abrasive resistance of the coating to the corrosion resistance and abrasive resistance of oxyacetylene flame remelting coating with more coarse crystal grains, low cost in technology investment and production and the like.

Owner:王洪刚

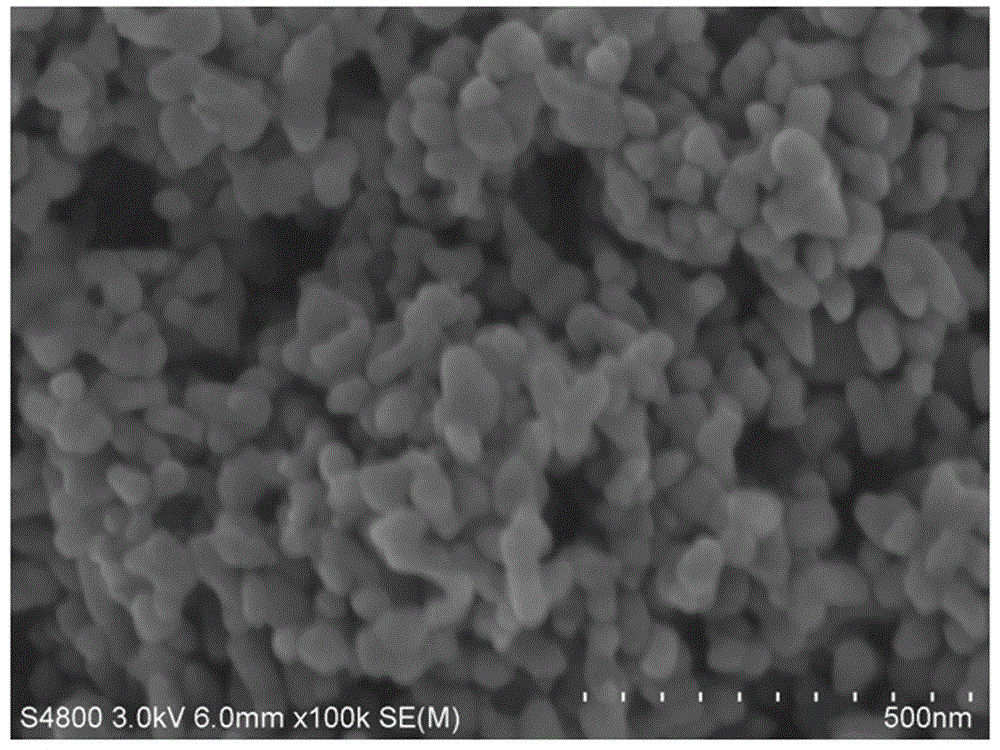

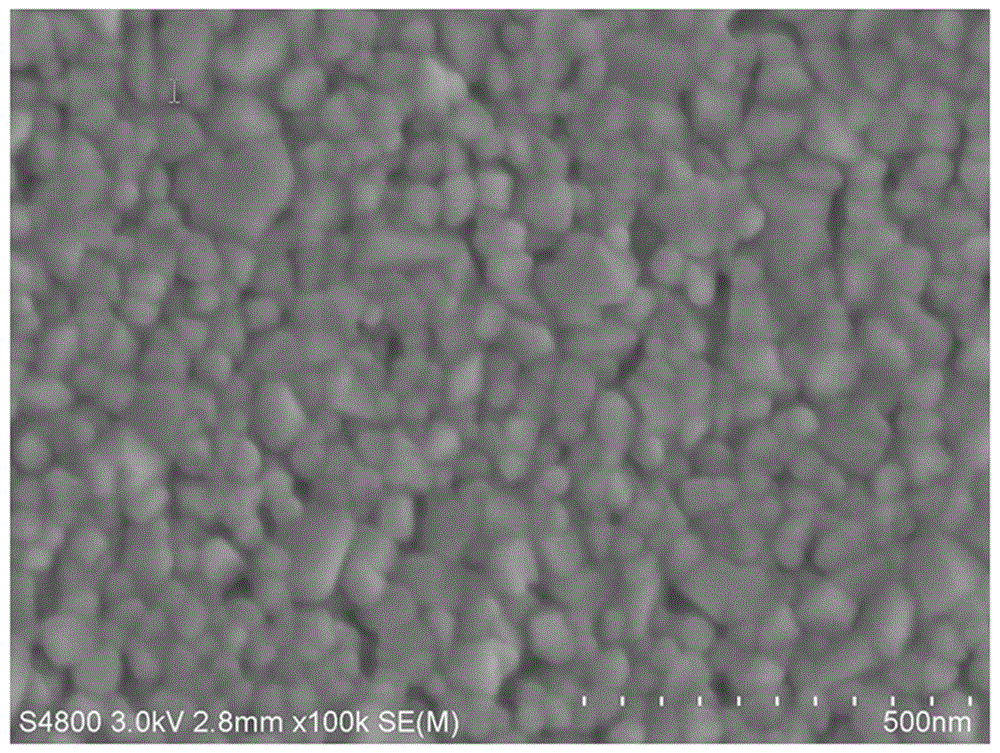

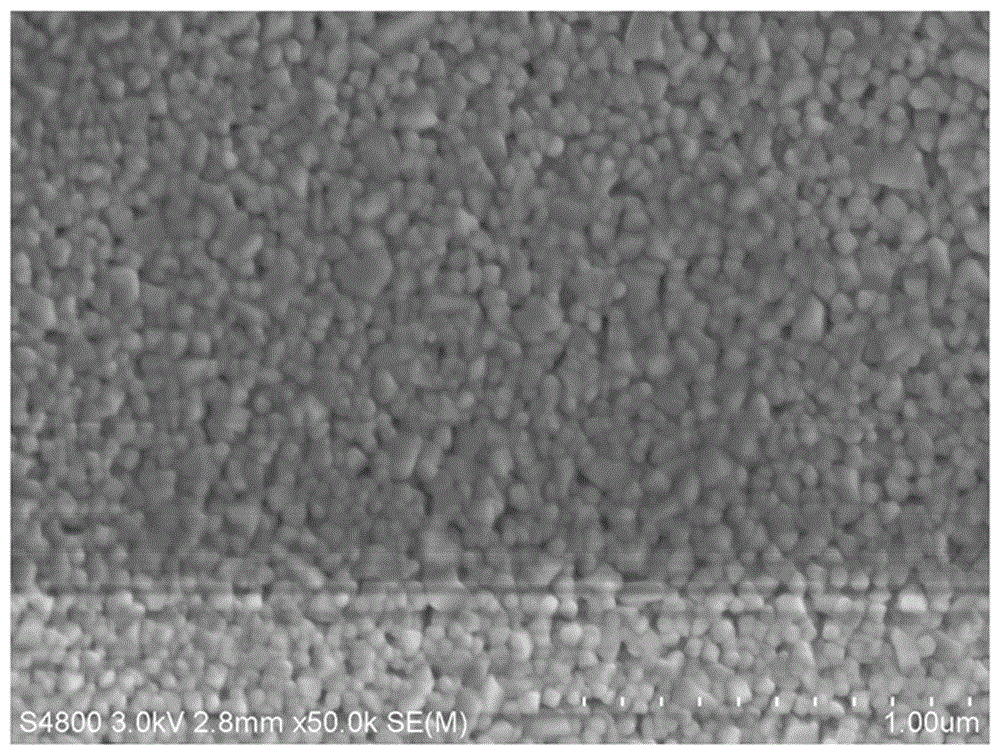

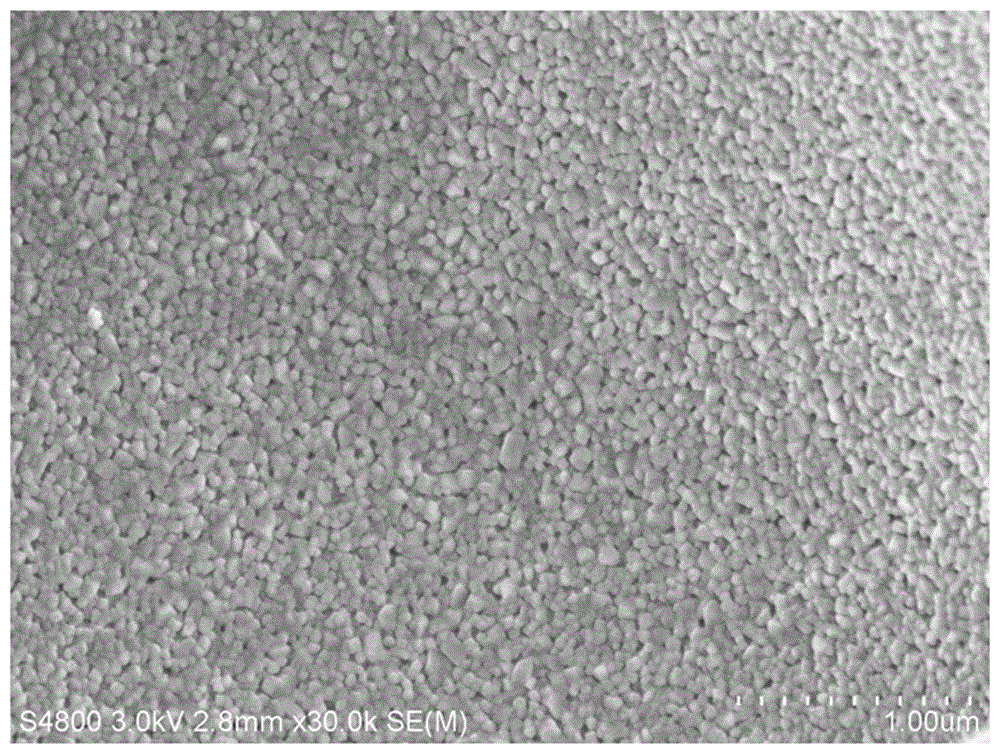

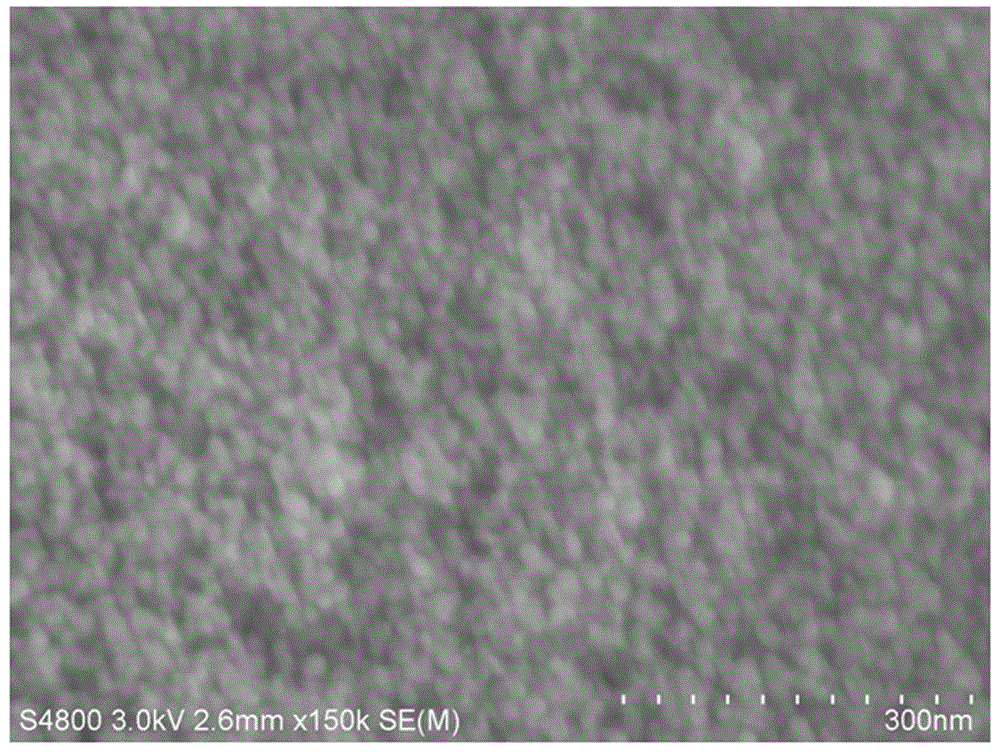

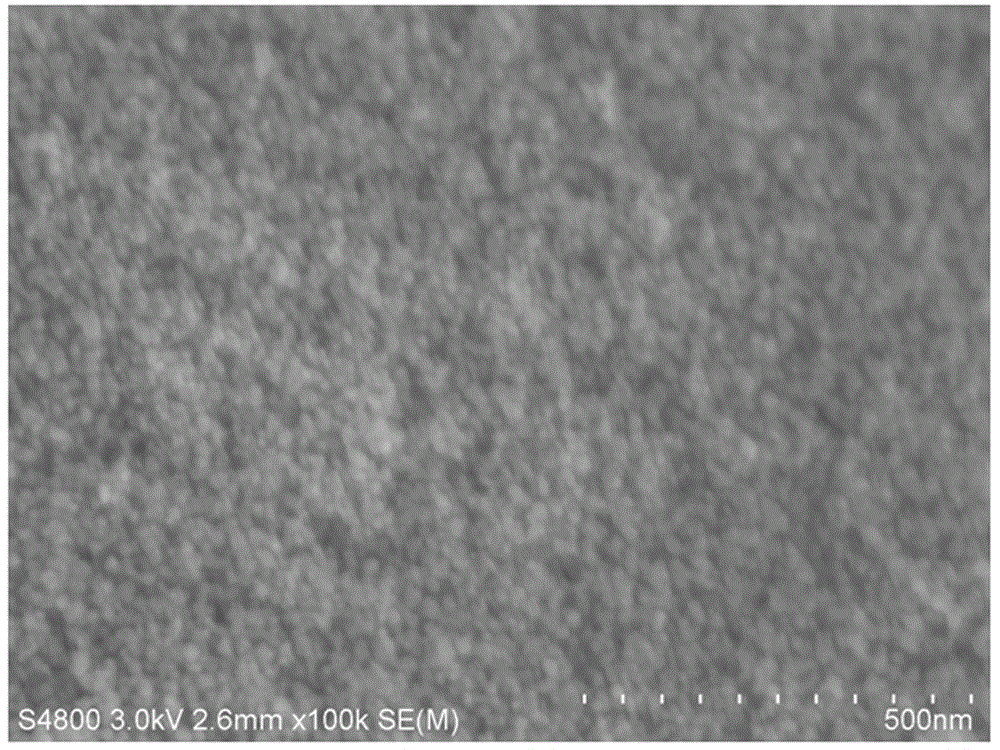

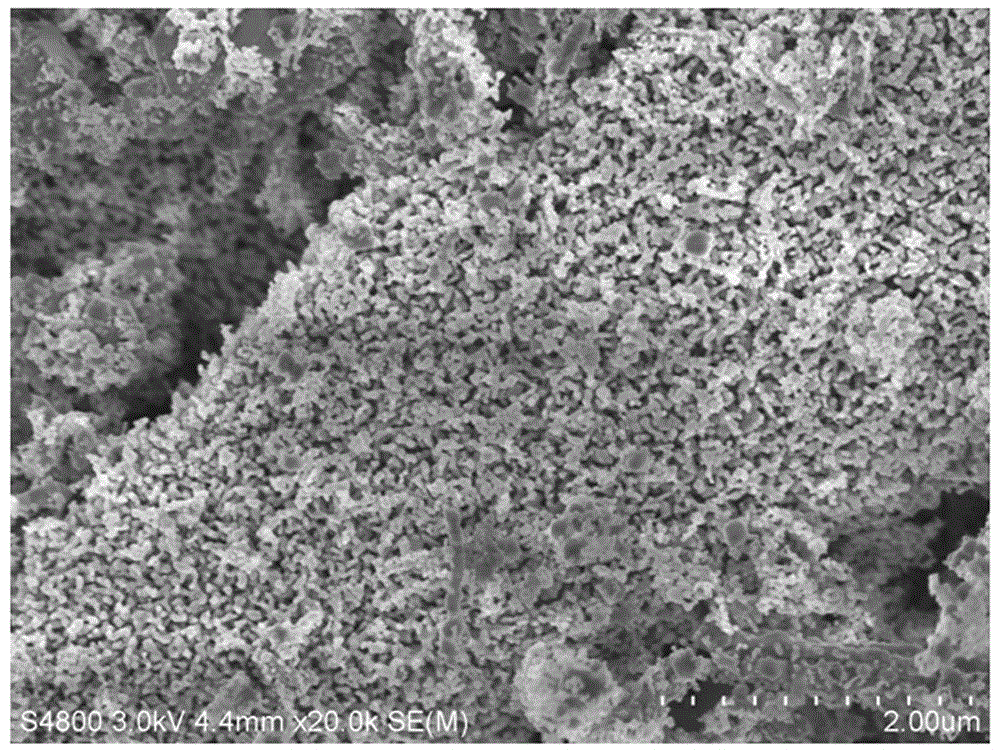

Preparing method for copper oxide spherical hierarchical structure material

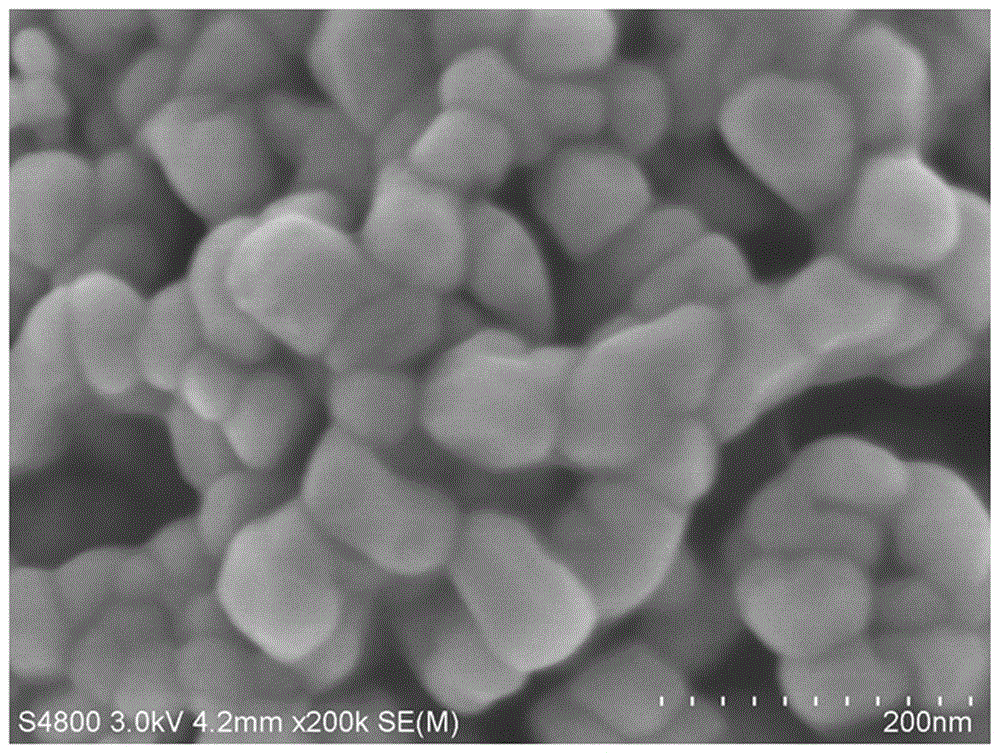

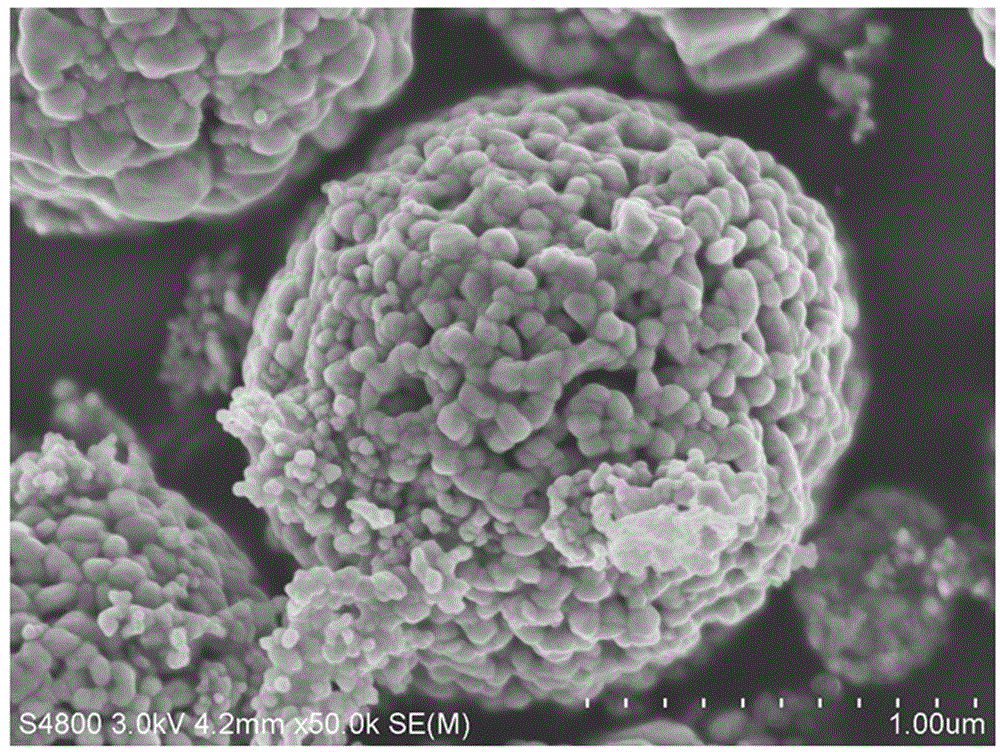

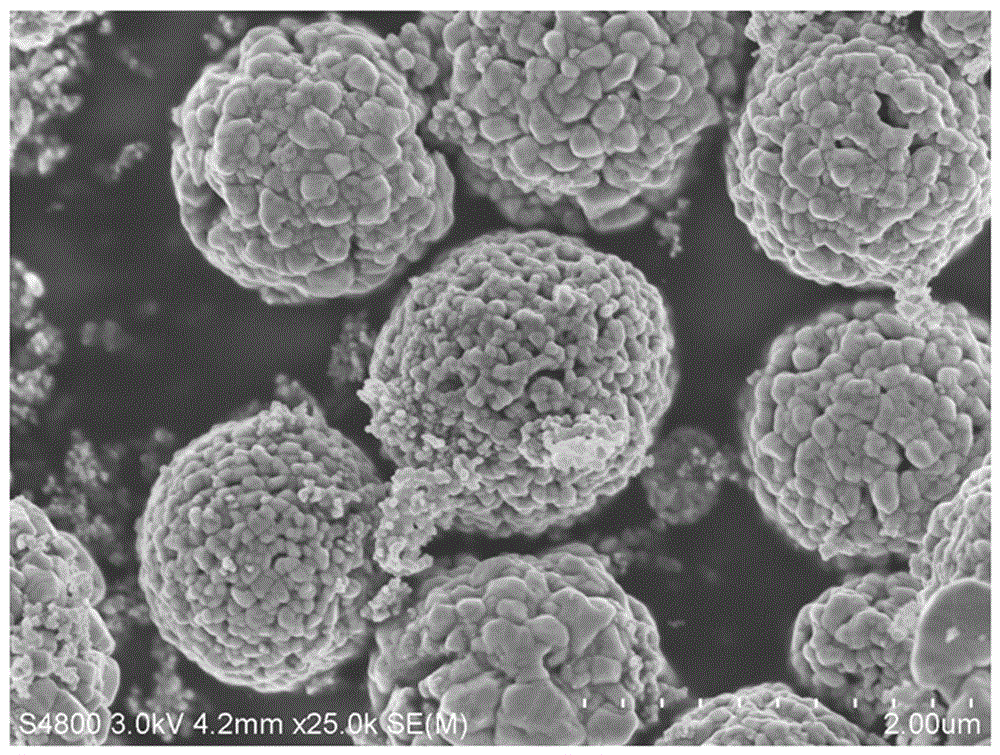

InactiveCN106115763ALarge specific surface areaMany gapsMaterial nanotechnologyCopper oxides/halidesCopper saltAqueous solution

The invention belongs to the technical field of functional material preparation and relates to a preparing method for a copper oxide spherical hierarchical structure material. A mineralizing agent is added into an oxalic acid aqueous solution, then a soluble copper salt aqueous solution is dropwise added, and a reaction is carried out under the constant temperature and stirring conditions until precursor precipitate is generated; filtering, washing, drying and roasting are carried out, and the copper oxide spherical hierarchical structure material is obtained. The copper oxide spherical hierarchical structure material is formed through assembling of a large quantity of copper oxide nanoparticles. The dimension of spheres ranges from 1 mm to 2 mm, the dimension of the copper oxide nanoparticles ranges from 40 nm to 60 nm, and the dimension of pore canals of the copper oxide nanoparticles ranges from 10 nm to 30 nm. The technology is low in preparing cost, operation is easy to control, high production efficiency is achieved, and industrial mass production can be achieved. The copper oxide spherical hierarchical structure material prepared with the method has high catalytic activity when serving as a visible light catalytic material and has wide application prospects in the fields such as dye wastewater and indoor harmful gas degradation and photocatalystic disinfection.

Owner:BOHAI UNIV

Method for preparing titanium dioxide/stannic oxide compounded oxide superfine nano particles

ActiveCN106076311ALow cost of preparationEasy to controlMaterial nanotechnologyWater/sewage treatment by irradiationMuffle furnaceOxide

Owner:抚顺市清原助剂厂有限公司

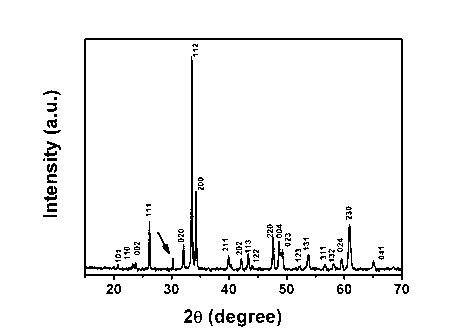

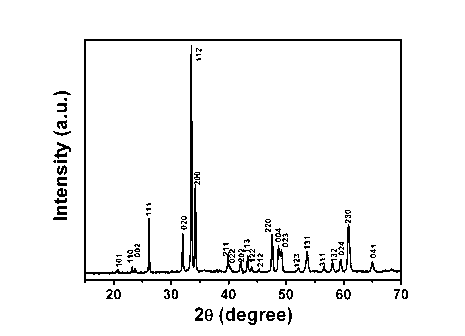

Preparation process of YMnO3 dielectric ceramic and YMnO3 dielectric ceramic capacitor

InactiveCN102910913AEasy to implementLower sintering temperatureFixed capacitor dielectricCeramicSol-gel

The invention relates to a preparation process and application of ceramic, in particular to a preparation process of YMnO3 dielectric ceramic and a YMnO3 dielectric ceramic capacitor. In order to solve the problems of complicated procedures, poor provenance of finished products and the like in an existing preparation process of YMnO3 dielectric ceramic, the YMnO3 dielectric ceramic is prepared by the aid of a sol-gel method and by means of mixing and dissolving ingredients, adding corresponding catalysts or complexing agents, drying, pyrolyzing, grinding, presintering and firing. The obtained YMnO3 dielectric ceramic can be prepared to the YMnO3 dielectric ceramic capacitor and other ceramic products.

Owner:HENAN UNIV OF SCI & TECH

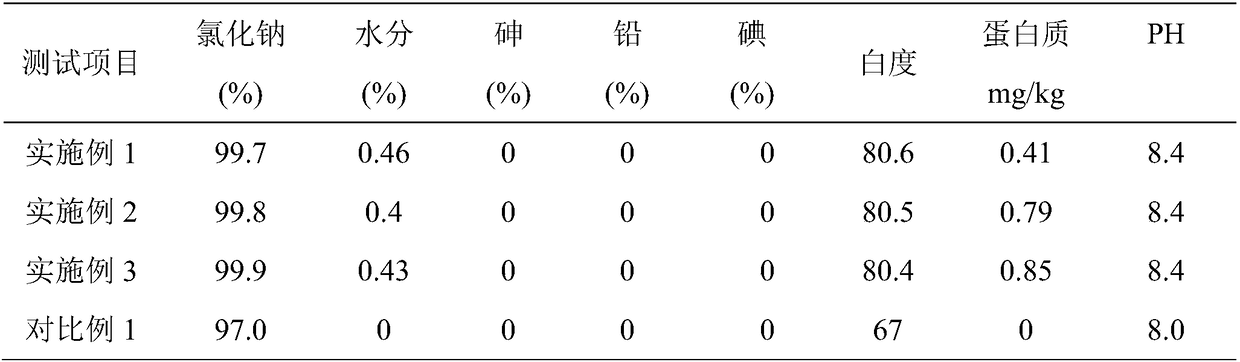

Preparation method of active bamboo salt

InactiveCN108354162AReduce craft production costReduce respiratory diseaseNatural extract food ingredientsFood ingredient functionsChemistryToxicity

The invention provides a preparation method of active bamboo salt. The method comprises the following steps of (1) preparing powdery refined rock salt; (2) preparing a bamboo extract; (3) mixing the powdery refined rock salt with the bamboo extract and pure water, and sequentially performing stirring, extruding and granulation so as to obtain granular bamboo salt; (4) performing calcining treatment on the granular bamboo salt, and performing screening to obtain the required bamboo salt, wherein the step (1) and the step (2) can be performed in any order. The technical scheme provided by the embodiment of the invention is simple in preparation method, environment-friendly, high in technology stability, high in speed, and easy to promote. The content of sodium chloride in the prepared bamboosalt is 99% or above, and the prepared bamboo salt is free from heavy metals, and has activity functions, the bore diameters are extensive in distribution, and the bamboo salt has high effects of diminishing inflammation, sterilizing, infiltrating, removing bad tissues, promoting tissue regeneration, removing toxicity, expelling toxins, relieving a cough and the like, and can be widely applied tothe fields of medical health and health-care products.

Owner:南京宽诚科技有限公司

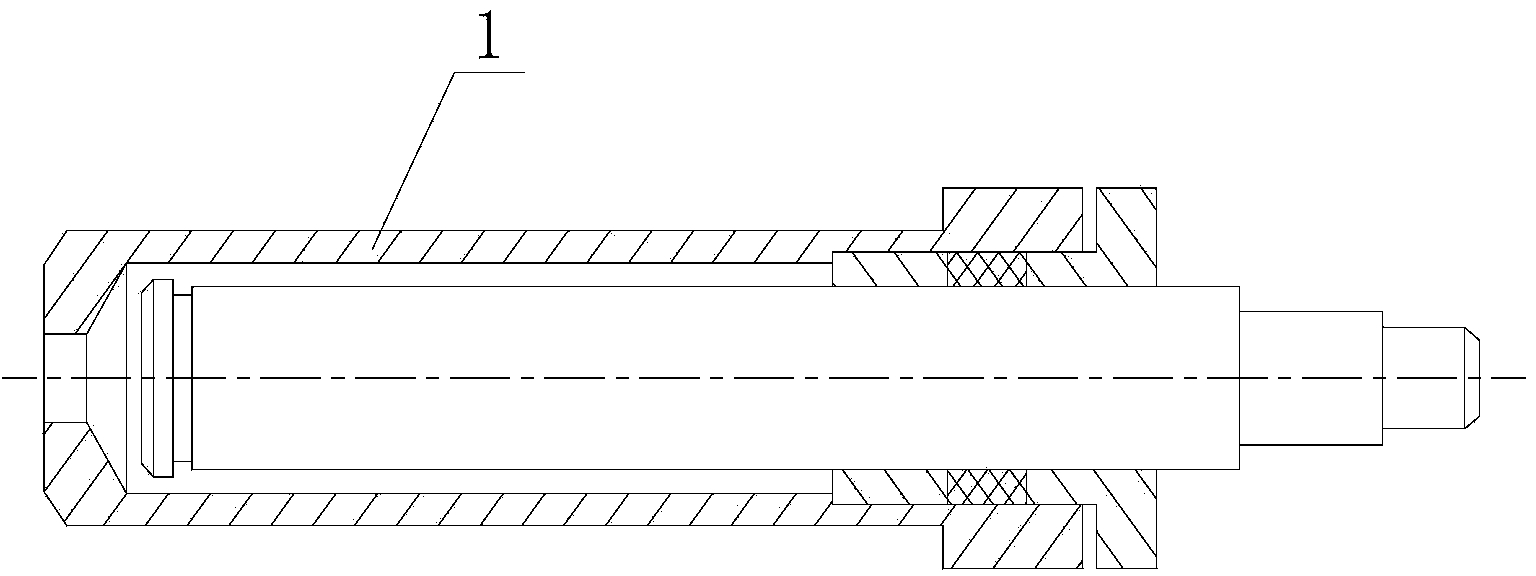

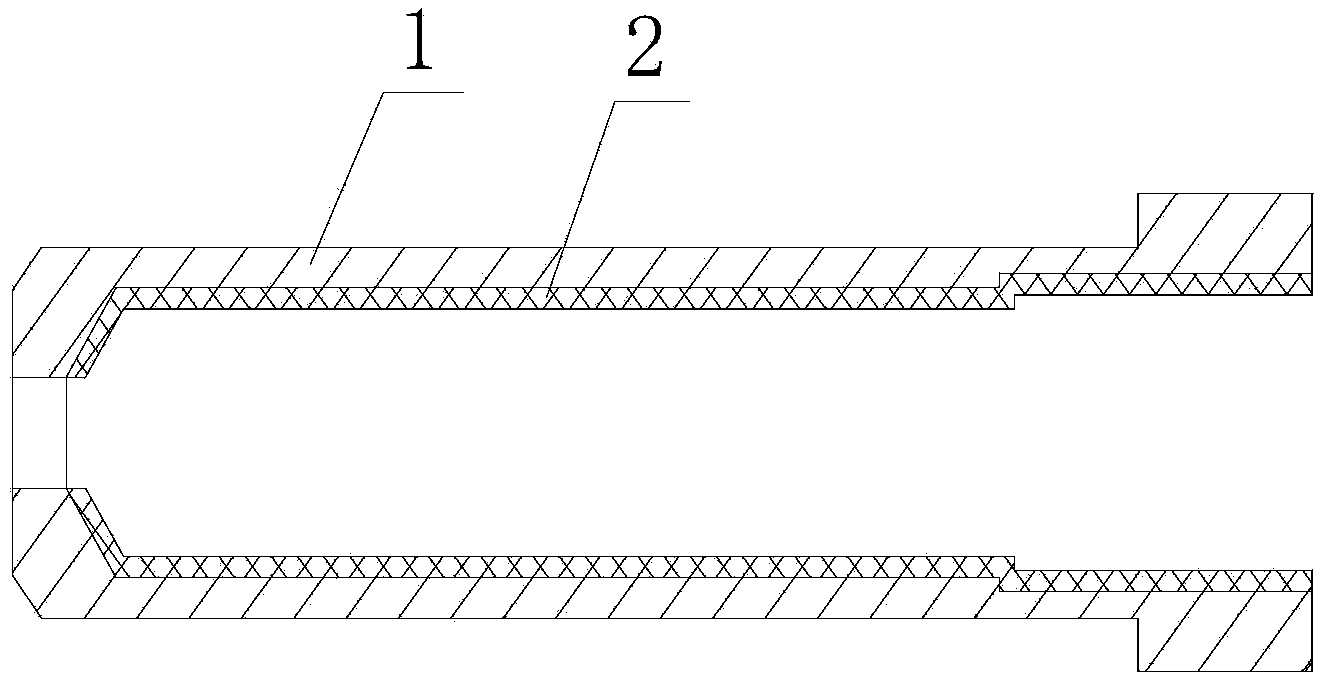

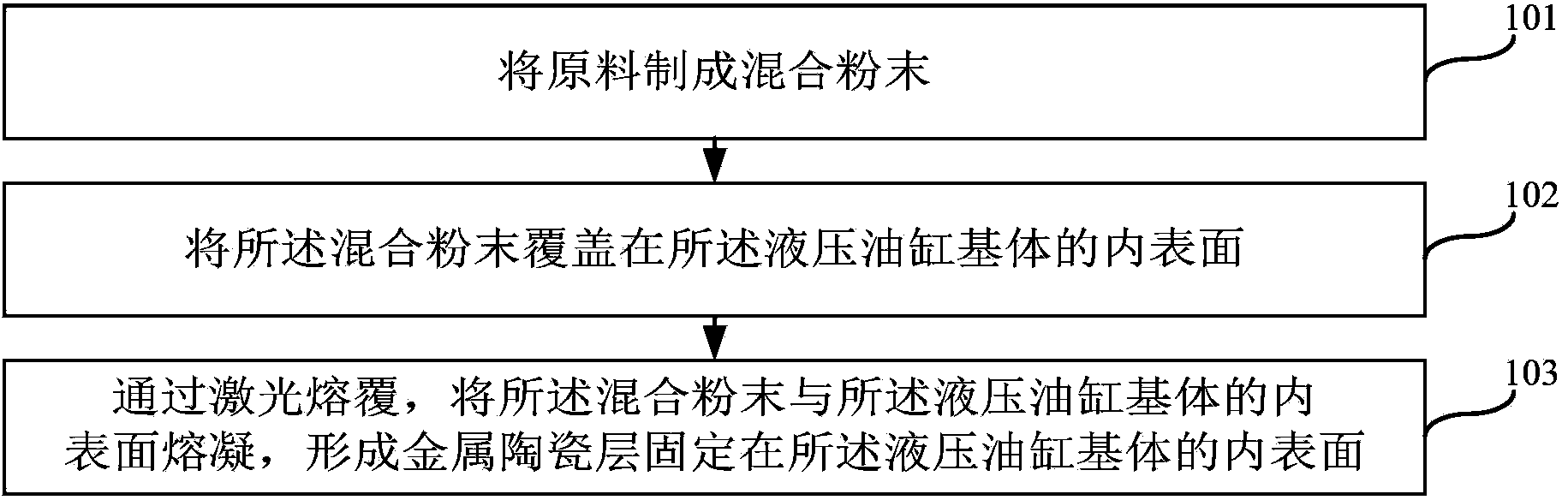

Anti-corrosion wear-proof hydraulic cylinder and manufacturing method thereof

InactiveCN103982654AImprove wear resistanceFast formingCylindersMetallic material coating processesHydraulic cylinderWear resistance

The invention belongs to the field of hydraulic cylinders and particularly relates to an anti-corrosion wear-proof hydraulic cylinder and a manufacturing method of the anti-corrosion wear-proof hydraulic cylinder. The anti-corrosion wear-proof hydraulic cylinder comprises a hydraulic cylinder base body. The inner surface of the hydraulic cylinder base body is covered with a metal ceramic layer. The metal ceramic layer comprises, by mass, 10%-30% of chromium, 2%-12% of silicon, 30%-40% of iron, 3%-13% of carbon and 35%-45% of nickel. By the adoption of the anti-corrosion wear-proof hydraulic cylinder and the manufacturing method of the manufacturing method of the anti-corrosion wear-proof hydraulic cylinder, the manufactured hydraulic cylinder is good in wear resistance, and the machining property and the stability are good; compared with an existing hydraulic cylinder, the service life of the manufactured hydraulic cylinder is prolonged by over 1.5 times, the utilization ratio of the hydraulic cylinder is increased, and the use cost is reduced.

Owner:四川中久力合石油科技有限公司

Preparation method of cobaltosic oxide/stannic oxide composite nanomaterial

InactiveCN105932271AReduce craft production costControllableMaterial nanotechnologyHybrid capacitor electrodesMuffle furnaceCapacitance

The invention belongs to the technical field of functional material preparation, and relates to a preparation method of a cobaltosic oxide / stannic oxide composite nanomaterial. The method comprises the following steps: dropwise adding a methanol solution of a cobalt chloride and stannous chloride mixture to an oxalic acid aqueous solution and reacting at a constant temperature under a stirring condition until a precursor sediment is generated; filtering, washing and drying the precursor sediment, and then carrying out thermal treatment in a muffle furnace to obtain the cobaltosic oxide / stannic oxide composite nanomaterial. The technology is simple, convenient and easy to do; the purity is high; the purity content is low; the preparation cost of the product is low; the performance is excellent; and industrial mass production can be achieved. The cobaltosic oxide / stannic oxide composite nanomaterial prepared by the method has relatively good conductivity, has relatively high specific capacitance and good cycle performance as an electrode material.

Owner:BOHAI UNIV

Preparing process of double-perovskite Y2MNCoO6 dielectric ceramic

The invention provides a preparing process of double-perovskite Y2MnCoO6 dielectric ceramic, relates to a ceramic preparing process and aims at solving the defects existing in the traditional preparing process of Y2MnCoO6 dielectric ceramic that the process is heavy and complicated, the finished product is poor in condition and the like. The invention provides a sol-gel method, comprising the steps of: mixing and dissolving ingredients, adding corresponding catalyst or complexing agent, drying, pyrolyzing, grinding, prefiring, and firing to prepare Y2MnCoO6 dielectric ceramic. The obtained Y2MnCoO6 dielectric ceramic can be widely applied to the field of ceramic things.

Owner:HENAN UNIV OF SCI & TECH

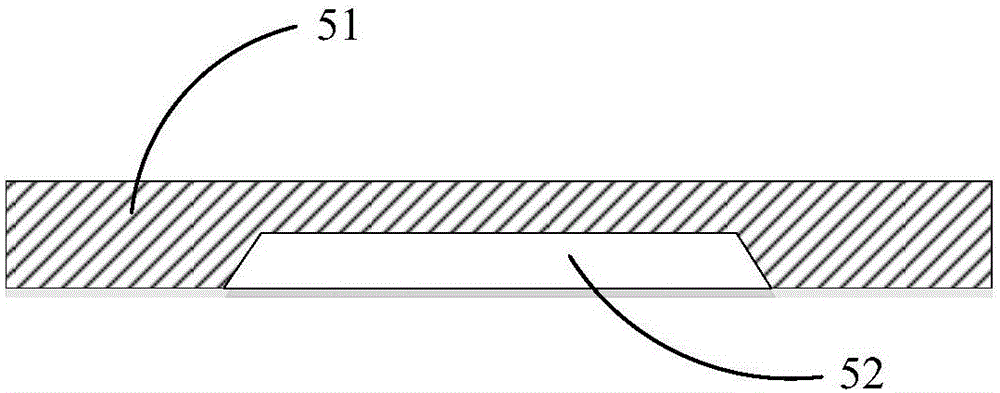

Board-level fan-out chip packaging device and preparation method thereof

ActiveCN105140189AImprove cooling effectImprove performanceSemiconductor/solid-state device detailsSolid-state devicesEngineeringEmbedded system

The embodiment of the invention relates to a board-level fan-out chip packaging device and a preparation method thereof. A recess is formed in one side of a bearing board used for bearing a chip, the size of the recess is matched with the size of the back side of the chip, and the chip is mounted in the recess. When the chip is mounted to the bearing board, the recess in the bearing board exactly accommodates the back side of the chip, so that the chip to be packaged is easy and convenient to put in place. According to the invention, the dependence of fan-out packaging on the format of a chip mounter and chip mounting precision is eliminated, so that the development of the large-format fan-out chip packaging technology is facilitated.

Owner:广东佛智芯微电子技术研究有限公司

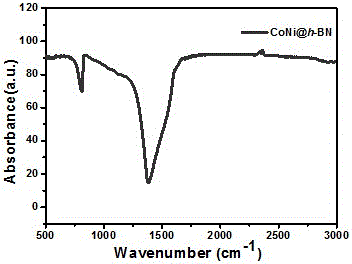

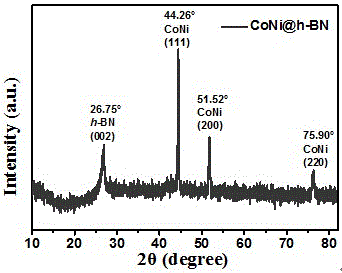

Preparing method for hexagonal boron nitride wrapping cobalt-nickel alloy

InactiveCN105921761AReduce craft production costControllableTransportation and packagingMetal-working apparatusHexagonal boron nitrideCobalt nickel alloy

The invention belongs to the technical field of preparing of nanometer materials, and particularly relates to a preparing method for a hexagonal boron nitride wrapping cobalt-nickel alloy material. A precursor of hexagonal boron nitride and a precursor of a cobalt-nickel alloy compound are mixed to be ground according to a certain molar ratio, and under the nitrogen condition, hexagonal boron nitride wrapping nanometer cobalt nickel particles are prepared in a high-temperature roasting manner; and according to the method, raw materials are cheap and easy to obtain, the cost is low, the preparing method is easy to operate, and high pressure and strong oxidants involved in preparation of methods like an arc discharge method are avoided. The production yield is high, defects are few, and the hexagonal boron nitride wrapping nanometer cobalt-nickel alloy nano particles have the higher heat conduction performance, high-temperature oxidation resistance performance, good soft magnetic performance and insulation performance.

Owner:JIANGSU UNIV

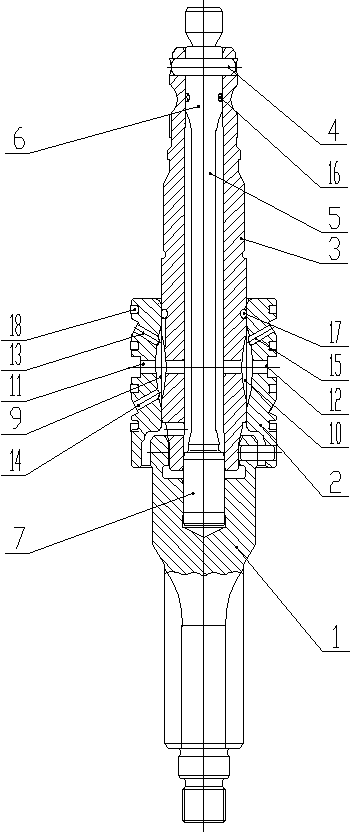

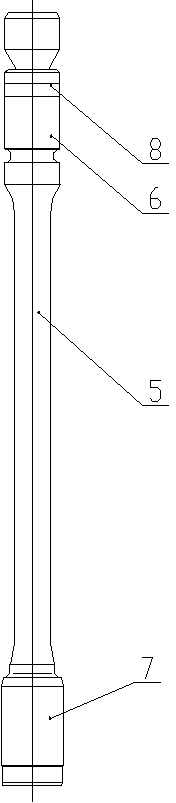

Pinion-and-rack type power steering gear valve element assembly

The invention relates to a pinion-and-rack type power steering gear valve element assembly and belongs to the technical field of automobile steering gears. The steering gear valve element assembly is composed of a pinion shaft, a valve sleeve, an input shaft and a torsion bar. The input shaft is installed on the pinion shaft through the valve sleeve. The torsion bar is installed in an inner hole of the input shaft through a cylindrical pin. A blind groove A and a blind groove B are correspondingly formed between the valve sleeve and the torsion bar. An oil inlet A and an oil outlet B are formed in the valve sleeve. The oil inlet A and the oil outlet B are communicated with the blind groove A and the blind groove B respectively. Compared with an existing power steering gear valve element assembly, needle bearings used for supporting the input shaft and the torsion bar are omitted, so that the product structure is optimized, the quality of the process that the torsion bar is pressed through the pinion shaft and the bouncing quality after a pin is punched into the valve element assembly are improved, the production and manufacturing cost is reduced to a certain degree, the output is improved, the quality control in the process is stable, and the requirements for automobile loading and quality are met.

Owner:荆州恒隆汽车零部件制造有限公司

Capacitance-free DRAM (Dynamic Random Access Memory) unit structure and manufacturing method

PendingCN114864583AReduce areaReduce craft production costTransistorSemiconductor/solid-state device manufacturingCapacitanceGate dielectric

The invention relates to a capacitance-free DRAM (Dynamic Random Access Memory) unit structure and a manufacturing method. The capacitance-free DRAM unit structure comprises a semiconductor substrate, a first isolation layer, a lower source-drain layer, a lower active region, a lower gate dielectric layer, a lower gate electrode layer, a second isolation layer, an upper source-drain layer, an upper active region layer, an upper gate dielectric layer and an upper gate electrode layer which are sequentially stacked from bottom to top, the lower source drain layer comprises a lower source electrode and a lower drain electrode which are separated by a first groove, and the bottom of the first groove is in contact with the first isolation layer; the upper source drain layer comprises an upper source electrode and an upper drain electrode which are separated by a second groove, and the bottom of the second groove is in contact with the second isolation layer; the lower gate electrode layer and the upper source drain layer are electrically connected through a contact hole arranged in the second isolation layer. According to the DRAM unit structure, the upper transistor and the lower transistor are completely overlapped, the unit area is saved, the integration density is improved, multiplexing of a gate electrode photoetching plate can be achieved, and the manufacturing cost is reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Coating of bamboo and wood color painting and preparation method thereof

InactiveCN102702906AImprove antioxidant capacityNo peeling and loss of lightFireproof paintsAnti-corrosive paintsNon toxicityFire resistance

The invention relates to a coating of a bamboo and wood color painting and a preparation method thereof. The prepared coating has natural and true color and gives the elegant, harmonious and sedate aesthetic perception. The coating is suitable for indoor and outdoor decoration of the bamboo and wood color painting. The effects of vividness, lifelikeness and return to the nature can be obtained. The coating has the effects of fire resistance, waterproofness, acid and alkali resistance, pollution resistance, non-toxicity, odorlessness, strong adhesive strength, fadeless property and the like; the bamboo and wood color painting can be effectively prevented from being eroded by the outside harsh environment; and the service life of the bamboo and wood color painting is prolonged. The coating has excellent adhesive force and freeze-thaw resistance, and thus, even though the coating is used in the cold areas, the coating of the bamboo and wood color painting is also simple and convenient to spray, is easy to dry, is time-saving and is convenient to operate.

Owner:太仓市德兰树片画设备科技有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com