Board-level fan-out chip packaging device and preparation method thereof

A chip packaging, fan-out technology, used in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., can solve problems such as development and cost reduction, and achieve the effect of improving performance, improving heat dissipation, and eliminating dependencies

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

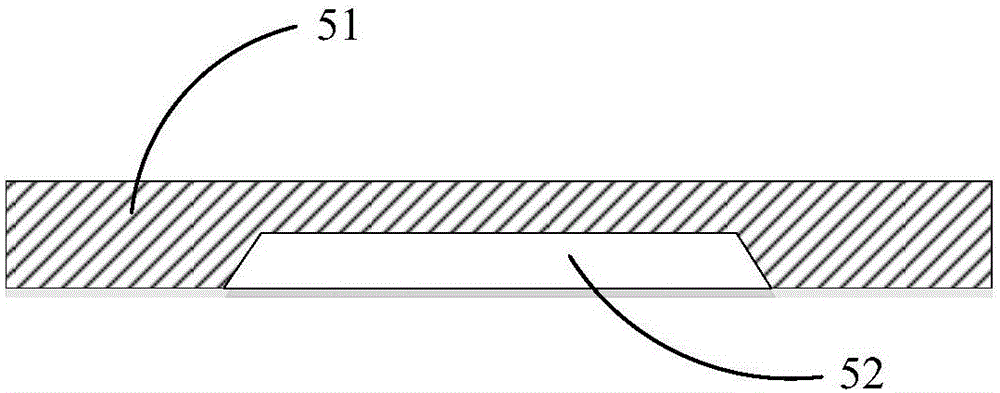

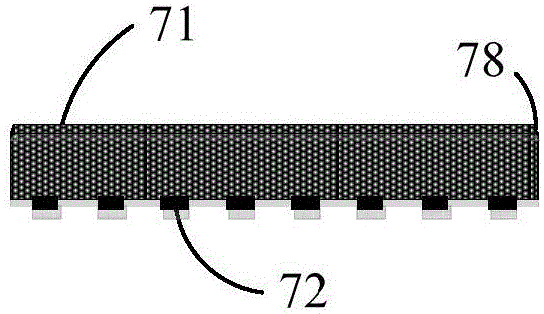

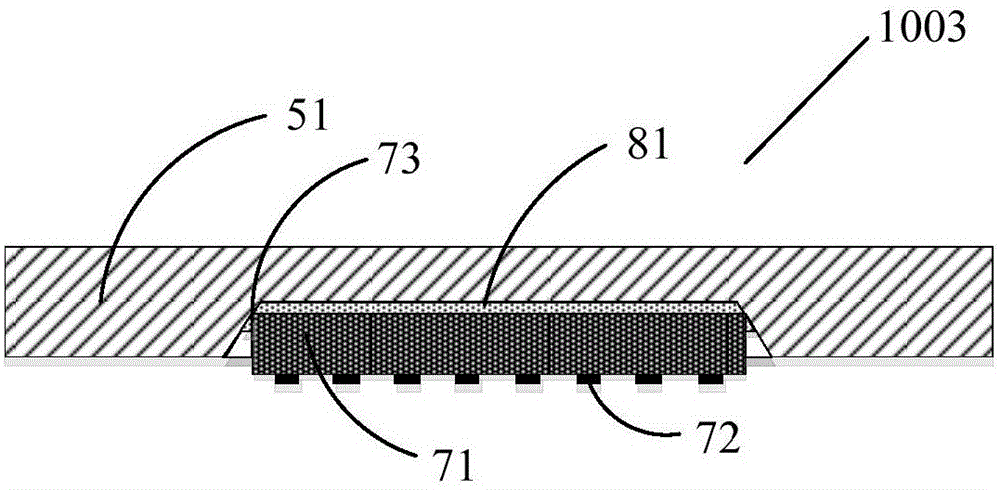

[0038] Therefore, the method for manufacturing a board-level fan-out chip package device provided according to an embodiment of the present invention includes: providing a carrier board on which a recess is provided, and the size of the recess is suitable for accommodating the chip; The back-mount and the recess of the carrier board; the dielectric layer is arranged on the recessed side of the carrier board, over the carrier board and the chip; and by pressing the carrier board and the dielectric layer, the material of the dielectric layer can be filled to the The recess of the carrier board and the gap between the chips.

[0039] The structure of the chip packaging device 10 according to the embodiment of the present invention has been embodied in the above description of the process flow, such as Figure 3-Figure 9 its cross-section shown. like Figure 4 As shown, the board-level fan-out chip package device 1004 includes: a carrier board on which recesses are provided, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More