A Fault Diagnosis Method for Analog Circuits with Single Measurement Node

A technology for simulating circuit faults and diagnostic methods, applied in the direction of simulating circuit testing, measuring electricity, measuring electrical variables, etc., can solve the problem that the circuit cannot directly apply the characteristic factor of blind source separation technology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will be described in detail below in conjunction with the accompanying drawings.

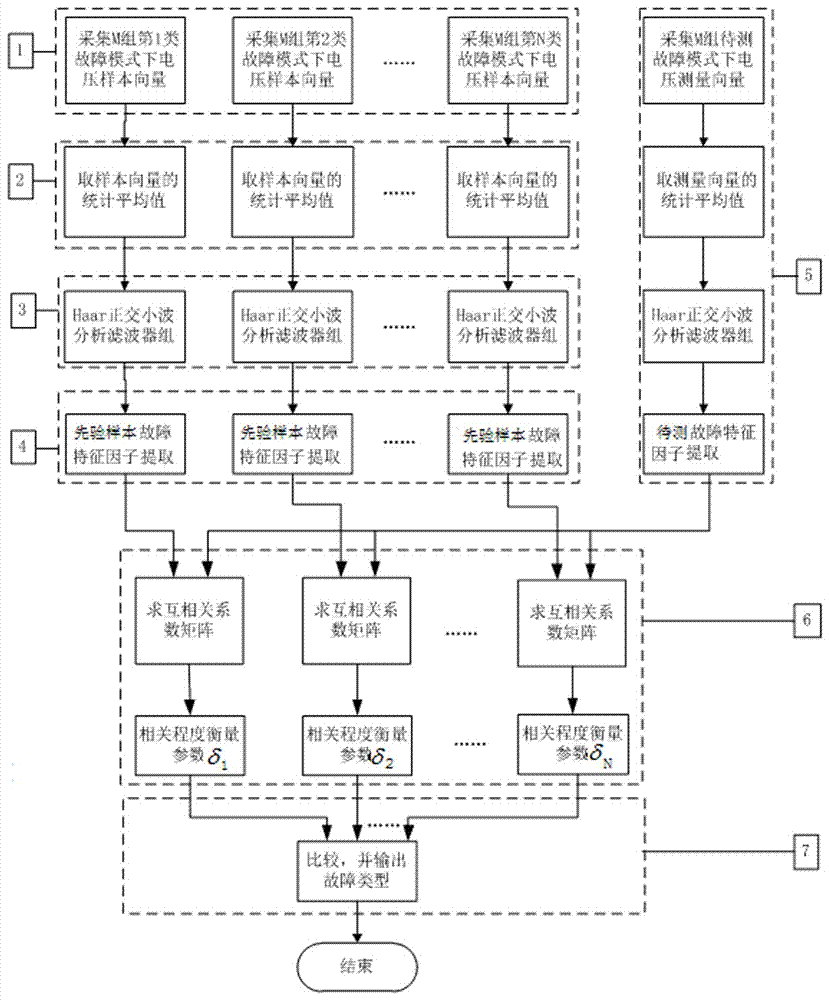

[0035] refer to figure 1 , a single measurement node analog circuit fault diagnosis method, comprising the following steps:

[0036] (1) Obtain the prior sample data vectors under each failure mode: use computer simulation software to obtain each failure mode F of the analog circuit to be tested i M groups of voltage sample vector V under ij , i=1,2,...,N, j=1,2,3,...,M, where N is the total number of circuit failure modes, i represents the circuit working in the i-type failure mode, and j is the collected jth group sample, V ij Represents the jth group of voltage sample vectors collected under the i-type failure mode of the circuit. exist figure 1 where is expressed as: collecting the voltage sample vectors under the first category failure mode of M groups; collecting the voltage sample vectors under the second category failure mode of M groups; ...;

[0037] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More