Mixed type three-dimensional on-chip network

A network-on-chip, hybrid technology, applied in the direction of instruments, electrical digital data processing, computers, etc., can solve the problems of increased communication power consumption, increased system transmission delay, etc., to improve internal bandwidth, shorten global interconnection length, increase The effect of interconnection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

[0031] The embodiment of the invention discloses a hybrid three-dimensional on-chip network to reduce the length of the connection and the diameter of the network, reduce system transmission delay, and reduce communication power consumption.

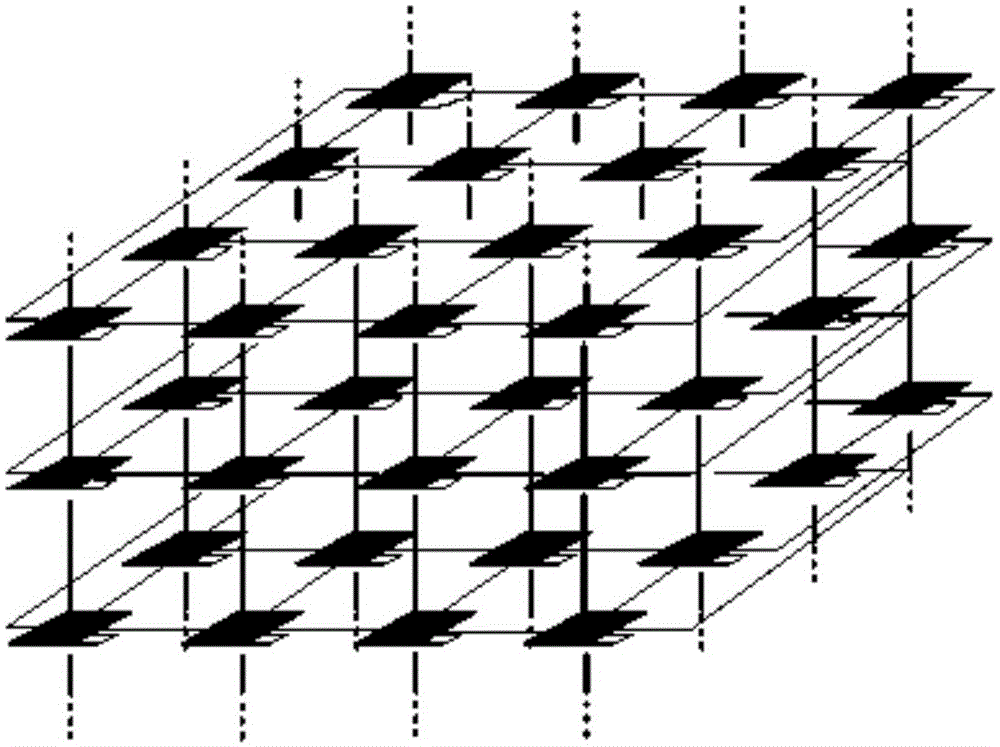

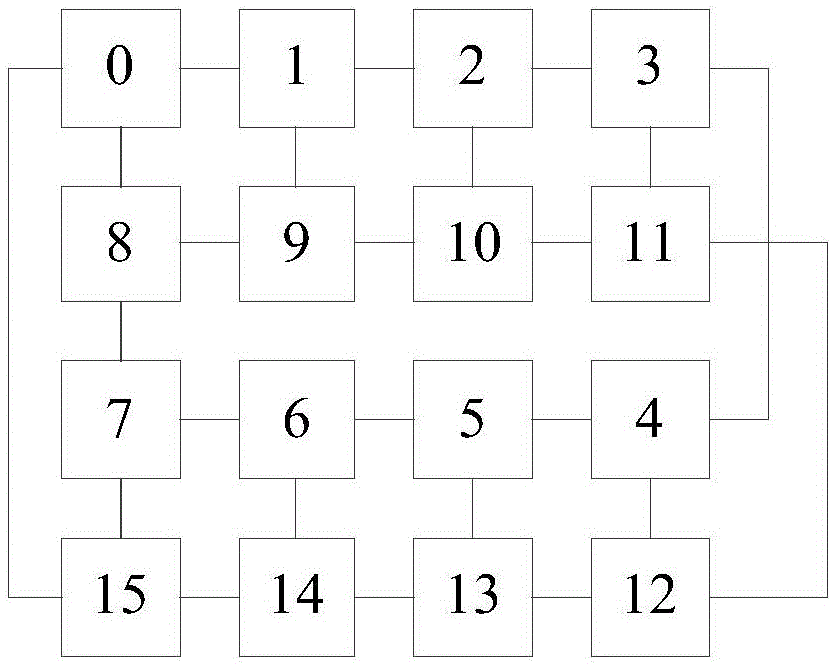

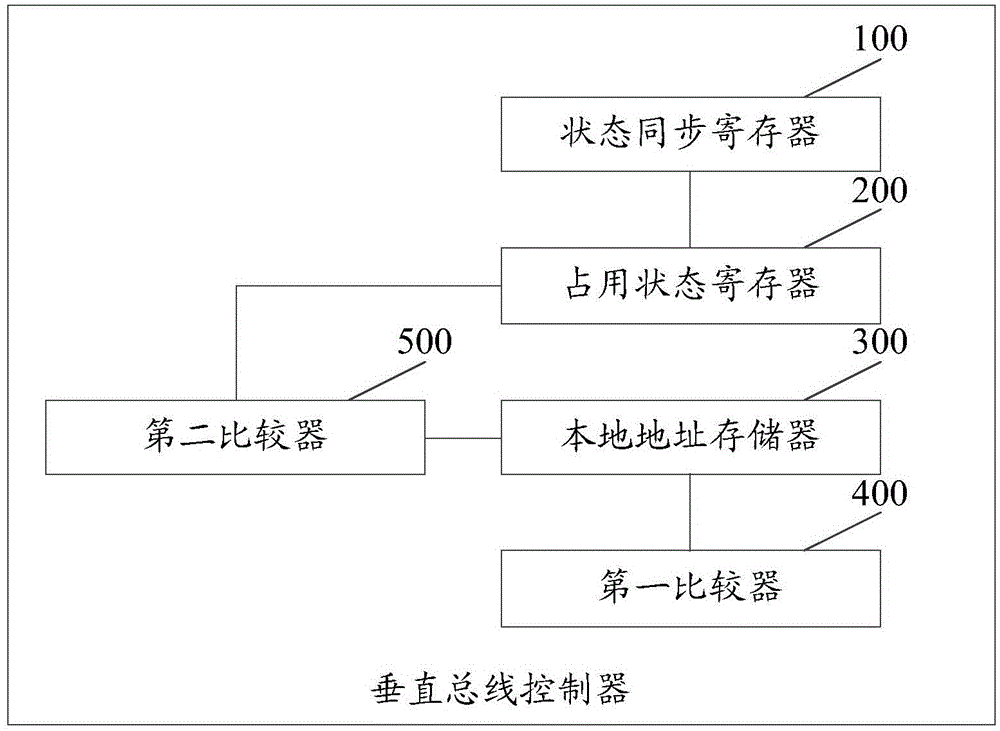

[0032] see figure 1 , a hybrid three-dimensional network on chip provided by an embodiment of the present invention, including:

[0033] A plurality of horizontal sublayers stacked in the vertical direction; wherein, the hor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More