BIST-based open-circuit test method for TSVs in 3D SRAM

An open-circuit test and open-circuit fault technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve problems such as failure to detect memory bank faults and interconnect medium TSV at the same time, increase area overhead, and increase circuit design complexity. , to achieve the effect of high test efficiency, reduced circuit design complexity, and low circuit design complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

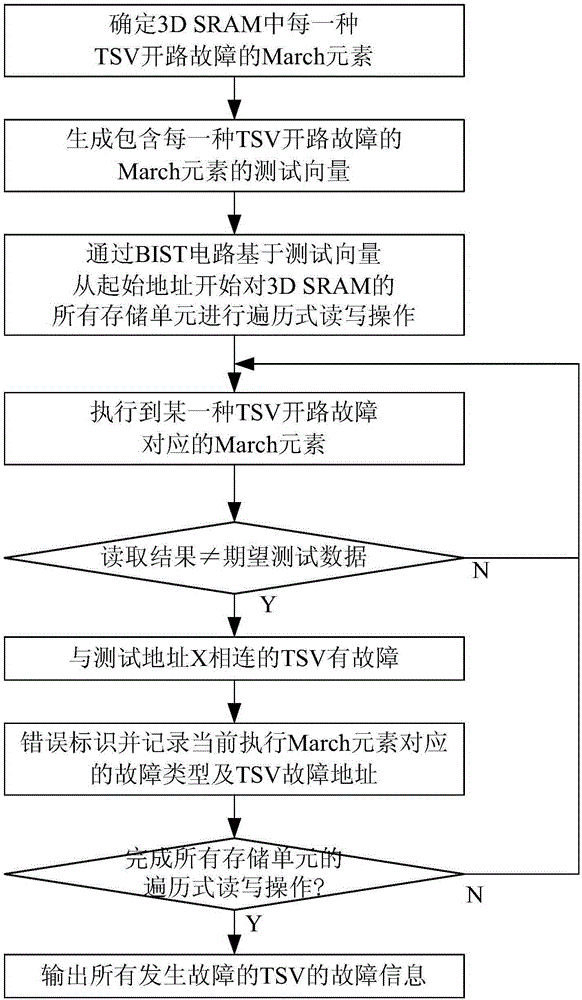

[0029] Such as figure 2 As shown, the steps of the TSV open circuit test method in the BIST-based 3DSRAM of this embodiment include:

[0030] 1) Determine the March element of each TSV open circuit fault in the 3DSRAM, and the March element includes the ascending and descending order traversal mode and read and write operations for traversing the storage unit;

[0031] 2) Generate a test vector that includes the March element corresponding to each TSV open circuit fault;

[0032]3) Through the BIST circuit, based on the test vector, the traversal read and write operations are performed on all storage cells of the 3DSRAM from the start address. When the March element corresponding to a certain TSV open circuit fault is executed, if a certain test address X is read If the result is not the same as the expected test data in the March element, it is determined that the TSV connected to the test address X is faulty, and the faulty TSV is identified as an error and records the fau...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More