Method for increasing display refreshing rate of multi-channel deep memory logic analyzer

A logic analyzer and deep storage technology, applied in the direction of digital output to display devices, etc., can solve the problems of data compression rate, data compression and decompression time-consuming, limited bus and interface speed, etc., to reduce time and reduce data transmission The effect of reducing the amount of time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] Specific embodiments of the present invention will be described below in conjunction with the accompanying drawings, so that those skilled in the art can better understand the present invention. It should be noted that in the following description, when detailed descriptions of known functions and designs may dilute the main content of the present invention, these descriptions will be omitted here.

[0023] In the present embodiment, the multi-channel deep storage logic analyzer of the present invention is a virtual logic analyzer with a PC (personal computer) as the control platform, and the number of channels is 132 (128 data channels, 4 clock channels), the maximum The timing analysis rate is 4GSa / s, the maximum state clock rate is 1.65GSa / s, and the maximum storage depth is 128Mb / channel.

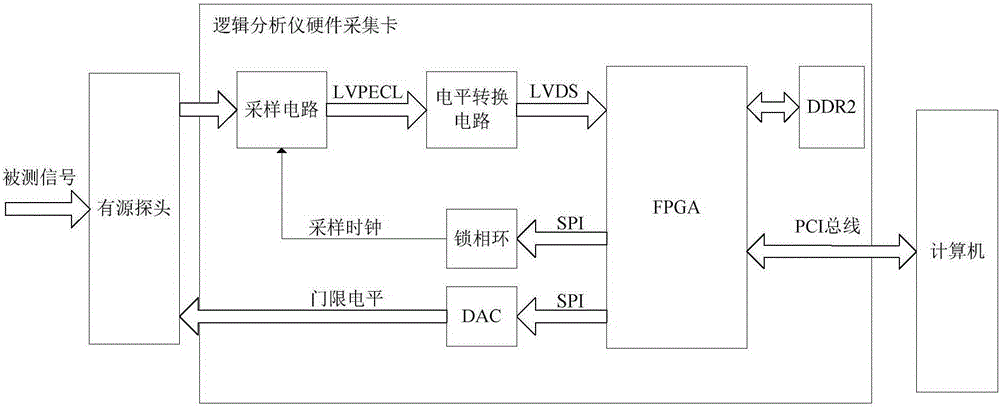

[0024] The hardware design block diagram of the logic analyzer is as follows: figure 1 shown. The measured signal passes through the active probe and is compared with the set t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com