FPGA pin loading reuse device and method

A technology of multiplexing devices and pins, applied in the field of FPGA pin loading multiplexing devices, can solve problems such as waste of pins, and achieve the effect of avoiding waste of pins and re-selection.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Preferred embodiments of the present invention are described below with reference to the accompanying drawings. Those skilled in the art should understand that these embodiments are only used to explain the technical principles of the present invention, and are not intended to limit the protection scope of the present invention.

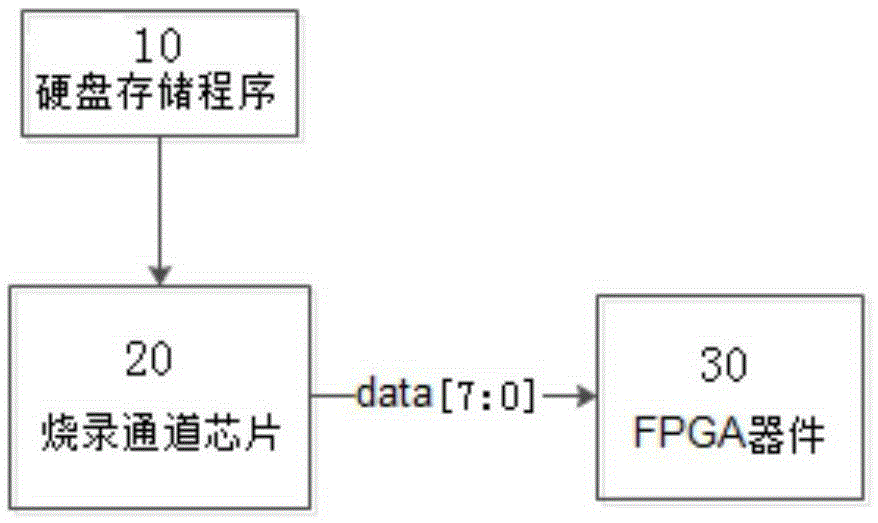

[0018] First refer to figure 1 , which is a structural diagram of an FPGA pin loading device in the prior art. As described in the background technology section, in the FPGA loading method of the prior art, the programming channel chip 20 is used to transmit the program 10 stored inside the hard disk, and the data[7:0] data line is used to transmit the program to the FPGA device 30, In order to complete the data loading or burning. However, as mentioned above, there is a waste of pins in this way.

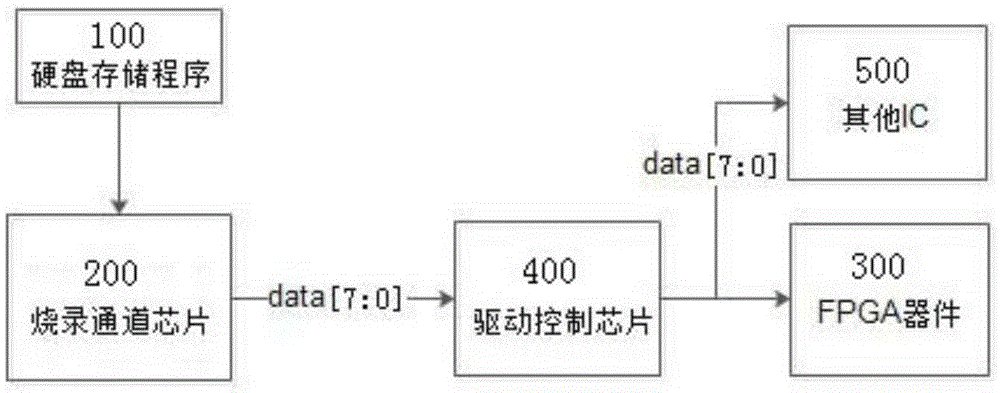

[0019] see below figure 2 , which is a structural diagram of the device for loading and multiplexing FPGA pins according to the present inven...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More