Chip debugging device, debugging method and SOC (System of Chip) chip system

A debugging method and chip technology, applied in the communication field, can solve problems such as inability to debug SOC chip AMBA bus function modules, occupying CPU resources, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The specific implementation manners of the chip debugging device, the debugging method and the SOC chip system provided by the embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

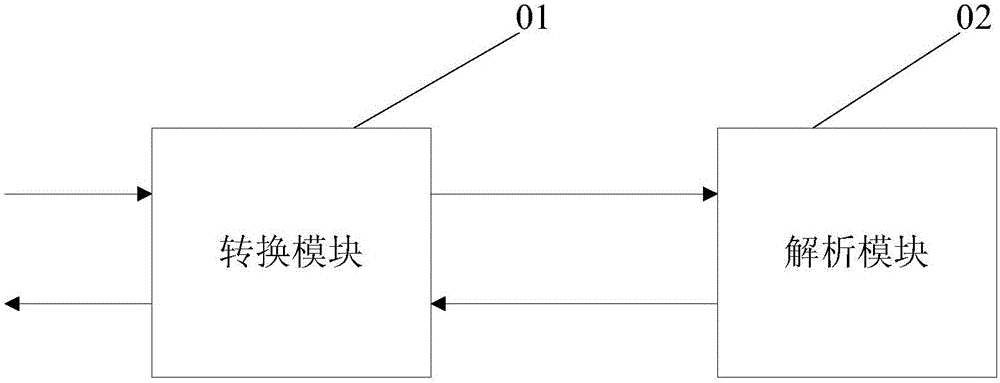

[0042] An embodiment of the present invention provides a chip debugging device for debugging an SOC chip, such as image 3 As shown, the chip debugging device may include: a conversion module 01 and an analysis module 02; wherein, the conversion module 01 is used to convert the external debugging command data received by the SOC chip to the analysis module 02 after serial-to-parallel conversion, and the analysis module 02 The returned data is output after parallel-to-serial conversion; the analysis module 02 is used to analyze the debugging command data converted by the conversion module 01 into an AMBA bus command, and obtain the execution result data of the SOC chip executing the AMBA bus command and return it to the conversion ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More