FPGA (Field Programmable Gate Array) binary file compression and decompression method, and FPGA binary file compression and decompression device

A binary file and compression method technology, applied in the field of FPGA, can solve problems that are not conducive to improving the overall compression ratio and overall compression performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

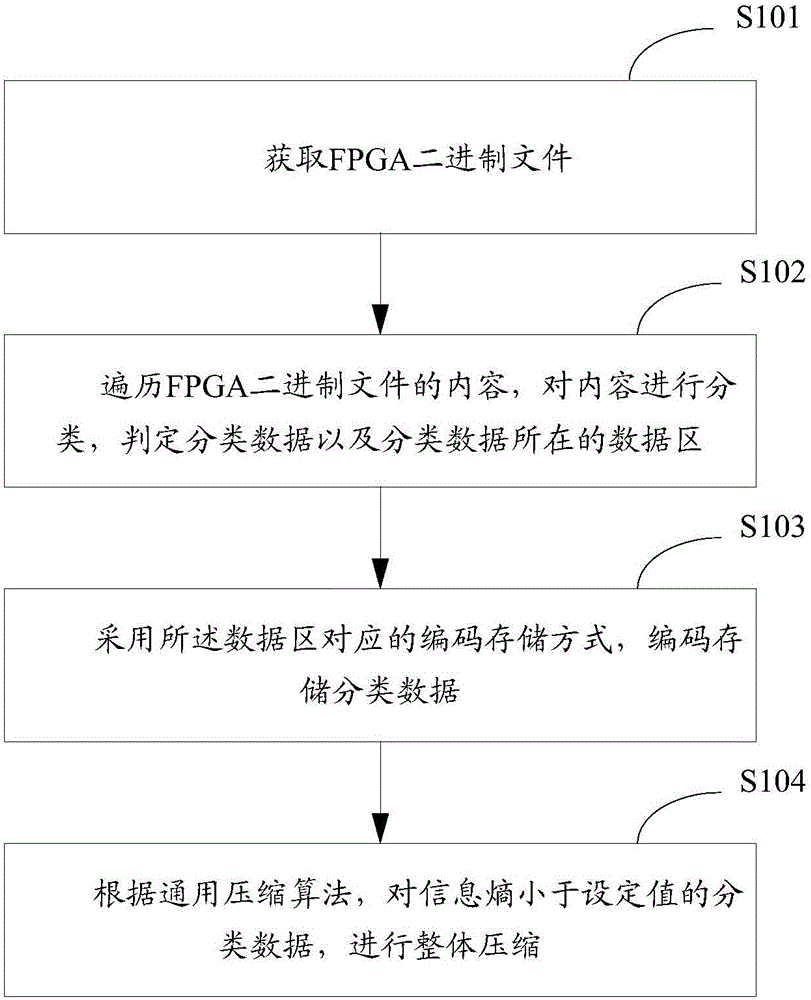

[0037] figure 1 It is the realization flowchart of the FPGA binary file compression method that the embodiment of the present invention provides, is described in detail as follows:

[0038] In step S101, obtain the FPGA binary file;

[0039] In step S102, traverse the content of the FPGA binary file, classify the content, determine the data area where the classified data and the classified data are located;

[0040] Wherein, the data area includes: a fixed data area, a repeated data area, a sparse data area and a random data area;

[0041] The fixed data area is: the data area shared by each FPGA binary file;

[0042] The repeated data area is: a data area that stores all 0s or all 1s;

[0043] The sparse data area is: a data area storing four-byte data;

[0044] The random data area is: a data area for storing random data.

[0045] In step S103, the coded storage method corresponding to the data area is used to encode and store the classified data;

[0046] In step S104...

Embodiment 2

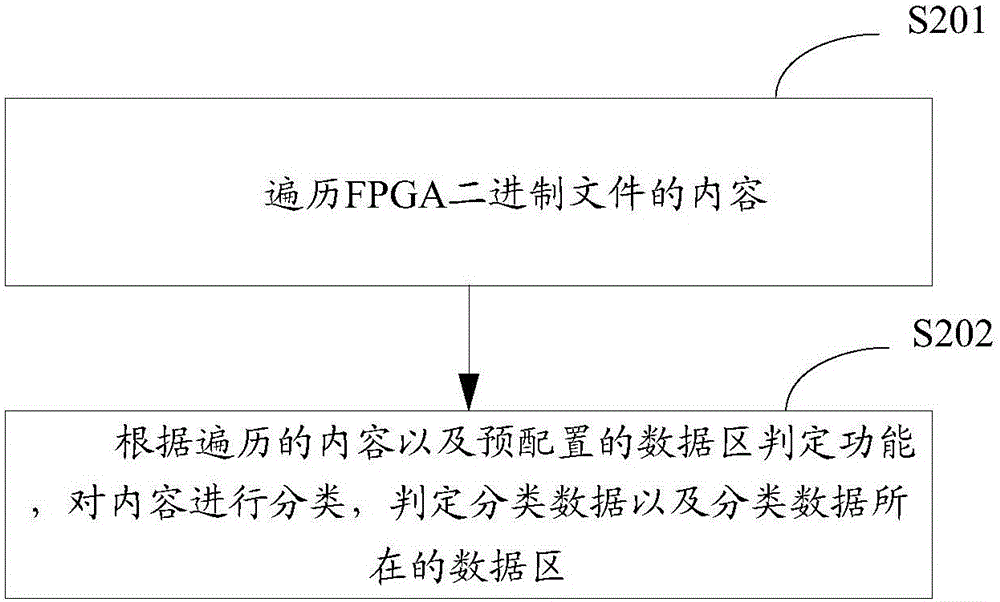

[0064] figure 2 It is the realization flowchart of the FPGA binary file compression method step S102 that the embodiment of the present invention provides, and is described in detail as follows:

[0065] In step S201, traverse the content of the FPGA binary file;

[0066] In step S202, according to the traversed content and the pre-configured data area determination function, the content is classified, and the classified data and the data area where the classified data is located are determined.

Embodiment 3

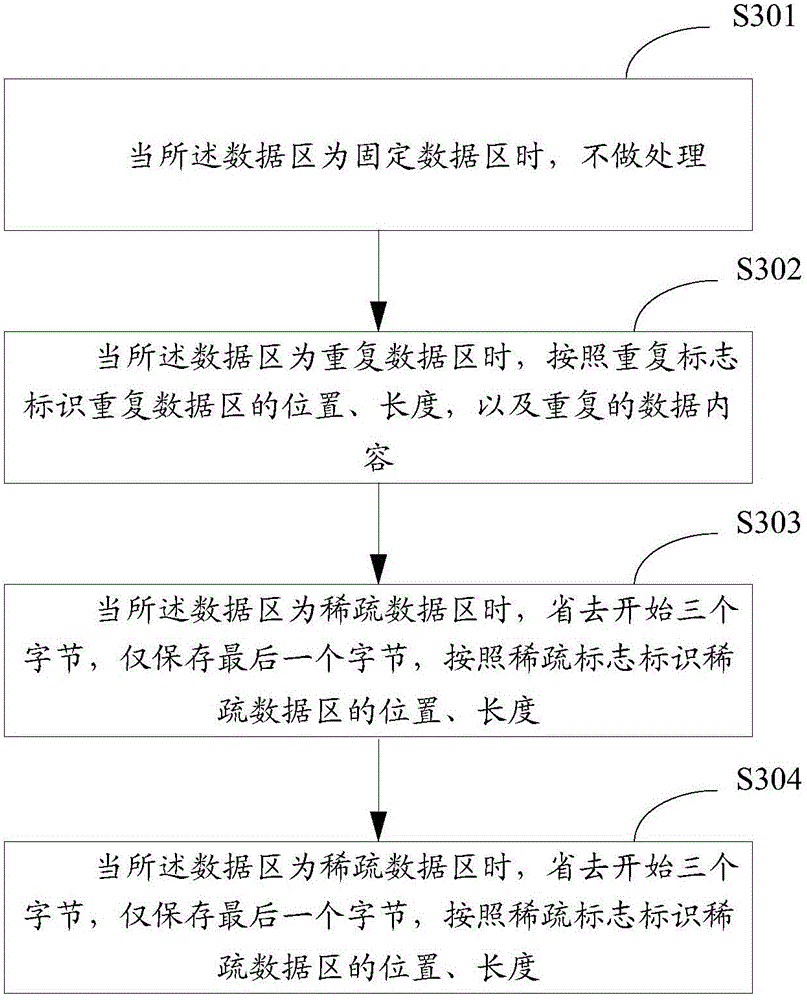

[0068] The implementation flowchart of the configuration data area judgment function described in the embodiment of the present invention is described in detail as follows:

[0069] Configuring the data area judgment function, the configuration data area judgment function specifically includes:

[0070] Configure the judgment function of the repeated data area, sparse data area, and random data area:

[0071] The data area in which data is repeated in units of single byte, data in unit of double byte, and data in unit of four bytes, and which lasts for the first set range is determined as a repeated data area.

[0072] In units of four bytes, the high-order 3 bytes remain unchanged, and the data of the fourth byte changes, and the area with a large continuous range is judged as a sparse data area;

[0073] The area other than the above two without regularity, or the second set range of repeated data and sparse data continuous range, is determined as a random data area;

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More