An Array Layout Generation Method for Full Board Layout Resistor and Capacitance Extraction

A resistance-capacitance, layout technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problem that the speed is difficult to meet the design requirements, the accurate calculation of the resistance and capacitance of the full board layout is time-consuming, and the array features no longer exist obviously, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example

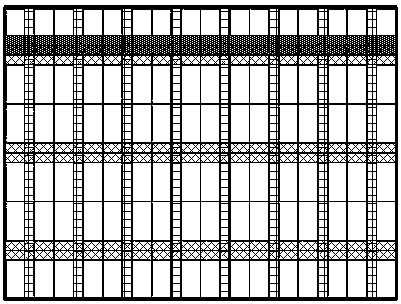

[0017] Combined with a specific example method, the operation process steps are as follows:

[0018] 1) Open a hierarchical layout;

[0019] 2) Select the reusable unit size w*h, and get the lower left corner of the array (x, y);

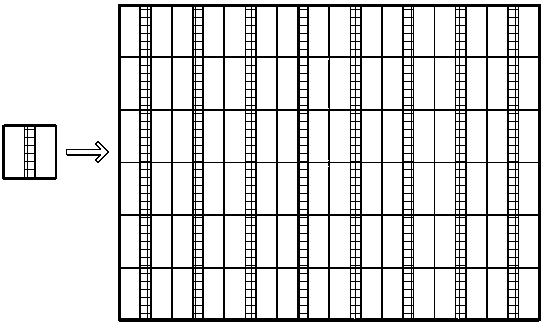

[0020] 3) Starting from (x, y), from left to right, from bottom to top, take an area of size w*h, divide the layout, obtain candidate reusable graphics unit sequences, and perform each area Mark the corresponding serial number;

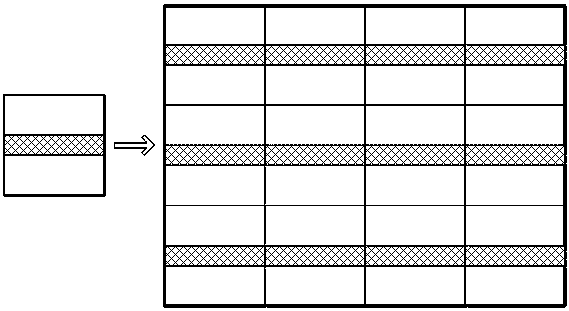

[0021] 4) Generate a new reusable array unit for each reusable graphics unit;

[0022] 5) Group the regions according to the region labels, and generate array instances according to the groups;

[0023] 6) A new layout is composed of new array instances.

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap