Array-based full-panel layout capacitance quick extraction method

An extraction method and capacitor technology, which can be used in electrical digital data processing, special data processing applications, instruments, etc., and can solve problems such as losing array rules.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example

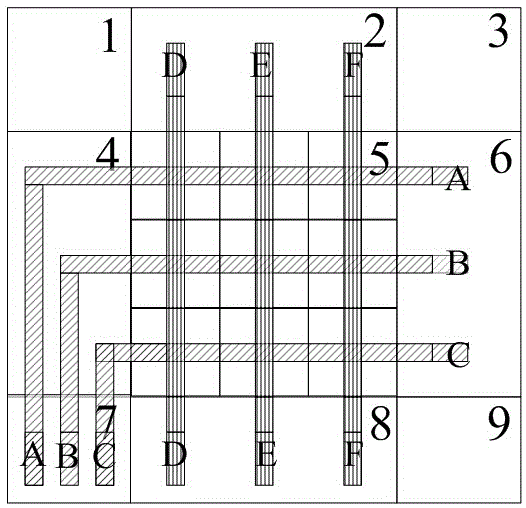

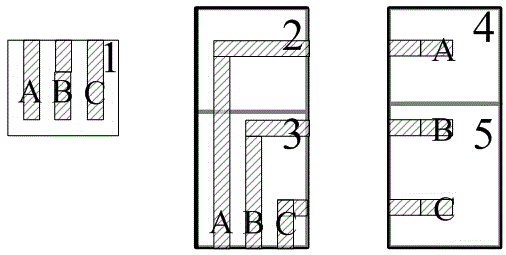

[0016] Combined with a specific instance method, the operation process steps are as follows:

[0017] 1) Open a hierarchical layout with a simple structure;

[0018] 2) Select the wire mesh to be extracted;

[0019] 3) For the proposed wire net, find the non-array area and the array area that have passed through, and record the index in the array;

[0020] 4) For the non-array area, divide and extract the capacitance of the effective area, and record the intermediate results;

[0021] 5) For the array area, perform capacitance extraction for each valid array unit, and record the intermediate results;

[0022] 6) Combine the final result, that is, combine the capacitance value of the array area and the capacitance value converted from the internal capacitance value of the array unit to the corresponding external wire net.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More