Apparatus and methods for transient overstress protection in compound semiconductor circuit applications

A semiconductor and compound technology, applied in the field of compound semiconductor protection devices, can solve problems such as surface charge accumulation, increased circuit temperature, and junction damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The following detailed description of certain embodiments presents various descriptions of specific embodiments of the invention. However, the invention can be embodied in many different ways as defined and covered by the claims. In this specification, reference is made to the drawings, in which like reference numbers indicate identical or functionally similar elements.

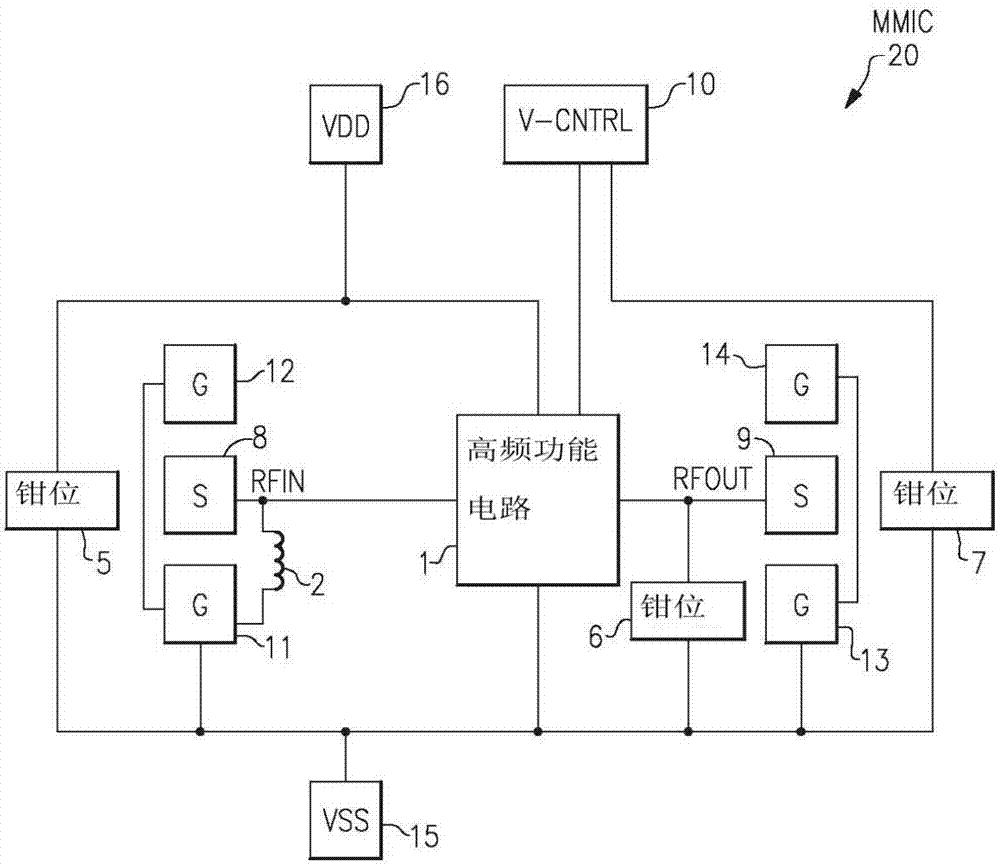

[0021] To help ensure that electronic systems are reliable, manufacturers can test electronic systems under defined stress conditions, which can be described by standards set by various organizations, such as the Joint Electron Device Engineering Council (JEDEC), the International Electrotechnical Society Committee ( IEC) and / or the International Organization for Standardization (ISO). Standards can cover a wide range of transient overstress events, including electrostatic discharge (ESD) events and / or electrical overstress (EOS) events. For example, a monolithic microwave integrated circuit (MMIC) m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More