Stress-tuned planar lighting circuit and method

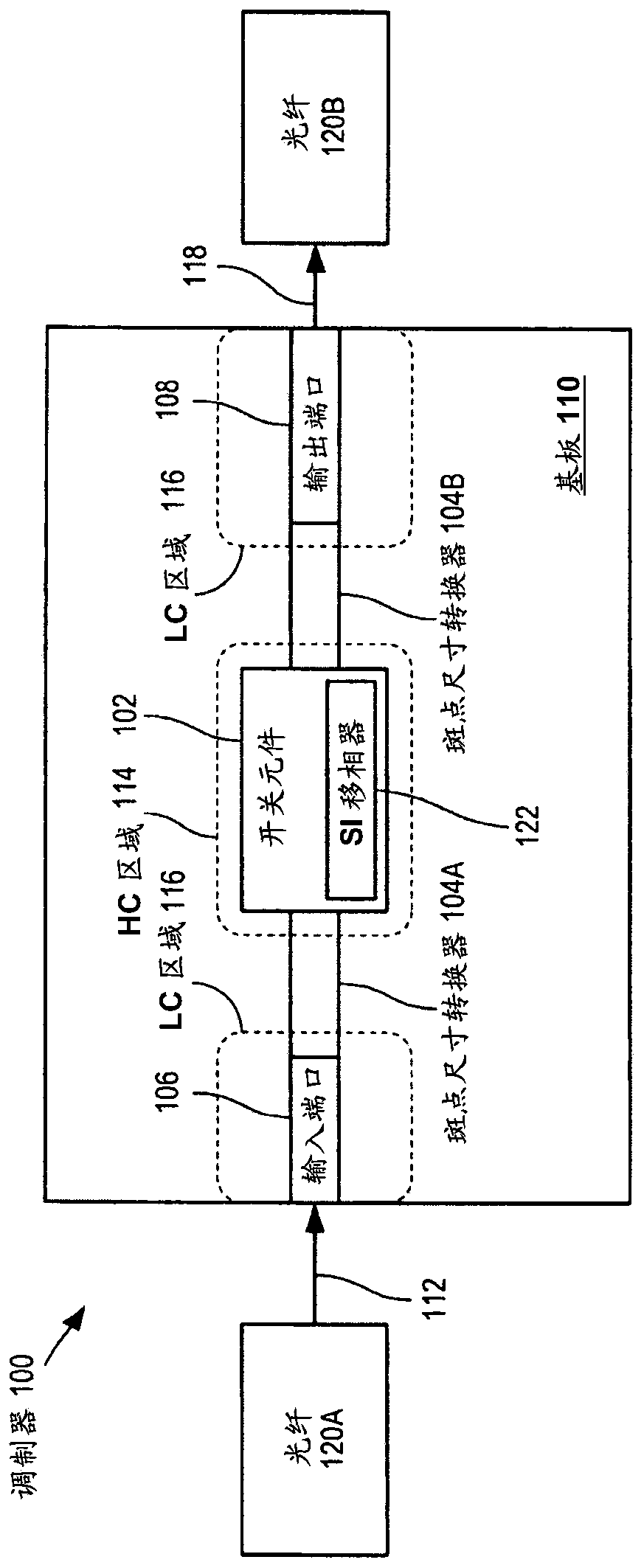

A circuit, plane light wave technology, applied in the direction of instruments, optical waveguides, light guides, etc., can solve the problems of a large amount of chip occupied area, high cost per chip, etc., and achieve the effect of cheap PLC chips, low light loss, and improved mechanical coupling.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] For the purposes of this specification, including the appended claims, the terms "disposed on" or "formed on" are defined as "present on" an underlying material or layer, or in direct physical contact therewith or by means of one or more middle layer. For example, if a material is described as being "deployed (or grown)" on a substrate, this can mean that either (1) the material is in intimate contact with the substrate; or (2) the material is in contact with one or more layers already present on the substrate touch. It should be noted that a conformal layer is considered to be deployed on each surface of the structure with which it conforms.

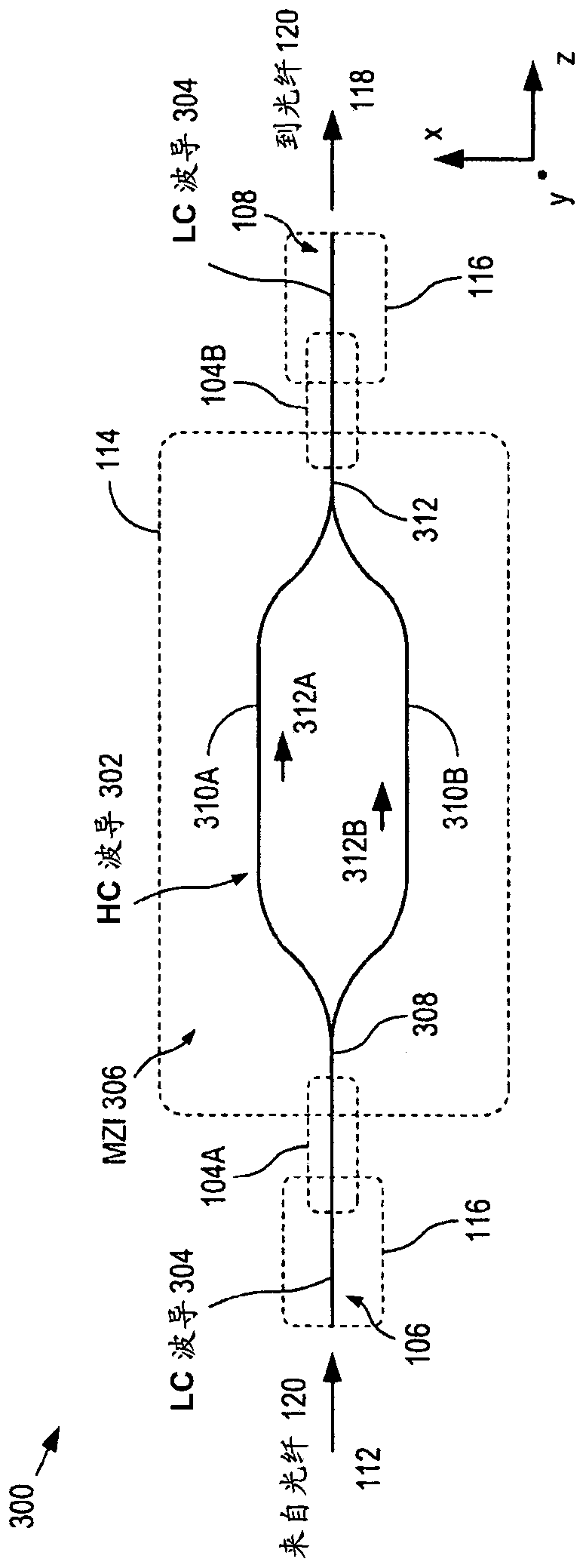

[0051] This case is a continuation-in-part of US Patent Application Serial No. 14 / 051715, entitled "Surface Waveguide Having a Tapered Region and Method of Forming" (hereinafter "parent case"), which is hereby incorporated by reference in its entirety. As discussed in the parent case, the use of waveguide taper-based spot size ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More