Chip top protection layer integrity detection device

A technology of integrity detection and protection layer, which is applied in the direction of measuring devices, measuring electricity, and measuring electrical variables, etc., can solve problems such as threats to the information security of integrated circuits, achieve high detection accuracy, and achieve the effect of integrity detection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

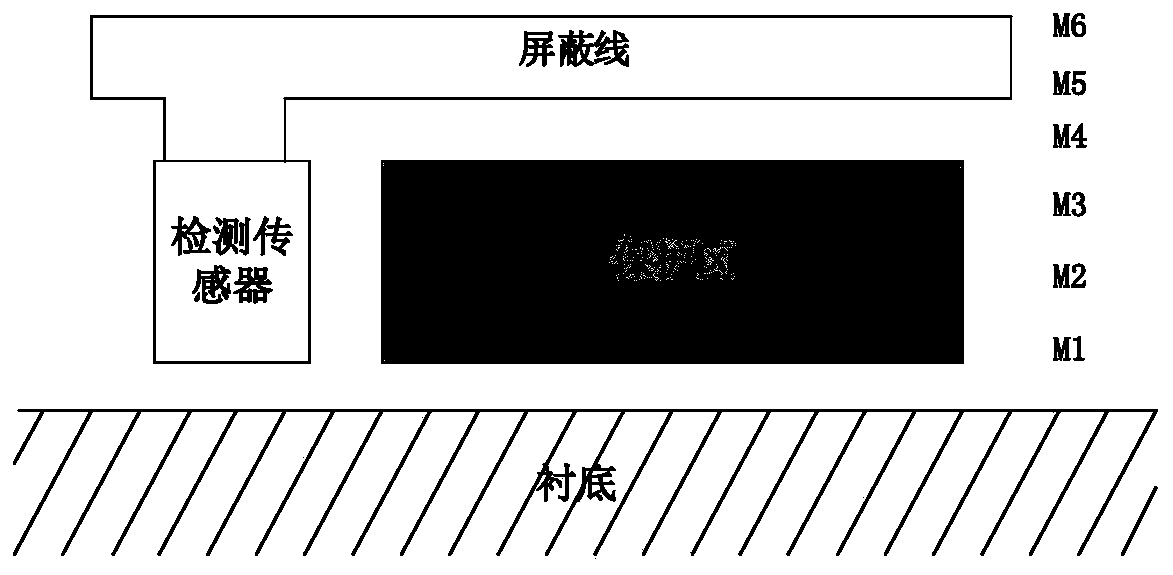

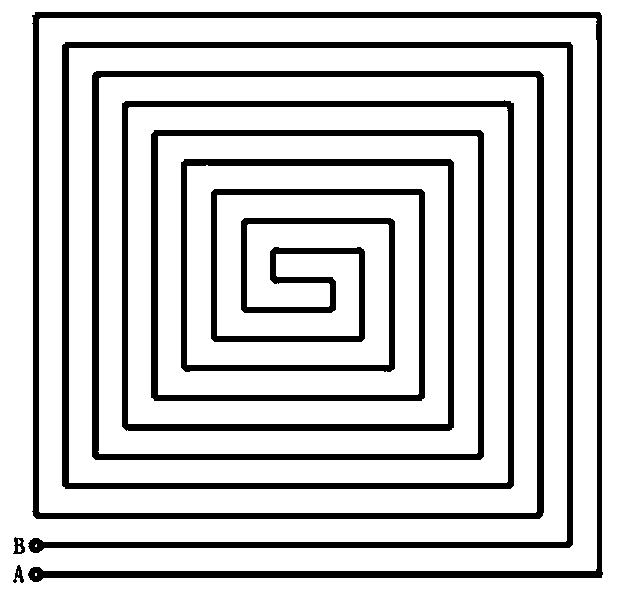

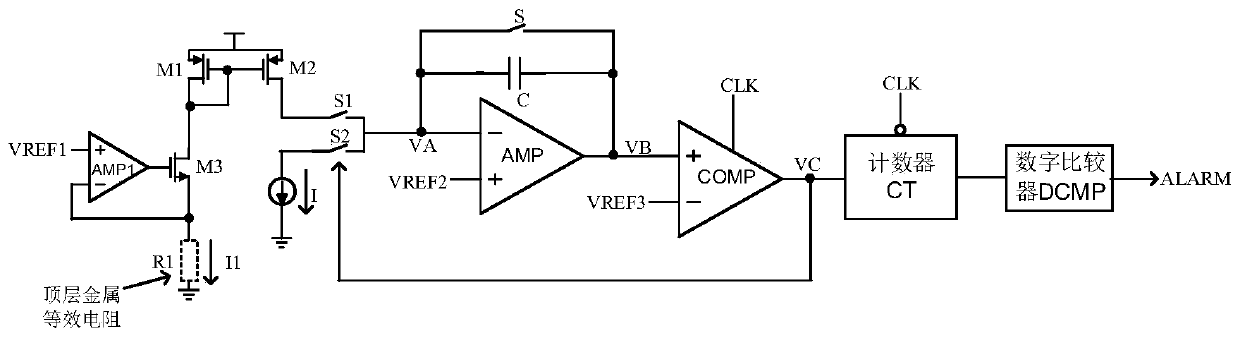

[0018] The present invention proposes a method for detecting the integrity of the top-layer metal protection layer based on a sigma-delta (Σ-Δ) modulator, the detection method is applicable to the top-layer metal protection layer of any graphic topological structure, and the present invention will take the spiral topological structure as the As an example, the integrity detection method is described. The spiral topology can be replaced by any other structure.

[0019] Such as figure 2 Shown is the wiring diagram of the top metal protection layer of the spiral topology. This protective layer is formed by metal wires AB. The metal line AB is composed of the top layer metal, and A and B are two ports respectively. The total resistance value of the metal wire AB is determined by its square resistance R, the width W of the metal wire, and the total length L of the metal wire. The total resistance value R AB =RL / W. Once the metal line AB is short-circuited from somewhere in th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More