Line edge roughness improvement with photon-assisted plasma process

A line edge roughness and plasma technology, applied in semiconductor/solid-state device manufacturing, discharge tubes, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

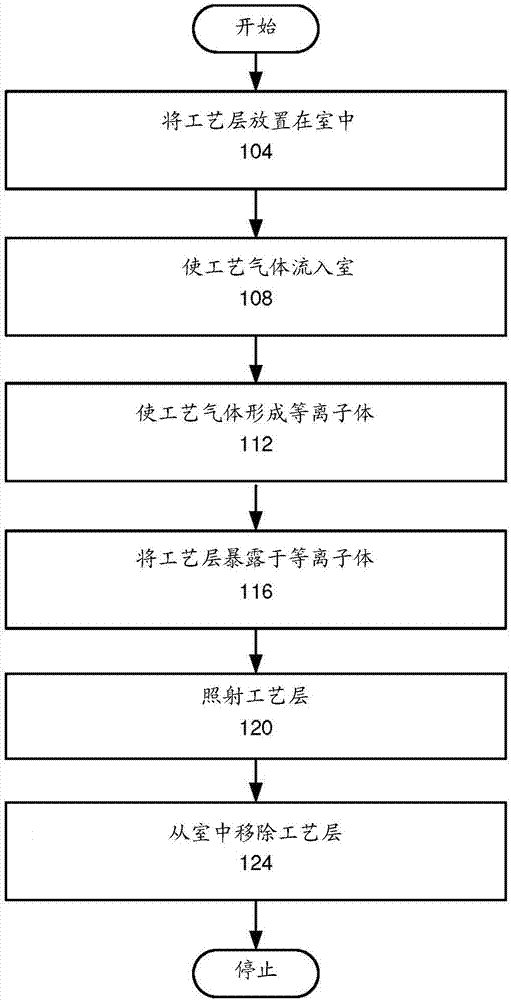

Method used

Image

Examples

Embodiment

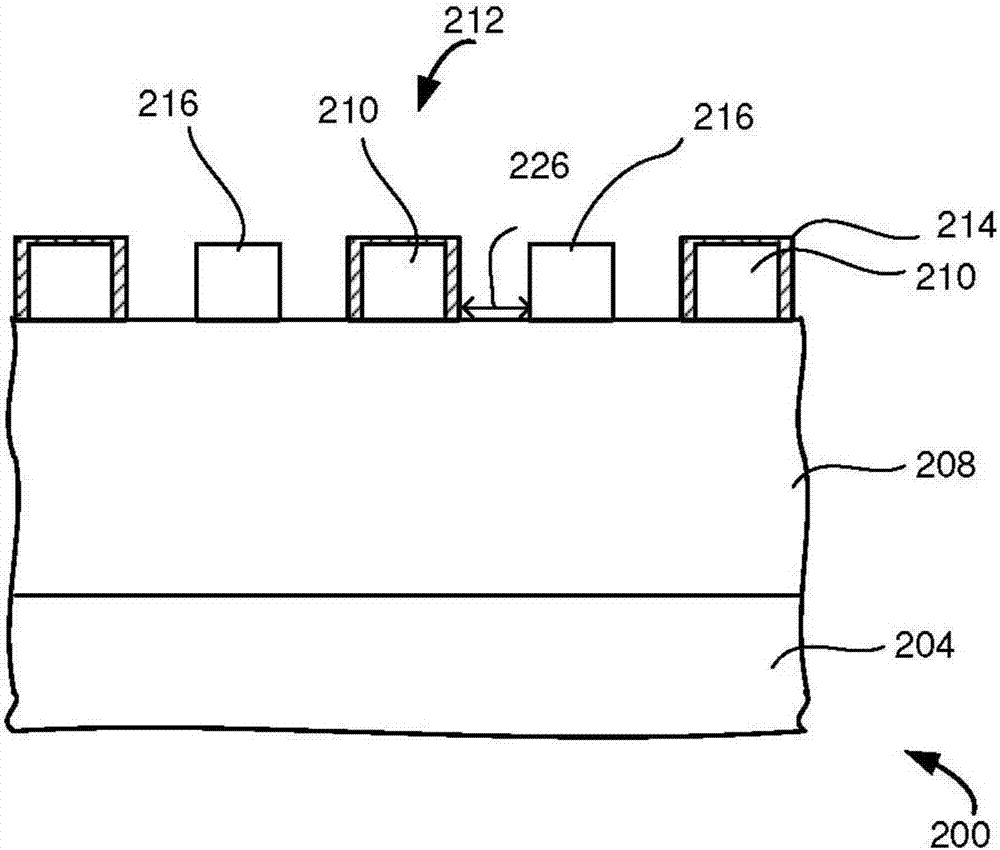

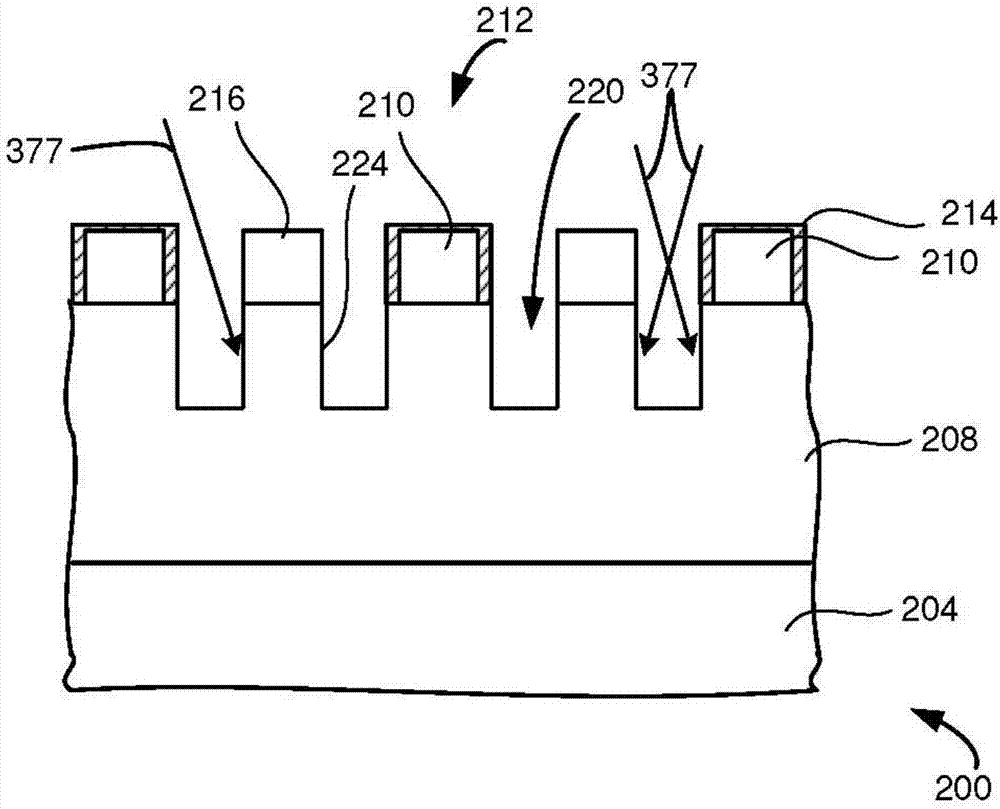

[0047] In a preferred embodiment, a substrate is provided having a silicon oxide-containing etch layer disposed beneath a double patterning mask. Double patterning masks are known in the art and include various processes for obtaining masks of higher resolution than a single mask patterning process can provide, enabling smaller devices and higher density. One example of a double patterning mask is described in Romano et al., US Patent No. 8,282,847, entitled "Photoresist Double Patterning," issued October 9, 2012, which is incorporated herein by reference for all purposes. The double patterning mask can be formed using self-aligned double patterning with spacer deposition. These processes are known in the art. An example of such a process is described in U.S. Patent No. 7,977,242 to Sadjadi et al., entitled "Double Mask Self-Aligned Patterning Technology (SADPT) Process," issued July 12, 2011, which is incorporated by reference in its entirety This article is for all purpos...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More