Symbol table-based programmable logic debugging method and system

A programming logic and symbol table technology, applied in the field of programmable logic debugging, can solve the problems of only viewing, running state information cannot be dynamically generated, etc., and achieve the effect of improving the means of acquisition and analysis

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

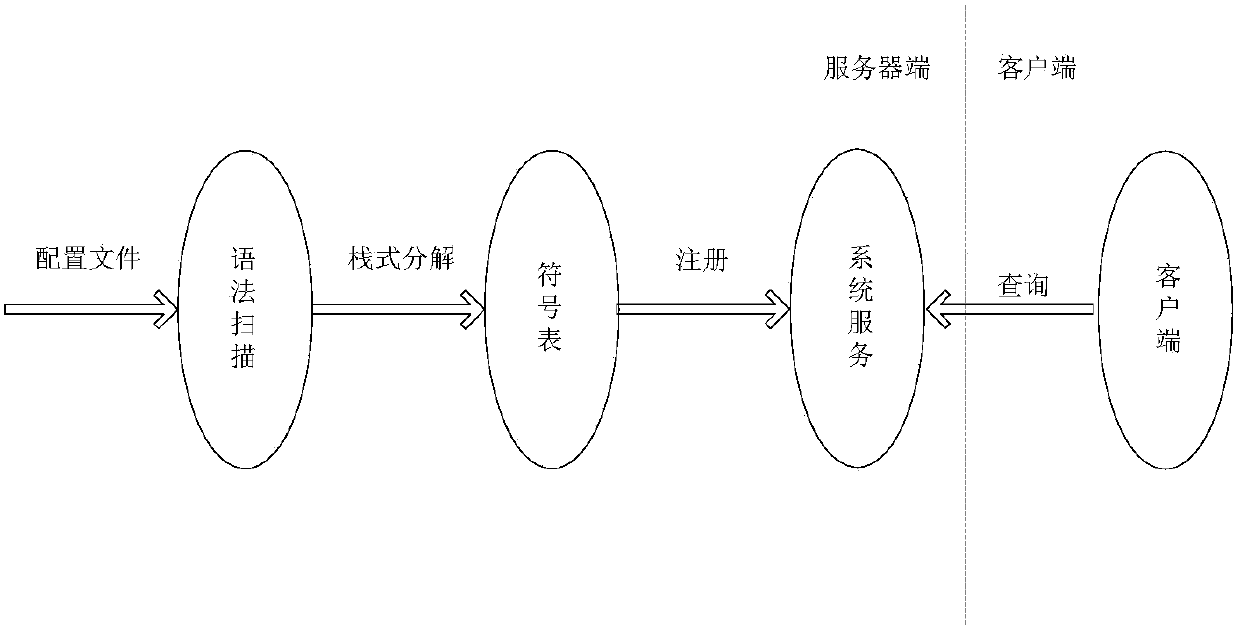

[0022] A specific method and system for debugging programmable logic based on a symbol table will be used to illustrate the specific implementation method of the present invention below. data flow see figure 1 , the specific implementation methods include:

[0023] 1. Syntax scanning:

[0024] (1) Build logic diagrams in a graphical way, with icons including four arithmetic operations, logical operations, conditional statements, jump statements, loop statements, function blocks, etc., to generate configuration files for logical function descriptions;

[0025] (2) The operating system side loads the configuration file into the shared memory, and the processor side reads the configuration information from the shared memory, checks the file CRC, and if the check is inconsistent, the device fails to start;

[0026] (3) Create summary table items, input table items, output table items, and formula table items in sequence;

[0027] 2. Symbol table:

[0028] (1) When scanning the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More