Multi-core cache WCET analysis method supporting instruction prefetching

A technology of instruction prefetching and analysis methods, which is applied in reliability/availability analysis, instrumentation, electrical digital data processing, etc., and can solve problems such as conservative and complex task WCET estimation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0101] This embodiment describes in detail the execution process of the present invention when it is implemented in the case of instruction prefetching.

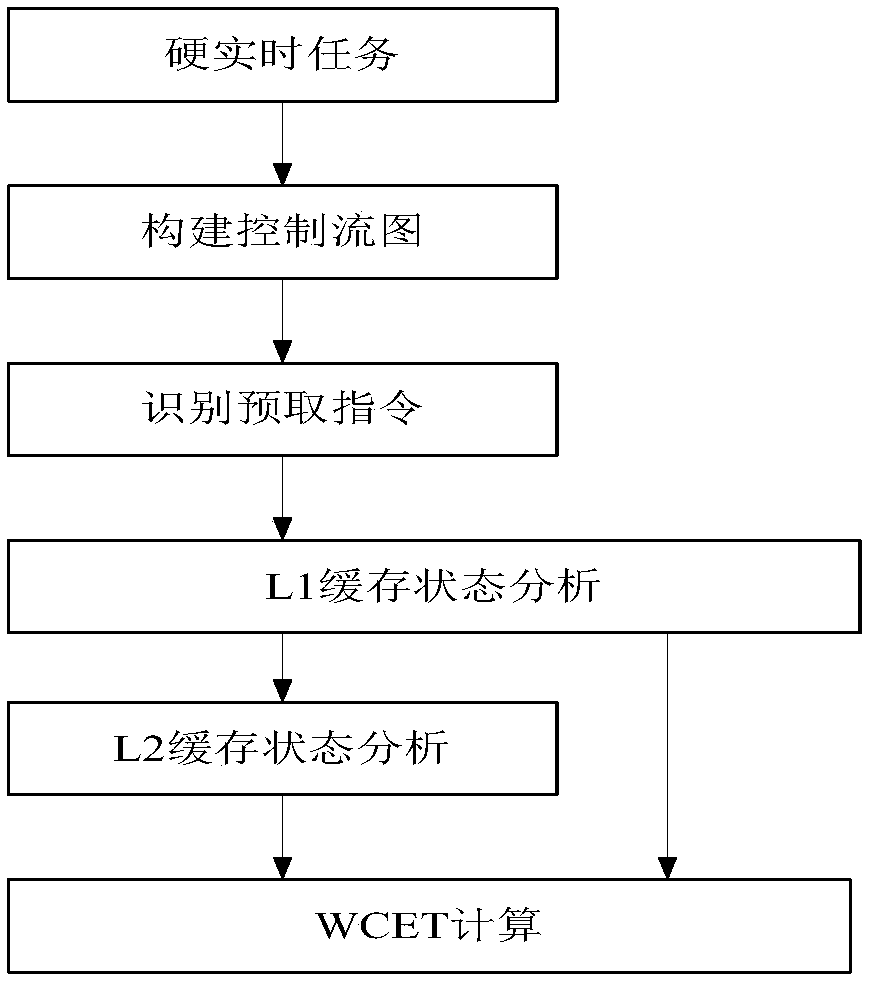

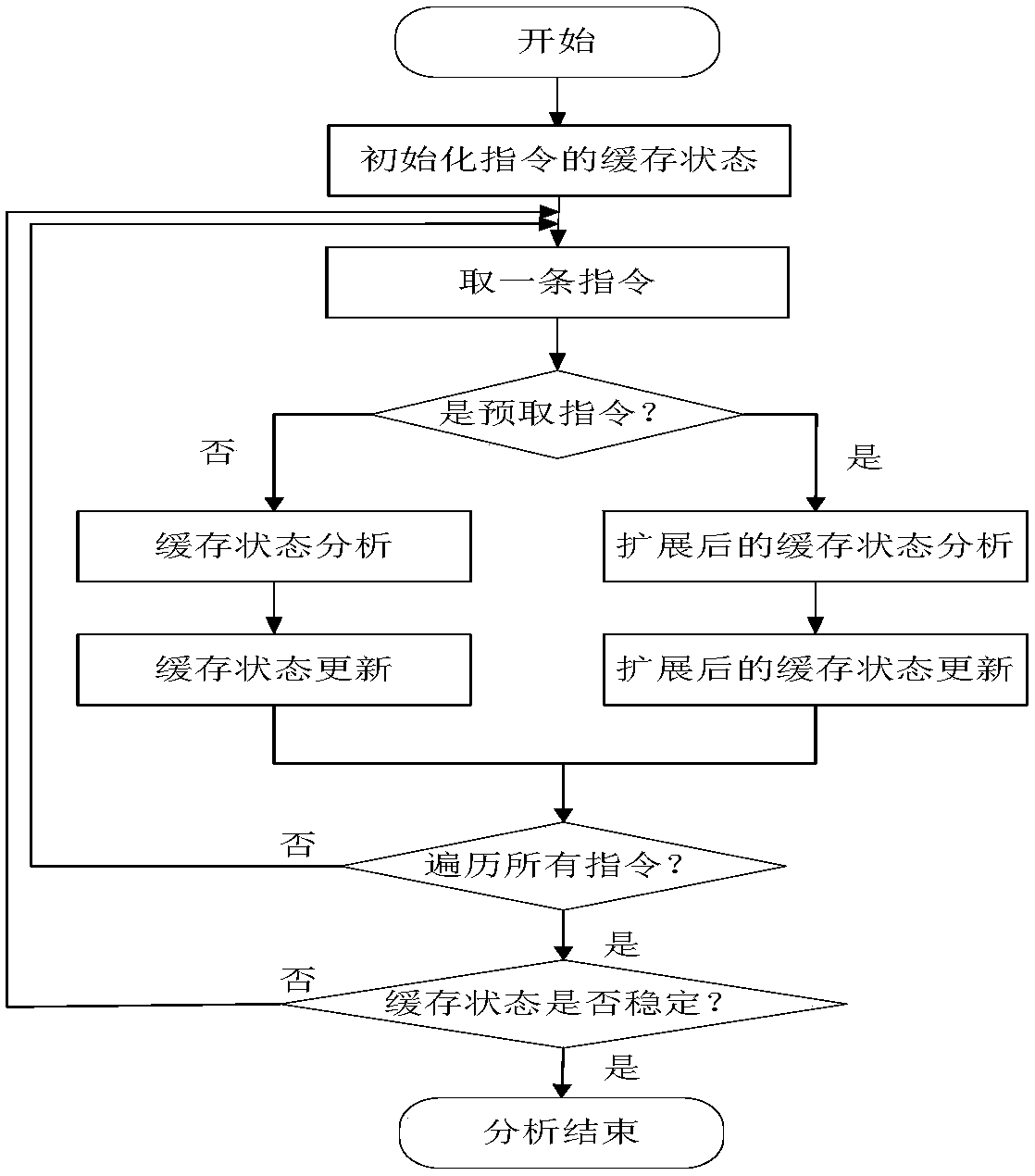

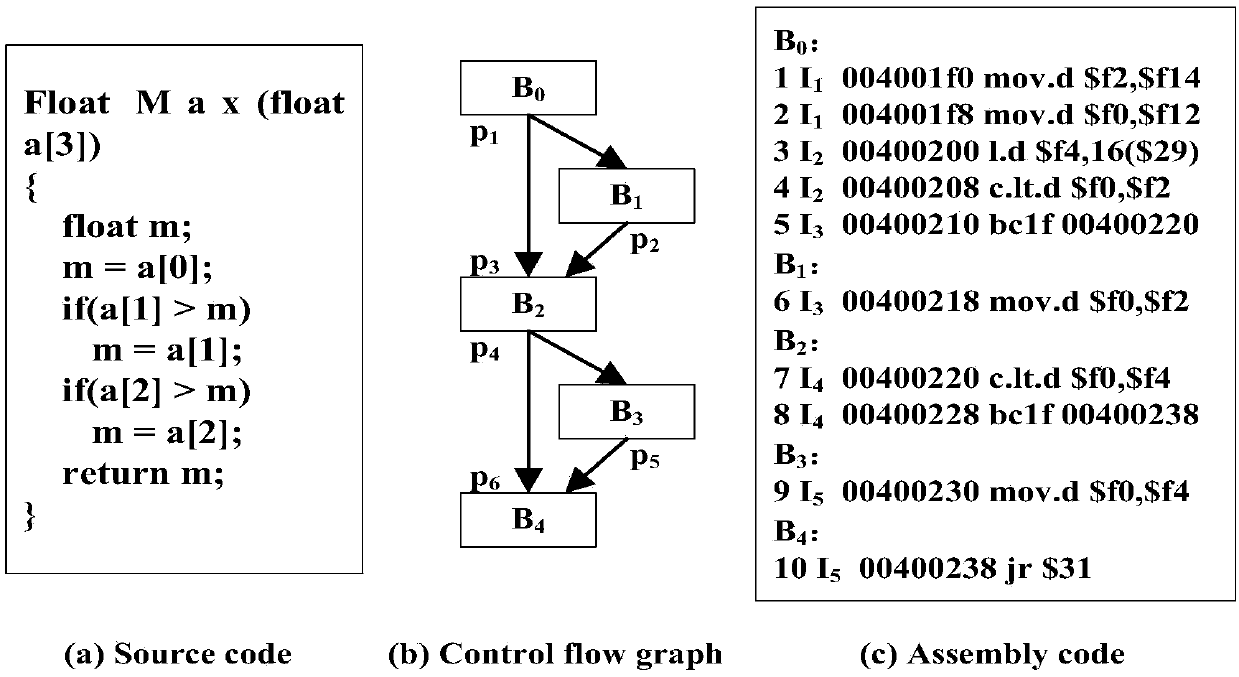

[0102] figure 1 It is a flow chart of the WCET analysis method of the present invention, and each block in the figure represents an operation step of the present invention. figure 2 It is a flow chart of the basic block analysis in the present invention, and the L1 cache state analysis and the L2 cache state analysis of the basic block in the task are all adopted figure 2 in the steps. image 3 (a-c) describe part of the source code of a program, and its corresponding CFG and assembly code obtained through reverse analysis. image 3 A node in (b) represents the number of the basic block, for example, B0 means that the number of the basic block is 0. for image 3 (c) The PISA assembly code based on the Simplescalar simulator in the basic block, the number at the top of each line is the instruction number (1-10), and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More